#### <atomic.h> weapons

Paolo Bonzini Red Hat, Inc. KVM Forum 2016

## The real things

- Herb Sutter's talks

- atomic<> Weapons: The C++ Memory Model and Modern Hardware

- Lock-Free Programming (or, Juggling Razor Blades)

- The C11 and C++11 standards

- N2429: Concurrency memory model

- N2480: A Less Formal Explanation of the Proposed C++ Concurrency Memory Model

# Outline

- Who ordered atomics?

- Compilers and the need for a memory model

- qemu/atomic.h: portable atomics in QEMU

- Future work

# Outline

- Who ordered atomics?

- Compilers and the need for a memory model

- qemu/atomic.h: portable atomics in QEMU

- Future work

## Why atomics?

- Coarse locks are simple, but scale badly

- Finer-grained locks introduce problems too

- Not easily composable ("leaf" locks are fine, nesting can result in deadlocks)

- Taking a lock many times is slow

- Like extremely fine-grained locks, but faster

## What do atomics provide?

- Ordering of reads and writes

- Atomic compare-and-swap, like this:

Everything else can be built on top of these

#### When to use atomics?

- When threads communicate at well-defined points

- Example: ring buffers

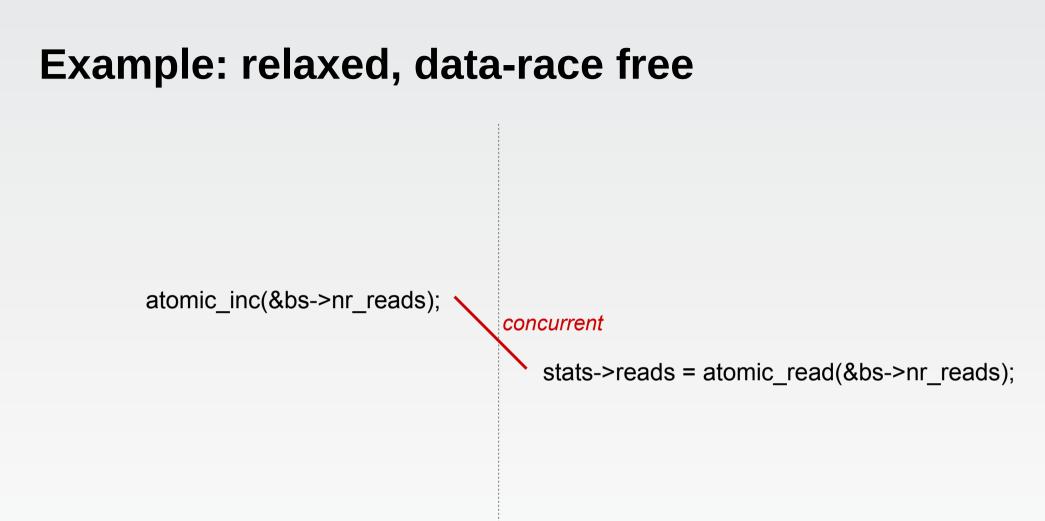

- When consistency requirements are minimal

- Example: accumulating statistics

- When complexity is easily abstracted

- Example: synchronization primitives, data structures

- For the fast path only

- Example: RCU, seqlock, pthread\_once

# Outline

- Who ordered atomics?

- Compilers and the need for a memory model

- qemu/atomic.h: portable atomics in QEMU

- Future work

## **Compiler writers are your friends**

int i; char \*a; a[i+4] = 1;

```

int n, *a;

for (int i = 0; i <= n; i++)

a[i] = 0;

```

```

int **a;

for (int i = 0; i < M; i++)

for (int j = 0; j < N; j++)

a[i][j] = 42;

```

# Compiler writers are your friends (but they need some help too)

a[i][i] = 42;

assumes no overflow in i+4! int i; char \*a; movb \$1, 4(%rsi,%rdi) a[i+4] = 1;infinite loop if n == INT MAX? int n, \*a; int n, \*a; for (int i = 0; i <= n; i++) for (int \*end = &a[n]; a <= end; ) a[i] = 0;\*a++ = 0; int \*\*a; int \*\*a; for (int i = 0; i < M; i++) for (int i = 0; i < M; i++) for (int j = 0; j < N; j++) for (int **\*row = a[i]**, j = 0; j < N; j++)

> what if a[i][j] overwrites a[i]?

row[i] = 42;

## The hard truth about undefined behavior

- You don't want the compiler to execute the program you wrote

- Most undefined behavior is obvious

- Some undefined behavior makes sense, but is hard to reason about

- Some undefined behavior seems to make no sense, but really *should* be left undefined

## Sequential consistency (Lamport, 1979)

- The result of any execution is the same as if reads and writes occurred in some total order

- Operations from each individual processor are ordered the same as they appear in the program

static int a; int x = ++a; f(); return x;

static int a; f(); return ++a;

## Sequential consistency (Lamport, 1979)

- The result of any execution is the same as if reads and writes occurred in some total order

- Operations from each individual processor are ordered the same as they appear in the program

long long x = 0; // thread 1 x = -1;

// thread 2

printf("%lld", x);

## Sequential consistency (Lamport, 1979)

- The result of any execution is the same as if reads and writes occurred in some total order

- Operations from each individual processor are ordered the same as they appear in the program

#### The C/C++ approach

- You also don't want the processor to execute the program that you wrote

- Processor "optimizations" can be described by rearranging loads and stores in the source code

- Can the same tools let you reason on both compiler- and processor-level transformations?

- Union, pointers, casts: with great power comes great responsibility

#### The C/C++ approach

- Programs must be race-free

- The standard precisely defines data races

- The semantics of data races are left undefined

- If the program is "compiler-correct", it's also "processor-correct"

- If the program is correct, its executions are all sequentially consistent

- ... unless you turn on the guru switch

## Happens-before (Lamport, 1978)

- Captures causal dependencies between events

- For any two events e1 and e2, only one is true:

- $e1 \rightarrow e2$  (e1 happens before e2)

- $e2 \rightarrow e1$  (e2 happens before e1)

- e1 || e2 (e1 is concurrent with e2)

- Data race: Concurrent accesses to the same memory location, at least one a write, at least one non-atomic

#### More precisely...

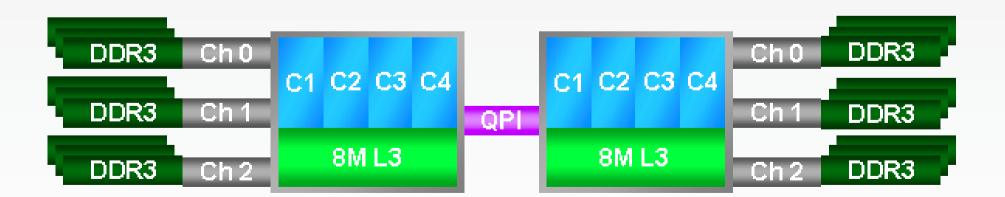

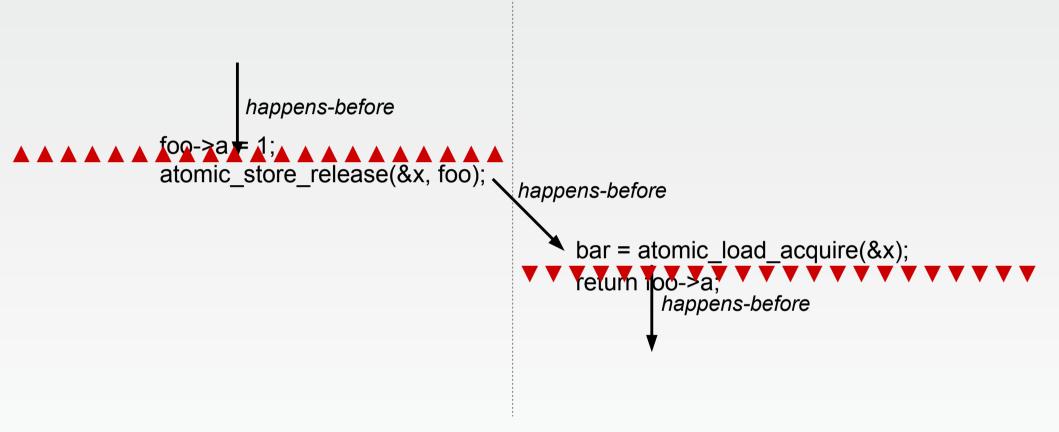

- If a thread's "load-acquire" sees a "store-release" from another thread, the store synchronizes with the load

- The store then happens before the load

- Within a single thread, program order provides the happens-before relation

- Happens-before is transitive

- Everything before the store-release happens before everything after the load-acquire

#### **Example: data-race free, correct**

- No concurrent accesses

- No data race!

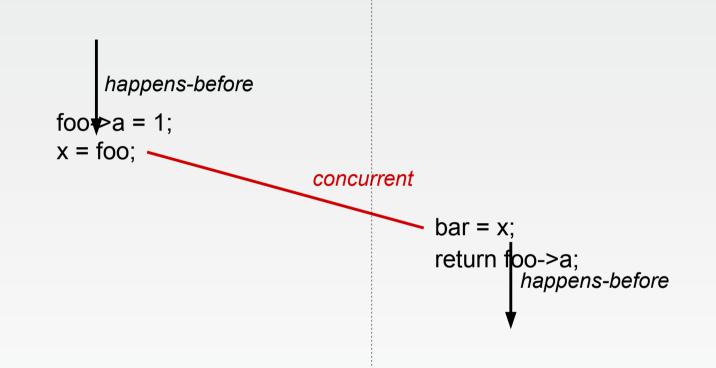

## **Example: data-race, undefined behavior (I)**

- Concurrent non-atomic accesses, one a write

- Data race → undefined behavior!

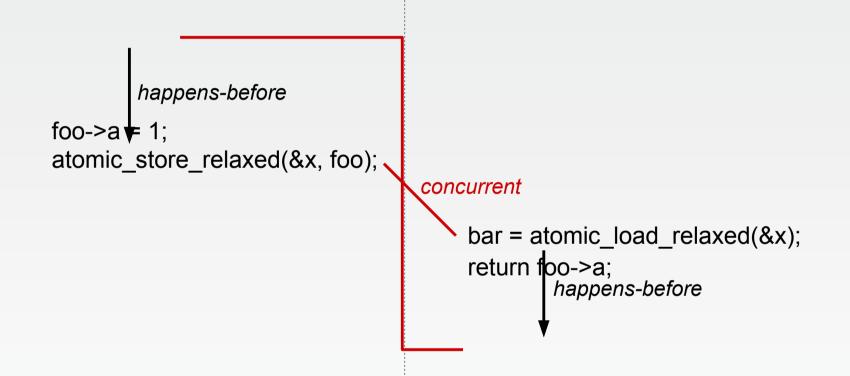

## **Example: data-race, undefined behavior (II)**

- Concurrent atomatoanciceasees, seese, anveritewrite

- Determined behavior!

- Concurrent atomic accesses, one a write

- No data race! But not sequentially consistent

#### Acquire/release as optimization barriers

## Acquire and release operations

- Acquire:

- pthread\_mutex\_lock

- pthread\_join

- pthread\_once

- pthread\_cond\_wait

- Release:

- pthread\_mutex\_unlock

- pthread\_create

- pthread\_once (first time)

- pthread\_cond\_signal

- pthread\_cond\_broadcast

- pthread\_cond\_wait

#### Why atomics work

- Atomics let threads access mutable shared data without causing data races

- Atomics define happens-before across threads

- Programs that correctly use locks to prevent all data races behave as sequentially consistent

- Same for programs that do not use so-called "relaxed" atomics

# Outline

- Who ordered atomics?

- Compilers and the need for a memory model

- qemu/atomic.h: portable atomics in QEMU

- Future work

## **Problems with C11 atomics**

- Only supported by very recent compilers

- Limit to what older compilers can "emulate"

- Very large API, few people can understand it

- Start small, later add what turns out to be useful

- Some rules conflict with older usage

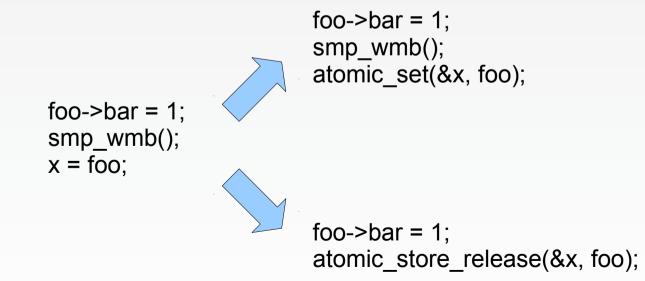

- foo->bar = 1;foo->bar = 1;smp\_wmb();atomic\_thorea(&\_fore,(memory\_order\_release);x = foo;atomic\_store(&x, foo, memory\_order\_relaxed);

# **Choosing the API**

# • Yes:

- Everything seq\_cst (load, store, RMW)

- Relaxed load/store

- RCU load/store

- Legacy:

- Compiler barrier

- Linux-style memory barriers

## • No:

- RMW operations other than seq\_cst

- Maybe:

- C11-style memory barriers

- Load-acquire

- Store-release

#### qemu/atomic.h API

- atomic\_mb\_read atomic\_mb\_set

- atomic\_rcu\_read atomic\_rcu\_set

- atomic\_read atomic set

- smp\_mb

smp\_rmb (load-load)

smp\_wmb (store-store)

- atomic\_fetch\_add atomic\_fetch\_sub atomic\_fetch\_inc

- atomic\_add atomic\_sub atomic\_inc

- atomic\_xchg

- atomic\_cmpxchg

## **Problems with portable atomics**

• Less safe than C11 stdatomic.h

```

_Atomic int x; int x;

x = 2; atomic_mb_set(&x, 2);

x += y; atomic_add(&x, y);

```

Sometimes difficult to bridge C11 and "compatibility" semantics

# **Compatibility with older compilers**

- To block optimization:

- volatile

- asm("") (aka barrier();)

- sync\_\* builtins

- If all else fails (or is too slow), asm

No synchronization for multiple threads!

#### **Problems with pre-C11 atomics**

"[C11 atomic] accesses are guaranteed to be atomic, while volatile accesses aren't.

In the volatile case we just cross our fingers hoping that the compiler will generate atomic accesses." (docs/atomics.txt)

#### **Problems with pre-C11 atomics**

- Only heavyweight memory barriers (\_\_\_sync\_synchronize)

- No seq-cst loads and stores

- Use asm for these

#### First rule of qemu/atomic.h

- Keep all pre-C11 hacks in there

- If really, really necessary use C11 atomics outside qemu/atomic.h

- NEVER use asm for atomics outside qemu/atomic.h

Corollary: relaxed-atomic optimizations should only target C11 atomics

#### qemu/atomic.h API "safe" subsets

- atomic\_mb\_read atomic\_mb\_set

- atomic\_rcu\_read atomic\_rcu\_set

- atomic\_read atomic\_set

- smp\_mb

smp\_rmb

smp\_wmb

- atomic\_fetch\_add atomic\_fetch\_sub atomic\_fetch\_inc

- atomic\_add atomic\_sub atomic\_inc

• • •

- atomic\_xchg

- atomic\_cmpxchg

#### qemu/atomic.h API "less safe" subset

- atomic\_mb\_read atomic\_mb\_set

- atomic\_rcu\_read atomic rcu set

- atomic read atomic set

- smp\_mb smp\_rmb smp\_wmb

- atomic\_fetch\_add atomic\_fetch\_sub atomic\_fetch\_inc

- atomic\_add atomic\_sub atomic\_inc

- atomic\_xchg

- atomic\_cmpxchg

# Outline

- Who ordered atomics?

- Compilers and the need for a memory model

- qemu/atomic.h: portable atomics in QEMU

- Future work

# **Choosing the API**

# • Yes:

- Everything seq\_cst (load, store, RMW)

- Relaxed load/store

- RCU load/store

- Legacy:

- Linux-style memory barriers

## • No:

- RMW operations other than seq\_cst

- Maybe:

- C11-style memory barriers

- Load-acquire

- Store-release

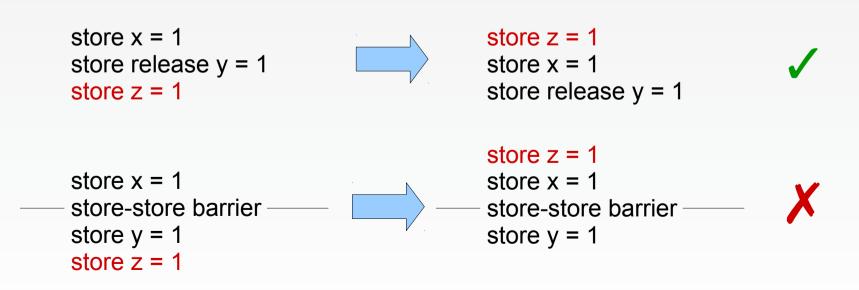

Modernize old code using memory barriers

- Use atomic\_read/atomic\_set

- Possibly introduce atomic\_load\_acquire and atomic\_store\_release

See commit 3bbf572 ("atomics: add explicit compiler fence in \_\_atomic memory barriers")

- Modernize old code using memory barriers

- Use atomic\_read/atomic\_set

- Possibly introduce atomic\_load\_acquire and atomic\_store\_release

- Seqlock-protected fields should use atomic\_read/atomic\_set too

- Change Linux-style barriers to C11 barriers

- Linux: smp\_mb(), smp\_rmb(), smp\_wmb()

- C11: seq-cst, acquire, release

|                 |            | RELEASE-BARRIER |  |  |

|-----------------|------------|-----------------|--|--|

| ACQUIRE-BARRIER | Load-load  | Load-store      |  |  |

|                 | Store-load | Store-store     |  |  |

"How to achieve [a load-store barrier] varies depending on the machine, but in practice smp\_rmb()+smp\_wmb() should have the desired effect." (docs/atomics.txt)

# • Yes:

- Everything seq\_cst (load, store, RMW)

- Relaxed load/store

- C11-style memory barriers

- Load-acquire

- Store-release

- Load-consume (RCU)

## • No:

- RMW operations other than seq\_cst

- Compiler barrier

- Linux-style memory barriers

#### "Atomics are like a chainsaw. Everyone can learn to use one, but don't let yourself get too comfortable with it."

- Herb Sutter

### **Bonus material**

### Load-acquire/store-release vs. Acquire-barrier/release-barrier

|                   | RELEABERBARRER |             |  |

|-------------------|----------------|-------------|--|

| ACIONAREABORIRRER | Load-load      | Load-store  |  |

|                   | Store-load     | Store-store |  |

# **Compiling atomics**

|         | load-consume | load-acquire         | store-release | load-seqcst                  | store-seqcst      |

|---------|--------------|----------------------|---------------|------------------------------|-------------------|

| X86     | mov          | mov                  | mov           | mov                          | xchg              |

| IA64    | ld.acq       | ld.acq               | st.rel        | ld.acq                       | st.rel<br>mf      |

| ARMv7   | ldr          | ldr<br>dmb           | dmb<br>Idr    | ldr<br>dmb                   | dmb<br>ldr<br>dmb |

| PPC     | ld           | ld<br>cmp; bc; isync | lwsync<br>st  | sync<br>ld<br>cmp; bc; isync | sync<br>st        |

| AArch64 | ldr          | ldar                 | stlr          | ldar                         | stlr              |

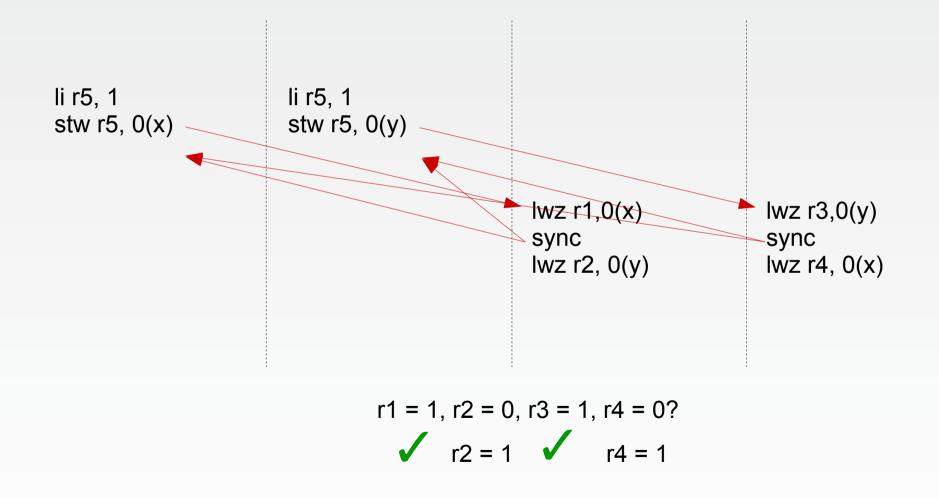

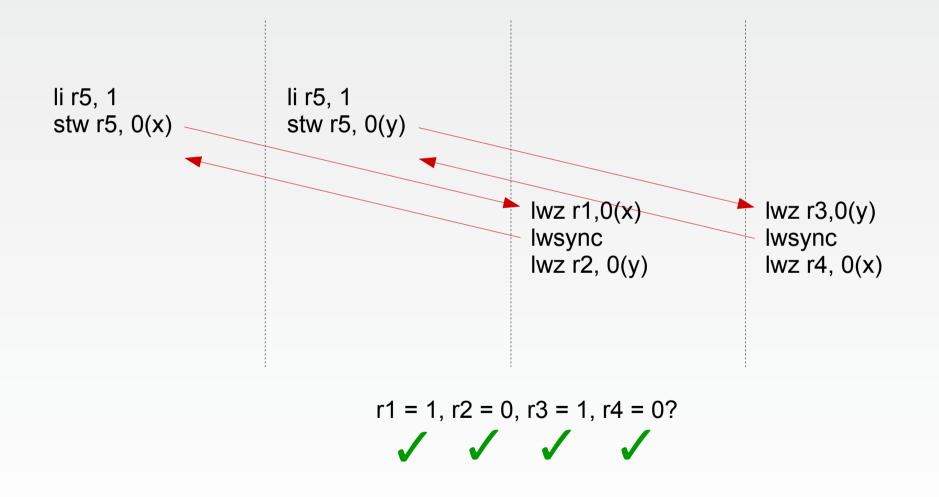

### **IRIW: independent reads of independent writes**

Х

r1 = 1, r2 = 0, r3 = 1, r4 = 0?

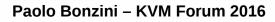

## **IRIW** and single-copy atomicity

## **IRIW and multiple-copy atomicity**