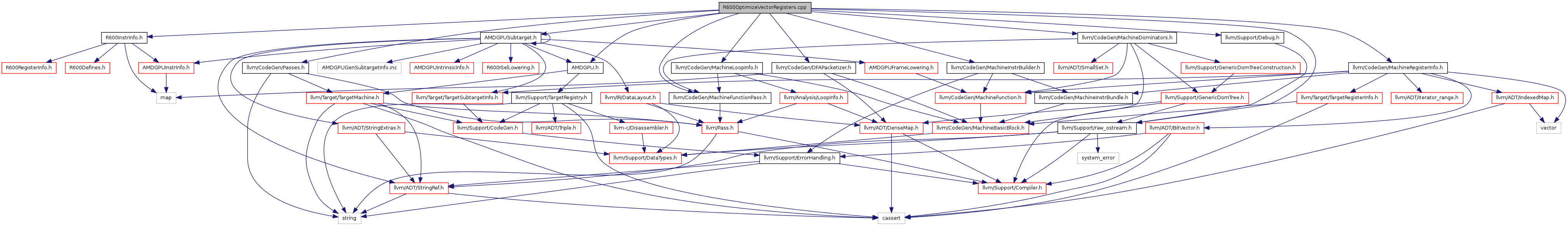

#include "llvm/Support/Debug.h"#include "AMDGPU.h"#include "R600InstrInfo.h"#include "AMDGPUSubtarget.h"#include "llvm/CodeGen/DFAPacketizer.h"#include "llvm/CodeGen/MachineDominators.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineLoopInfo.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/Passes.h"#include "llvm/Support/raw_ostream.h"

Go to the source code of this file.

Defines | |

| #define | DEBUG_TYPE "vec-merger" |

Detailed Description

This pass merges inputs of swizzeable instructions into vector sharing common data and/or have enough undef subreg using swizzle abilities.

For instance let's consider the following pseudo code : vreg5<def> = REG_SEQ vreg1, sub0, vreg2, sub1, vreg3, sub2, undef, sub3 ... vreg7<def> = REG_SEQ vreg1, sub0, vreg3, sub1, undef, sub2, vreg4, sub3 (swizzable Inst) vreg7, SwizzleMask : sub0, sub1, sub2, sub3

is turned into : vreg5<def> = REG_SEQ vreg1, sub0, vreg2, sub1, vreg3, sub2, undef, sub3 ... vreg7<def> = INSERT_SUBREG vreg4, sub3 (swizzable Inst) vreg7, SwizzleMask : sub0, sub2, sub1, sub3

This allow regalloc to reduce register pressure for vector registers and to reduce MOV count.

Definition in file R600OptimizeVectorRegisters.cpp.

Define Documentation

| #define DEBUG_TYPE "vec-merger" |

Definition at line 45 of file R600OptimizeVectorRegisters.cpp.

1.7.6.1

1.7.6.1