Namespaces |

| namespace | llvm |

| | List of target independent CodeGen pass IDs.

|

| namespace | llvm::AMDGPU |

| namespace | ShaderType |

| namespace | AMDGPUAS |

Defines |

| #define | END_OF_TEXT_LABEL_NAME "EndOfTextLabel" |

Enumerations |

| enum | llvm::AMDGPU::TargetIndex { llvm::AMDGPU::TI_CONSTDATA_START

} |

| enum | ShaderType::Type { ShaderType::PIXEL = 0,

ShaderType::VERTEX = 1,

ShaderType::GEOMETRY = 2,

ShaderType::COMPUTE = 3

} |

| enum | AMDGPUAS::AddressSpaces {

AMDGPUAS::PRIVATE_ADDRESS = 0,

AMDGPUAS::GLOBAL_ADDRESS = 1,

AMDGPUAS::CONSTANT_ADDRESS = 2,

AMDGPUAS::LOCAL_ADDRESS = 3,

AMDGPUAS::FLAT_ADDRESS = 4,

AMDGPUAS::REGION_ADDRESS = 5,

AMDGPUAS::PARAM_D_ADDRESS = 6,

AMDGPUAS::PARAM_I_ADDRESS = 7,

AMDGPUAS::CONSTANT_BUFFER_0 = 8,

AMDGPUAS::CONSTANT_BUFFER_1 = 9,

AMDGPUAS::CONSTANT_BUFFER_2 = 10,

AMDGPUAS::CONSTANT_BUFFER_3 = 11,

AMDGPUAS::CONSTANT_BUFFER_4 = 12,

AMDGPUAS::CONSTANT_BUFFER_5 = 13,

AMDGPUAS::CONSTANT_BUFFER_6 = 14,

AMDGPUAS::CONSTANT_BUFFER_7 = 15,

AMDGPUAS::CONSTANT_BUFFER_8 = 16,

AMDGPUAS::CONSTANT_BUFFER_9 = 17,

AMDGPUAS::CONSTANT_BUFFER_10 = 18,

AMDGPUAS::CONSTANT_BUFFER_11 = 19,

AMDGPUAS::CONSTANT_BUFFER_12 = 20,

AMDGPUAS::CONSTANT_BUFFER_13 = 21,

AMDGPUAS::CONSTANT_BUFFER_14 = 22,

AMDGPUAS::CONSTANT_BUFFER_15 = 23,

AMDGPUAS::ADDRESS_NONE = 24,

AMDGPUAS::LAST_ADDRESS = ADDRESS_NONE

} |

Functions |

| FunctionPass * | llvm::createR600VectorRegMerger (TargetMachine &tm) |

| FunctionPass * | llvm::createR600TextureIntrinsicsReplacer () |

| FunctionPass * | llvm::createR600ExpandSpecialInstrsPass (TargetMachine &tm) |

| FunctionPass * | llvm::createR600EmitClauseMarkers () |

| FunctionPass * | llvm::createR600ClauseMergePass (TargetMachine &tm) |

| FunctionPass * | llvm::createR600Packetizer (TargetMachine &tm) |

| FunctionPass * | llvm::createR600ControlFlowFinalizer (TargetMachine &tm) |

| FunctionPass * | llvm::createAMDGPUCFGStructurizerPass () |

| FunctionPass * | llvm::createSITypeRewriter () |

| FunctionPass * | llvm::createSIAnnotateControlFlowPass () |

| | Create the annotation pass.

|

| FunctionPass * | llvm::createSILowerI1CopiesPass () |

| FunctionPass * | llvm::createSIShrinkInstructionsPass () |

| FunctionPass * | llvm::createSILowerControlFlowPass (TargetMachine &tm) |

| FunctionPass * | llvm::createSIFixSGPRCopiesPass (TargetMachine &tm) |

| FunctionPass * | llvm::createSIFixSGPRLiveRangesPass () |

| FunctionPass * | llvm::createSICodeEmitterPass (formatted_raw_ostream &OS) |

| FunctionPass * | llvm::createSIInsertWaits (TargetMachine &tm) |

| void | llvm::initializeSILowerI1CopiesPass (PassRegistry &) |

| FunctionPass * | llvm::createAMDGPUPromoteAlloca (const AMDGPUSubtarget &ST) |

| Pass * | llvm::createAMDGPUStructurizeCFGPass () |

| FunctionPass * | llvm::createAMDGPUISelDag (TargetMachine &tm) |

| | This pass converts a legalized DAG into a AMDGPU-specific.

|

| ImmutablePass * | llvm::createAMDGPUTargetTransformInfoPass (const AMDGPUTargetMachine *TM) |

| | Creates an AMDGPU-specific Target Transformation Info pass.

|

| void | llvm::initializeSIFixSGPRLiveRangesPass (PassRegistry &) |

Variables |

| char & | llvm::SILowerI1CopiesID = SILowerI1Copies::ID |

| char & | llvm::SIFixSGPRLiveRangesID = SIFixSGPRLiveRanges::ID |

| Target | llvm::TheAMDGPUTarget |

| | The target for the AMDGPU backend.

|

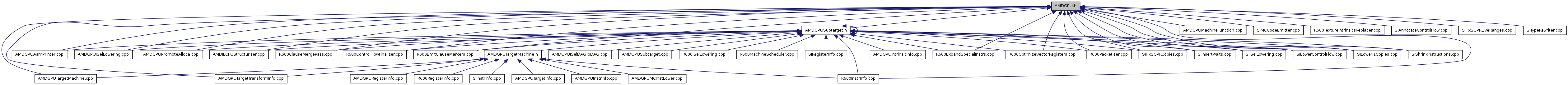

Definition in file AMDGPU.h.

1.7.6.1

1.7.6.1