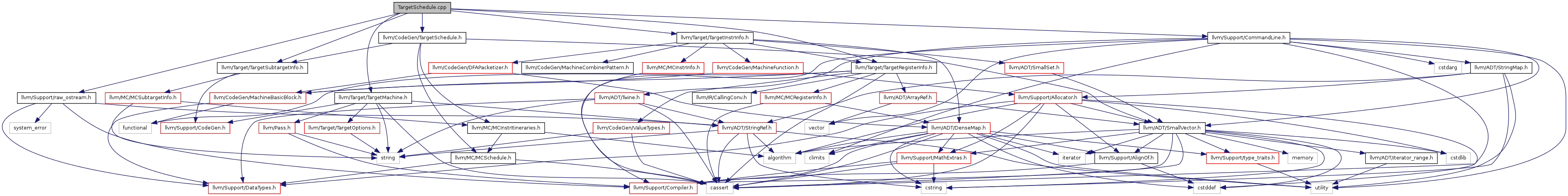

#include "llvm/CodeGen/TargetSchedule.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetInstrInfo.h"#include "llvm/Target/TargetMachine.h"#include "llvm/Target/TargetRegisterInfo.h"#include "llvm/Target/TargetSubtargetInfo.h"

Go to the source code of this file.

Functions | |

| static unsigned | gcd (unsigned Dividend, unsigned Divisor) |

| static unsigned | lcm (unsigned A, unsigned B) |

| static unsigned | capLatency (int Cycles) |

| static unsigned | findDefIdx (const MachineInstr *MI, unsigned DefOperIdx) |

| static unsigned | findUseIdx (const MachineInstr *MI, unsigned UseOperIdx) |

Variables | |

| static cl::opt< bool > | EnableSchedModel ("schedmodel", cl::Hidden, cl::init(true), cl::desc("Use TargetSchedModel for latency lookup")) |

| static cl::opt< bool > | EnableSchedItins ("scheditins", cl::Hidden, cl::init(true), cl::desc("Use InstrItineraryData for latency lookup")) |

Function Documentation

| static unsigned capLatency | ( | int | Cycles | ) | [static] |

Definition at line 96 of file TargetSchedule.cpp.

Referenced by llvm::TargetSchedModel::computeInstrLatency(), and llvm::TargetSchedModel::computeOperandLatency().

| static unsigned findDefIdx | ( | const MachineInstr * | MI, |

| unsigned | DefOperIdx | ||

| ) | [static] |

Find the def index of this operand. This index maps to the machine model and is independent of use operands. Def operands may be reordered with uses or merged with uses without affecting the def index (e.g. before/after regalloc). However, an instruction's def operands must never be reordered with respect to each other.

Definition at line 128 of file TargetSchedule.cpp.

References llvm::MachineInstr::getOperand(), llvm::MachineOperand::isDef(), and llvm::MachineOperand::isReg().

Referenced by llvm::TargetSchedModel::computeOperandLatency().

| static unsigned findUseIdx | ( | const MachineInstr * | MI, |

| unsigned | UseOperIdx | ||

| ) | [static] |

Find the use index of this operand. This is independent of the instruction's def operands.

Note that uses are not determined by the operand's isUse property, which is simply the inverse of isDef. Here we consider any readsReg operand to be a "use". The machine model allows an operand to be both a Def and Use.

Definition at line 144 of file TargetSchedule.cpp.

References llvm::MachineInstr::getOperand(), llvm::MachineOperand::isReg(), and llvm::MachineOperand::readsReg().

Referenced by llvm::TargetSchedModel::computeOperandLatency().

Definition at line 39 of file TargetSchedule.cpp.

Referenced by lcm().

Definition at line 48 of file TargetSchedule.cpp.

References gcd().

Referenced by llvm::TargetSchedModel::init().

Variable Documentation

cl::opt<bool> EnableSchedItins("scheditins", cl::Hidden, cl::init(true), cl::desc("Use InstrItineraryData for latency lookup")) [static] |

Referenced by llvm::TargetSchedModel::hasInstrItineraries().

cl::opt<bool> EnableSchedModel("schedmodel", cl::Hidden, cl::init(true), cl::desc("Use TargetSchedModel for latency lookup")) [static] |

Referenced by llvm::TargetSchedModel::hasInstrSchedModel().

1.7.6.1

1.7.6.1