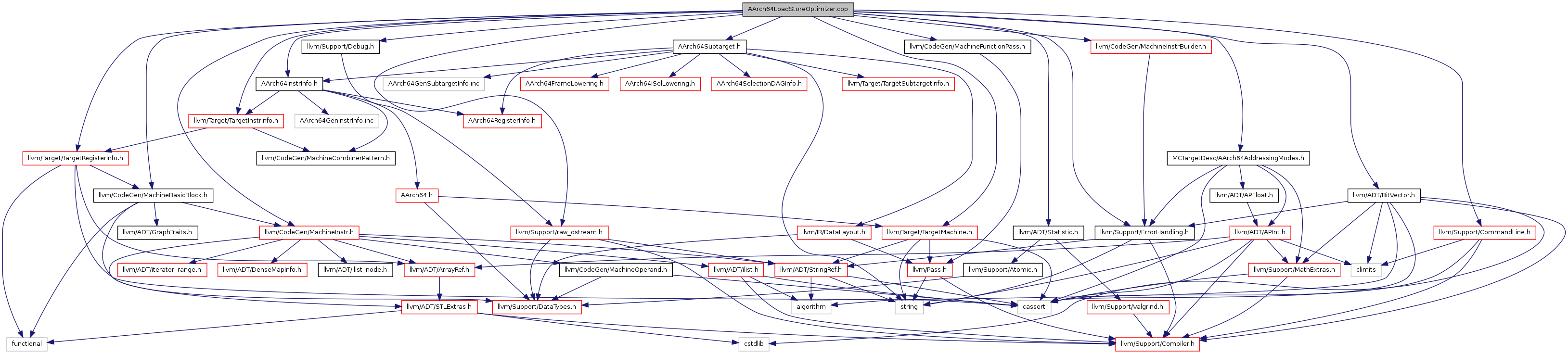

#include "AArch64InstrInfo.h"#include "AArch64Subtarget.h"#include "MCTargetDesc/AArch64AddressingModes.h"#include "llvm/ADT/BitVector.h"#include "llvm/ADT/Statistic.h"#include "llvm/CodeGen/MachineBasicBlock.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstr.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetInstrInfo.h"#include "llvm/Target/TargetMachine.h"#include "llvm/Target/TargetRegisterInfo.h"

Go to the source code of this file.

Defines | |

| #define | DEBUG_TYPE "aarch64-ldst-opt" |

Functions | |

| STATISTIC (NumPairCreated,"Number of load/store pair instructions generated") | |

| STATISTIC (NumPostFolded,"Number of post-index updates folded") | |

| STATISTIC (NumPreFolded,"Number of pre-index updates folded") | |

| STATISTIC (NumUnscaledPairCreated,"Number of load/store from unscaled generated") | |

| static bool | isUnscaledLdst (unsigned Opc) |

| static unsigned | getMatchingPairOpcode (unsigned Opc) |

| static unsigned | getPreIndexedOpcode (unsigned Opc) |

| static unsigned | getPostIndexedOpcode (unsigned Opc) |

| static void | trackRegDefsUses (MachineInstr *MI, BitVector &ModifiedRegs, BitVector &UsedRegs, const TargetRegisterInfo *TRI) |

| static bool | inBoundsForPair (bool IsUnscaled, int Offset, int OffsetStride) |

| static int | alignTo (int Num, int PowOf2) |

| static bool | isMatchingUpdateInsn (MachineInstr *MI, unsigned BaseReg, int Offset) |

Variables | |

| static cl::opt< unsigned > | ScanLimit ("aarch64-load-store-scan-limit", cl::init(20), cl::Hidden) |

| static cl::opt< bool > | EnableAArch64UnscaledMemOp ("aarch64-unscaled-mem-op", cl::Hidden, cl::desc("Allow AArch64 unscaled load/store combining"), cl::init(true)) |

Define Documentation

| #define DEBUG_TYPE "aarch64-ldst-opt" |

Definition at line 33 of file AArch64LoadStoreOptimizer.cpp.

Function Documentation

Definition at line 379 of file AArch64LoadStoreOptimizer.cpp.

| static unsigned getMatchingPairOpcode | ( | unsigned | Opc | ) | [static] |

Definition at line 179 of file AArch64LoadStoreOptimizer.cpp.

References llvm_unreachable.

| static unsigned getPostIndexedOpcode | ( | unsigned | Opc | ) | [static] |

Definition at line 243 of file AArch64LoadStoreOptimizer.cpp.

References llvm_unreachable.

| static unsigned getPreIndexedOpcode | ( | unsigned | Opc | ) | [static] |

Definition at line 216 of file AArch64LoadStoreOptimizer.cpp.

References llvm_unreachable.

| static bool inBoundsForPair | ( | bool | IsUnscaled, |

| int | Offset, | ||

| int | OffsetStride | ||

| ) | [static] |

Definition at line 362 of file AArch64LoadStoreOptimizer.cpp.

| static bool isMatchingUpdateInsn | ( | MachineInstr * | MI, |

| unsigned | BaseReg, | ||

| int | Offset | ||

| ) | [static] |

Definition at line 607 of file AArch64LoadStoreOptimizer.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::AArch64_AM::getShiftValue(), and llvm::MachineOperand::isImm().

| static bool isUnscaledLdst | ( | unsigned | Opc | ) | [static] |

Definition at line 114 of file AArch64LoadStoreOptimizer.cpp.

| STATISTIC | ( | NumPairCreated | , |

| "Number of load/store pair instructions generated" | |||

| ) |

AArch64AllocLoadStoreOpt - Post-register allocation pass to combine load / store instructions to form ldp / stp instructions.

| STATISTIC | ( | NumPostFolded | , |

| "Number of post-index updates folded" | |||

| ) |

| STATISTIC | ( | NumPreFolded | , |

| "Number of pre-index updates folded" | |||

| ) |

| static void trackRegDefsUses | ( | MachineInstr * | MI, |

| BitVector & | ModifiedRegs, | ||

| BitVector & | UsedRegs, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | [static] |

trackRegDefsUses - Remember what registers the specified instruction uses and modifies.

Definition at line 340 of file AArch64LoadStoreOptimizer.cpp.

References llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getRegMask(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), llvm::MachineOperand::isUse(), llvm::MCRegAliasIterator::isValid(), llvm::BitVector::set(), and llvm::BitVector::setBitsNotInMask().

Variable Documentation

cl::opt<bool> EnableAArch64UnscaledMemOp("aarch64-unscaled-mem-op", cl::Hidden, cl::desc("Allow AArch64 unscaled load/store combining"), cl::init(true)) [static] |

1.7.6.1

1.7.6.1