#include "AArch64.h"#include "AArch64TargetMachine.h"#include "llvm/CodeGen/Passes.h"#include "llvm/CodeGen/RegAllocRegistry.h"#include "llvm/PassManager.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/TargetRegistry.h"#include "llvm/Target/TargetOptions.h"#include "llvm/Transforms/Scalar.h"

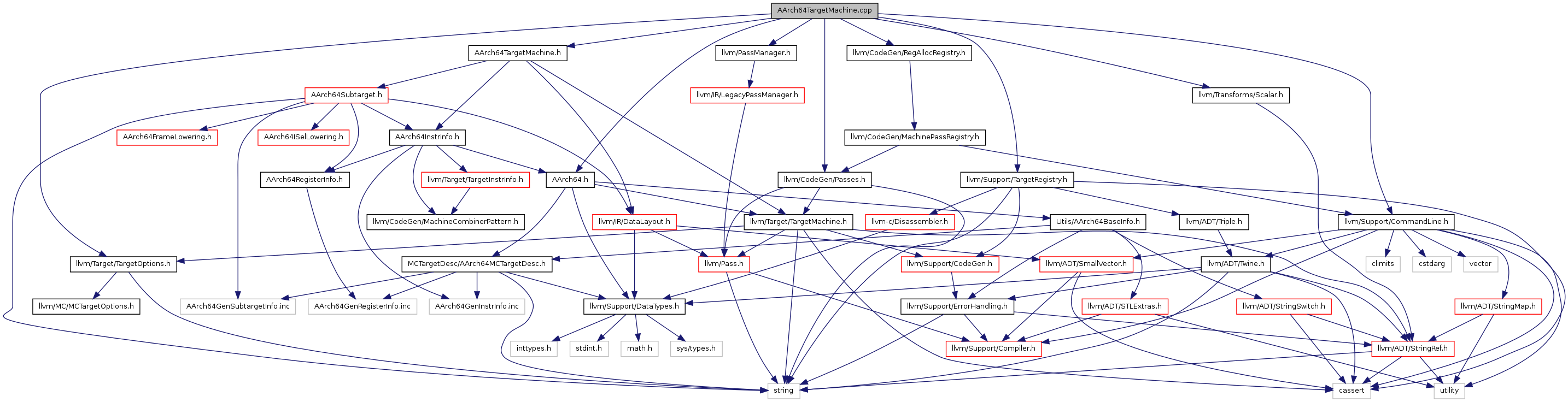

Include dependency graph for AArch64TargetMachine.cpp:

Go to the source code of this file.

Functions | |

| void | LLVMInitializeAArch64Target () |

Variables | |

| static cl::opt< bool > | EnableCCMP ("aarch64-ccmp", cl::desc("Enable the CCMP formation pass"), cl::init(true), cl::Hidden) |

| static cl::opt< bool > | EnableMCR ("aarch64-mcr", cl::desc("Enable the machine combiner pass"), cl::init(true), cl::Hidden) |

| static cl::opt< bool > | EnableStPairSuppress ("aarch64-stp-suppress", cl::desc("Suppress STP for AArch64"), cl::init(true), cl::Hidden) |

| static cl::opt< bool > | EnableAdvSIMDScalar ("aarch64-simd-scalar", cl::desc("Enable use of AdvSIMD scalar"" integer instructions"), cl::init(false), cl::Hidden) |

| static cl::opt< bool > | EnablePromoteConstant ("aarch64-promote-const", cl::desc("Enable the promote ""constant pass"), cl::init(true), cl::Hidden) |

| static cl::opt< bool > | EnableCollectLOH ("aarch64-collect-loh", cl::desc("Enable the pass that emits the"" linker optimization hints (LOH)"), cl::init(true), cl::Hidden) |

| static cl::opt< bool > | EnableDeadRegisterElimination ("aarch64-dead-def-elimination", cl::Hidden, cl::desc("Enable the pass that removes dead"" definitons and replaces stores to"" them with stores to the zero"" register"), cl::init(true)) |

| static cl::opt< bool > | EnableLoadStoreOpt ("aarch64-load-store-opt", cl::desc("Enable the load/store pair"" optimization pass"), cl::init(true), cl::Hidden) |

| static cl::opt< bool > | EnableAtomicTidy ("aarch64-atomic-cfg-tidy", cl::Hidden, cl::desc("Run SimplifyCFG after expanding atomic operations"" to make use of cmpxchg flow-based information"), cl::init(true)) |

| static cl::opt< bool > | EnableEarlyIfConversion ("aarch64-enable-early-ifcvt", cl::Hidden, cl::desc("Run early if-conversion"), cl::init(true)) |

| static cl::opt< bool > | EnableCondOpt ("aarch64-condopt", cl::desc("Enable the condition optimizer pass"), cl::init(true), cl::Hidden) |

| static cl::opt< bool > | EnablePBQP ("aarch64-pbqp", cl::Hidden, cl::desc("Use PBQP register allocator (experimental)"), cl::init(false)) |

Function Documentation

| void LLVMInitializeAArch64Target | ( | ) |

Definition at line 82 of file AArch64TargetMachine.cpp.

References llvm::TheAArch64beTarget, llvm::TheAArch64leTarget, llvm::TheARM64Target, llvm::X, and Y.

Variable Documentation

cl::opt<bool> EnableAdvSIMDScalar("aarch64-simd-scalar", cl::desc("Enable use of AdvSIMD scalar"" integer instructions"), cl::init(false), cl::Hidden) [static] |

cl::opt<bool> EnableAtomicTidy("aarch64-atomic-cfg-tidy", cl::Hidden, cl::desc("Run SimplifyCFG after expanding atomic operations"" to make use of cmpxchg flow-based information"), cl::init(true)) [static] |

cl::opt<bool> EnableCCMP("aarch64-ccmp", cl::desc("Enable the CCMP formation pass"), cl::init(true), cl::Hidden) [static] |

cl::opt<bool> EnableCollectLOH("aarch64-collect-loh", cl::desc("Enable the pass that emits the"" linker optimization hints (LOH)"), cl::init(true), cl::Hidden) [static] |

cl::opt<bool> EnableCondOpt("aarch64-condopt", cl::desc("Enable the condition optimizer pass"), cl::init(true), cl::Hidden) [static] |

cl::opt<bool> EnableDeadRegisterElimination("aarch64-dead-def-elimination", cl::Hidden, cl::desc("Enable the pass that removes dead"" definitons and replaces stores to"" them with stores to the zero"" register"), cl::init(true)) [static] |

cl::opt<bool> EnableEarlyIfConversion("aarch64-enable-early-ifcvt", cl::Hidden, cl::desc("Run early if-conversion"), cl::init(true)) [static] |

cl::opt<bool> EnableLoadStoreOpt("aarch64-load-store-opt", cl::desc("Enable the load/store pair"" optimization pass"), cl::init(true), cl::Hidden) [static] |

cl::opt<bool> EnableMCR("aarch64-mcr", cl::desc("Enable the machine combiner pass"), cl::init(true), cl::Hidden) [static] |

cl::opt<bool> EnablePBQP("aarch64-pbqp", cl::Hidden, cl::desc("Use PBQP register allocator (experimental)"), cl::init(false)) [static] |

Referenced by llvm::AArch64TargetMachine::AArch64TargetMachine().

cl::opt<bool> EnablePromoteConstant("aarch64-promote-const", cl::desc("Enable the promote ""constant pass"), cl::init(true), cl::Hidden) [static] |

cl::opt<bool> EnableStPairSuppress("aarch64-stp-suppress", cl::desc("Suppress STP for AArch64"), cl::init(true), cl::Hidden) [static] |

1.7.6.1

1.7.6.1