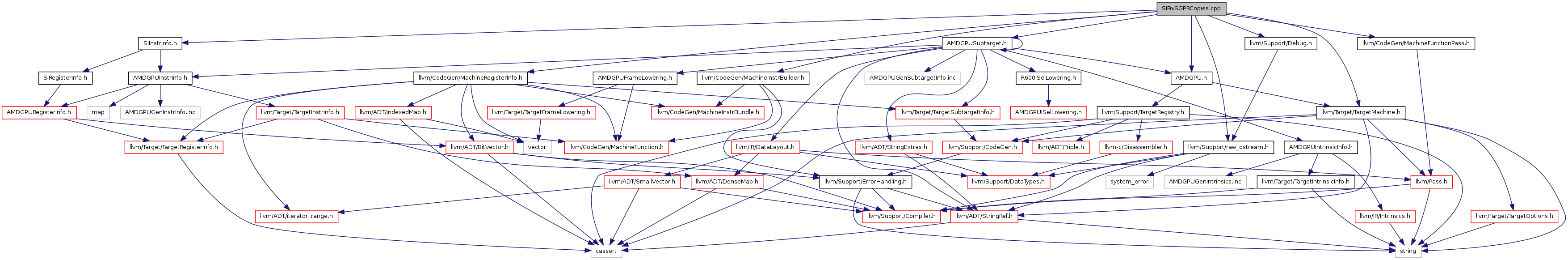

#include "AMDGPU.h"#include "AMDGPUSubtarget.h"#include "SIInstrInfo.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/Support/Debug.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetMachine.h"

Go to the source code of this file.

Defines | |

| #define | DEBUG_TYPE "sgpr-copies" |

Functions | |

| static bool | hasVGPROperands (const MachineInstr &MI, const SIRegisterInfo *TRI) |

Detailed Description

Copies from VGPR to SGPR registers are illegal and the register coalescer will sometimes generate these illegal copies in situations like this:

Register Class <vsrc> is the union of <vgpr> and <sgpr>

BB0: vreg0 <sgpr> = SCALAR_INST vreg1 <vsrc> = COPY vreg0 <sgpr> ... BRANCH cond BB1, BB2 BB1: vreg2 <vgpr> = VECTOR_INST vreg3 <vsrc> = COPY vreg2 <vgpr> BB2: vreg4 <vsrc> = PHI vreg1 <vsrc>, <BB#0>, vreg3 <vrsc>, <BB#1> vreg5 <vgpr> = VECTOR_INST vreg4 <vsrc>

The coalescer will begin at BB0 and eliminate its copy, then the resulting code will look like this:

BB0: vreg0 <sgpr> = SCALAR_INST ... BRANCH cond BB1, BB2 BB1: vreg2 <vgpr> = VECTOR_INST vreg3 <vsrc> = COPY vreg2 <vgpr> BB2: vreg4 <sgpr> = PHI vreg0 <sgpr>, <BB#0>, vreg3 <vsrc>, <BB#1> vreg5 <vgpr> = VECTOR_INST vreg4 <sgpr>

Now that the result of the PHI instruction is an SGPR, the register allocator is now forced to constrain the register class of vreg3 to <sgpr> so we end up with final code like this:

BB0: vreg0 <sgpr> = SCALAR_INST ... BRANCH cond BB1, BB2 BB1: vreg2 <vgpr> = VECTOR_INST vreg3 <sgpr> = COPY vreg2 <vgpr> BB2: vreg4 <sgpr> = PHI vreg0 <sgpr>, <BB#0>, vreg3 <sgpr>, <BB#1> vreg5 <vgpr> = VECTOR_INST vreg4 <sgpr>

Now this code contains an illegal copy from a VGPR to an SGPR.

In order to avoid this problem, this pass searches for PHI instructions which define a <vsrc> register and constrains its definition class to <vgpr> if the user of the PHI's definition register is a vector instruction. If the PHI's definition class is constrained to <vgpr> then the coalescer will be unable to perform the COPY removal from the above example which ultimately led to the creation of an illegal COPY.

Definition in file SIFixSGPRCopies.cpp.

Define Documentation

| #define DEBUG_TYPE "sgpr-copies" |

Definition at line 80 of file SIFixSGPRCopies.cpp.

Function Documentation

| static bool hasVGPROperands | ( | const MachineInstr & | MI, |

| const SIRegisterInfo * | TRI | ||

| ) | [static] |

Definition at line 118 of file SIFixSGPRCopies.cpp.

References llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::SIRegisterInfo::hasVGPRs(), llvm::MachineOperand::isReg(), and llvm::TargetRegisterInfo::isVirtualRegister().

1.7.6.1

1.7.6.1