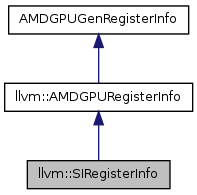

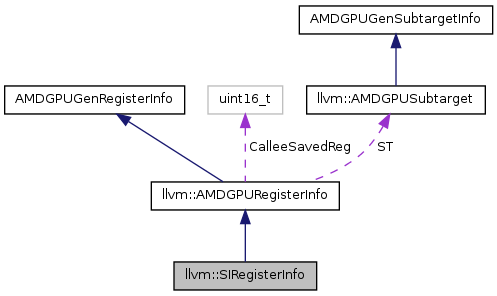

#include <SIRegisterInfo.h>

Detailed Description

Definition at line 23 of file SIRegisterInfo.h.

Member Enumeration Documentation

Definition at line 78 of file SIRegisterInfo.h.

Constructor & Destructor Documentation

Definition at line 28 of file SIRegisterInfo.cpp.

Member Function Documentation

| void SIRegisterInfo::eliminateFrameIndex | ( | MachineBasicBlock::iterator | MI, |

| int | SPAdj, | ||

| unsigned | FIOperandNum, | ||

| RegScavenger * | RS | ||

| ) | const [override] |

Reimplemented from llvm::AMDGPURegisterInfo.

Definition at line 71 of file SIRegisterInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::BuildMI(), llvm::MachineOperand::ChangeToImmediate(), llvm::MachineOperand::ChangeToRegister(), llvm::LLVMContext::emitError(), llvm::MachineInstr::eraseFromParent(), llvm::Function::getContext(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getIndex(), llvm::MachineFunction::getInfo(), llvm::AMDGPUSubtarget::getInstrInfo(), getNumSubRegsForSpillOp(), llvm::MachineBasicBlock::getParent(), getPhysRegSubReg(), llvm::SIMachineFunctionInfo::getSpilledReg(), llvm::SIInstrInfo::insertNOPs(), llvm::SIInstrInfo::isImmOperandLegal(), llvm::SIMachineFunctionInfo::SpilledReg::Lane, llvm::RegScavenger::scavengeRegister(), llvm::AMDGPURegisterInfo::ST, TII, and llvm::SIMachineFunctionInfo::SpilledReg::VGPR.

| const TargetRegisterClass * SIRegisterInfo::getCFGStructurizerRegClass | ( | MVT | VT | ) | const [override, virtual] |

get the register class of the specified type to use in the CFGStructurizer

Reimplemented from llvm::AMDGPURegisterInfo.

Definition at line 156 of file SIRegisterInfo.cpp.

References llvm::MVT::i32, and llvm::MVT::SimpleTy.

| const TargetRegisterClass * SIRegisterInfo::getEquivalentVGPRClass | ( | const TargetRegisterClass * | SRC | ) | const |

- Returns:

- A VGPR reg class with the same width as

SRC

Definition at line 204 of file SIRegisterInfo.cpp.

References hasVGPRs().

Referenced by llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::legalizeOpWithMove(), and llvm::SIInstrInfo::moveToVALU().

| unsigned SIRegisterInfo::getHWRegIndex | ( | unsigned | Reg | ) | const [override, virtual] |

Reimplemented from llvm::AMDGPURegisterInfo.

Definition at line 164 of file SIRegisterInfo.cpp.

Referenced by getPhysRegSubReg().

| const TargetRegisterClass * SIRegisterInfo::getPhysRegClass | ( | unsigned | Reg | ) | const |

Return the 'base' register class for this register. e.g. SGPR0 => SReg_32, VGPR => VReg_32 SGPR0_SGPR1 -> SReg_32, etc.

Definition at line 168 of file SIRegisterInfo.cpp.

References llvm::TargetRegisterInfo::isVirtualRegister().

Referenced by isVGPR().

| unsigned SIRegisterInfo::getPhysRegSubReg | ( | unsigned | Reg, |

| const TargetRegisterClass * | SubRC, | ||

| unsigned | Channel | ||

| ) | const |

Channel This is the register channel (e.g. a value from 0-16), not the SubReg index.

- Returns:

- The sub-register of Reg that is in Channel.

Definition at line 238 of file SIRegisterInfo.cpp.

References getHWRegIndex(), llvm::TargetRegisterClass::getRegister(), and llvm_unreachable.

Referenced by eliminateFrameIndex().

| unsigned SIRegisterInfo::getPreloadedValue | ( | const MachineFunction & | MF, |

| enum PreloadedValue | Value | ||

| ) | const |

Returns the physical register that Value is stored in.

Definition at line 294 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getInfo(), llvm_unreachable, llvm::SIMachineFunctionInfo::NumUserSGPRs, SCRATCH_PTR, SCRATCH_WAVE_OFFSET, TGID_X, TGID_Y, and TGID_Z.

| unsigned SIRegisterInfo::getRegPressureLimit | ( | const TargetRegisterClass * | RC, |

| MachineFunction & | MF | ||

| ) | const [override] |

Definition at line 40 of file SIRegisterInfo.cpp.

References llvm::TargetRegisterClass::getNumRegs().

| BitVector SIRegisterInfo::getReservedRegs | ( | const MachineFunction & | MF | ) | const [override] |

Reimplemented from llvm::AMDGPURegisterInfo.

Definition at line 32 of file SIRegisterInfo.cpp.

References llvm::BitVector::set().

| const TargetRegisterClass * SIRegisterInfo::getSubRegClass | ( | const TargetRegisterClass * | RC, |

| unsigned | SubIdx | ||

| ) | const |

- Returns:

- The register class that is used for a sub-register of

RCfor the givenSubIdx. IfSubIdxequals NoSubRegister,RCwill be returned.

Definition at line 224 of file SIRegisterInfo.cpp.

References isSGPRClass().

| bool SIRegisterInfo::hasVGPRs | ( | const TargetRegisterClass * | RC | ) | const |

- Returns:

- true if this class contains VGPR registers.

Definition at line 195 of file SIRegisterInfo.cpp.

Referenced by llvm::SIInstrInfo::canReadVGPR(), getEquivalentVGPRClass(), hasVGPROperands(), isSGPRClass(), isVGPR(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::loadRegFromStackSlot(), llvm::SIInstrInfo::moveToVALU(), and llvm::SIInstrInfo::storeRegToStackSlot().

| bool SIRegisterInfo::isSGPRClass | ( | const TargetRegisterClass * | RC | ) | const |

- Returns:

- true if this class contains only SGPR registers

Definition at line 188 of file SIRegisterInfo.cpp.

References hasVGPRs().

Referenced by getSubRegClass(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::legalizeOpWithMove(), llvm::SIInstrInfo::loadRegFromStackSlot(), and llvm::SIInstrInfo::storeRegToStackSlot().

| bool SIRegisterInfo::regClassCanUseImmediate | ( | int | RCID | ) | const |

- Returns:

- True if operands defined with this register class can accept inline immediates.

Definition at line 278 of file SIRegisterInfo.cpp.

Referenced by llvm::SIInstrInfo::isImmOperandLegal(), llvm::SIInstrInfo::isOperandLegal(), regClassCanUseImmediate(), and llvm::SIInstrInfo::verifyInstruction().

| bool SIRegisterInfo::regClassCanUseImmediate | ( | const TargetRegisterClass * | RC | ) | const |

- Returns:

- True if operands defined with this register class can accept inline immediates.

Definition at line 289 of file SIRegisterInfo.cpp.

References llvm::TargetRegisterClass::getID(), and regClassCanUseImmediate().

| bool SIRegisterInfo::requiresRegisterScavenging | ( | const MachineFunction & | Fn | ) | const [override] |

Definition at line 45 of file SIRegisterInfo.cpp.

References llvm::MachineFunction::getFrameInfo(), and llvm::MachineFrameInfo::hasStackObjects().

The documentation for this struct was generated from the following files:

1.7.6.1

1.7.6.1