#include <Mips16ISelLowering.h>

Public Member Functions | |

| Mips16TargetLowering (MipsTargetMachine &TM, const MipsSubtarget &STI) | |

| bool | allowsMisalignedMemoryAccesses (EVT VT, unsigned AddrSpace, unsigned Align, bool *Fast) const override |

| Determine if the target supports unaligned memory accesses. | |

| MachineBasicBlock * | EmitInstrWithCustomInserter (MachineInstr *MI, MachineBasicBlock *MBB) const override |

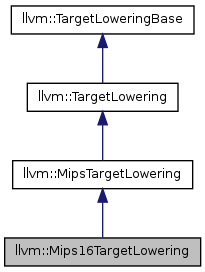

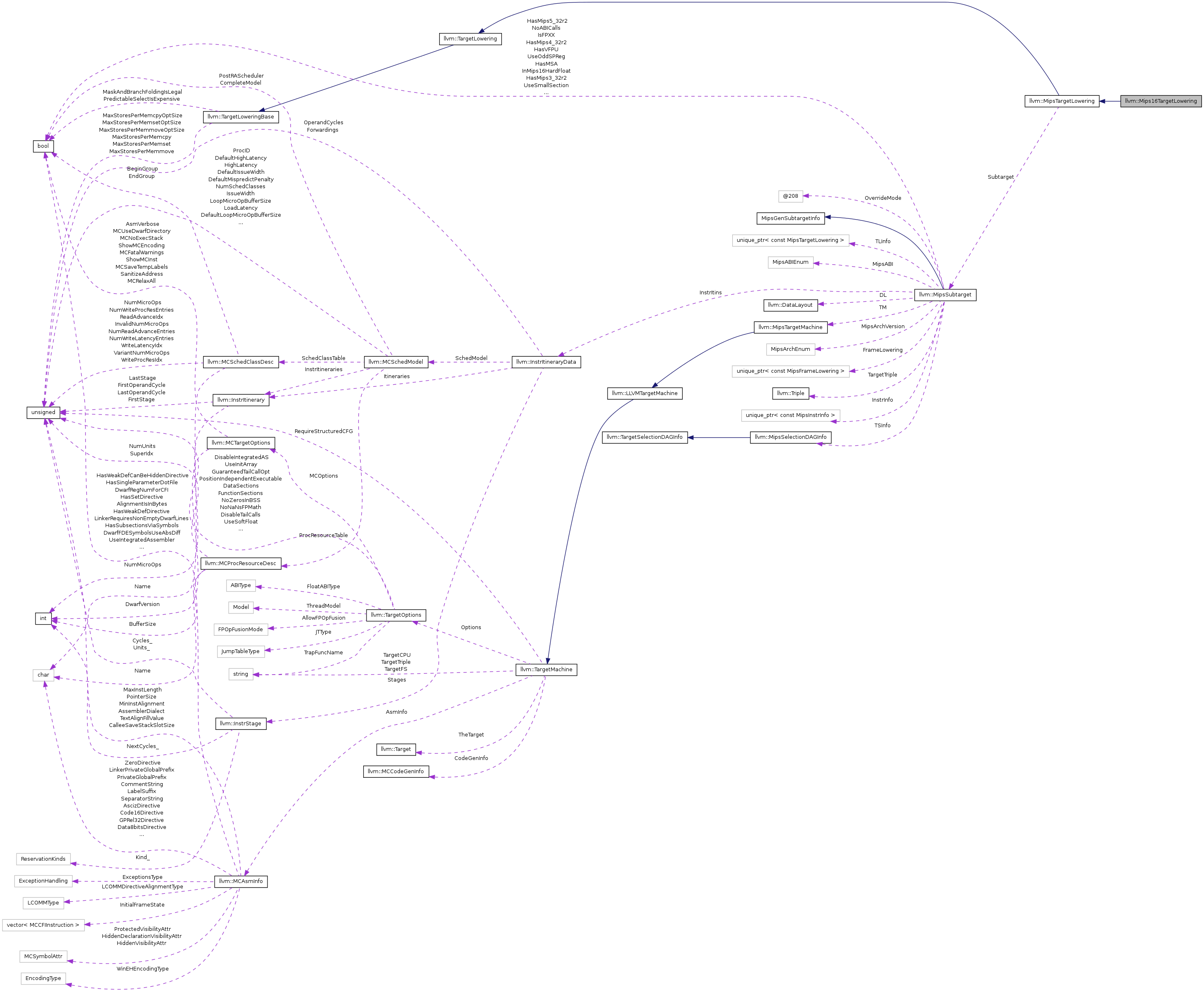

Detailed Description

Definition at line 20 of file Mips16ISelLowering.h.

Constructor & Destructor Documentation

| Mips16TargetLowering::Mips16TargetLowering | ( | MipsTargetMachine & | TM, |

| const MipsSubtarget & | STI | ||

| ) | [explicit] |

Definition at line 123 of file Mips16ISelLowering.cpp.

References llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::ATOMIC_CMP_SWAP, llvm::ISD::ATOMIC_FENCE, llvm::ISD::ATOMIC_LOAD_ADD, llvm::ISD::ATOMIC_LOAD_AND, llvm::ISD::ATOMIC_LOAD_MAX, llvm::ISD::ATOMIC_LOAD_MIN, llvm::ISD::ATOMIC_LOAD_NAND, llvm::ISD::ATOMIC_LOAD_OR, llvm::ISD::ATOMIC_LOAD_SUB, llvm::ISD::ATOMIC_LOAD_UMAX, llvm::ISD::ATOMIC_LOAD_UMIN, llvm::ISD::ATOMIC_LOAD_XOR, llvm::ISD::ATOMIC_SWAP, llvm::ISD::BSWAP, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::TargetLoweringBase::Expand, llvm::MVT::i32, llvm::MVT::i64, llvm::TargetMachine::Options, llvm::MVT::Other, llvm::ISD::ROTR, llvm::TargetLoweringBase::setOperationAction(), and llvm::TargetOptions::UseSoftFloat.

Member Function Documentation

| bool Mips16TargetLowering::allowsMisalignedMemoryAccesses | ( | EVT | , |

| unsigned | AddrSpace, | ||

| unsigned | Align, | ||

| bool * | |||

| ) | const [override, virtual] |

Determine if the target supports unaligned memory accesses.

This function returns true if the target allows unaligned memory accesses of the specified type in the given address space. If true, it also returns whether the unaligned memory access is "fast" in the last argument by reference. This is used, for example, in situations where an array copy/move/set is converted to a sequence of store operations. Its use helps to ensure that such replacements don't generate code that causes an alignment error (trap) on the target machine.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 162 of file Mips16ISelLowering.cpp.

| MachineBasicBlock * Mips16TargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::MipsTargetLowering.

Definition at line 170 of file Mips16ISelLowering.cpp.

References llvm::MachineInstr::getOpcode().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1