#include <TargetLowering.h>

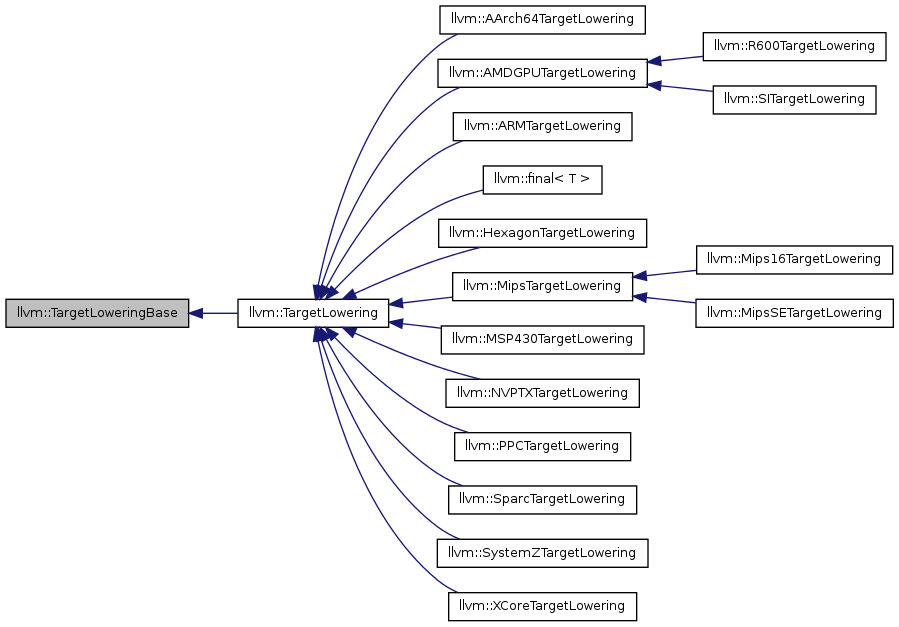

Detailed Description

This base class for TargetLowering contains the SelectionDAG-independent parts that can be used from the rest of CodeGen.

Definition at line 78 of file TargetLowering.h.

Member Typedef Documentation

| typedef std::pair<LegalizeTypeAction, EVT> llvm::TargetLoweringBase::LegalizeKind |

LegalizeKind holds the legalization kind that needs to happen to EVT in order to type-legalize it.

Definition at line 107 of file TargetLowering.h.

Member Enumeration Documentation

Enum that describes how the target represents true/false values.

Definition at line 110 of file TargetLowering.h.

This enum indicates whether operations are valid for a target, and if not, what action should be used to make them valid.

Definition at line 85 of file TargetLowering.h.

This enum indicates whether a types are legal for a target, and if not, what action should be used to make them valid.

- Enumerator:

TypeLegal TypePromoteInteger TypeExpandInteger TypeSoftenFloat TypeExpandFloat TypeScalarizeVector TypeSplitVector TypeWidenVector

Definition at line 94 of file TargetLowering.h.

Enum that describes what type of support for selects the target has.

Definition at line 117 of file TargetLowering.h.

Constructor & Destructor Documentation

| TargetLoweringBase::TargetLoweringBase | ( | const TargetMachine & | TM, |

| const TargetLoweringObjectFile * | TLOF | ||

| ) | [explicit] |

NOTE: The constructor takes ownership of TLOF.

Definition at line 688 of file TargetLoweringBase.cpp.

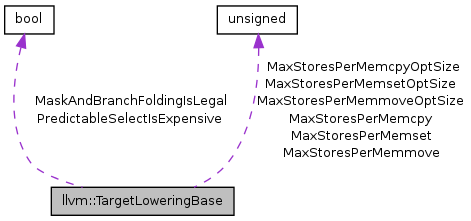

References llvm::TargetMachine::getTargetTriple(), llvm::Sched::ILP, initActions(), InitCmpLibcallCCs(), InitLibcallCallingConvs(), InitLibcallNames(), llvm::DataLayout::isLittleEndian(), MaskAndBranchFoldingIsLegal, MaxStoresPerMemcpy, MaxStoresPerMemcpyOptSize, MaxStoresPerMemmove, MaxStoresPerMemmoveOptSize, MaxStoresPerMemset, MaxStoresPerMemsetOptSize, PredictableSelectIsExpensive, and UndefinedBooleanContent.

| TargetLoweringBase::~TargetLoweringBase | ( | ) | [virtual] |

Definition at line 730 of file TargetLoweringBase.cpp.

Member Function Documentation

| void llvm::TargetLoweringBase::addBypassSlowDiv | ( | unsigned int | SlowBitWidth, |

| unsigned int | FastBitWidth | ||

| ) | [inline, protected] |

Tells the code generator which bitwidths to bypass.

Definition at line 1107 of file TargetLowering.h.

Referenced by llvm::AMDGPUTargetLowering::AMDGPUTargetLowering().

| void llvm::TargetLoweringBase::AddPromotedToType | ( | unsigned | Opc, |

| MVT | OrigVT, | ||

| MVT | DestVT | ||

| ) | [inline, protected] |

If Opc/OrigVT is specified as being promoted, the promotion code defaults to trying a larger integer/fp until it can find one that works. If that default is insufficient, this method can be used by the target to override the default.

Definition at line 1217 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::AMDGPUTargetLowering::AMDGPUTargetLowering(), llvm::MipsTargetLowering::MipsTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), and llvm::SITargetLowering::SITargetLowering().

| void llvm::TargetLoweringBase::addRegisterClass | ( | MVT | VT, |

| const TargetRegisterClass * | RC | ||

| ) | [inline, protected] |

Add the specified register class as an available regclass for the specified value type. This indicates the selector can handle values of that class natively.

Definition at line 1118 of file TargetLowering.h.

References llvm::array_lengthof(), and llvm::MVT::SimpleTy.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::MipsSETargetLowering::addMSAFloatType(), llvm::MipsSETargetLowering::addMSAIntType(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::Mips16TargetLowering::Mips16TargetLowering(), llvm::MipsSETargetLowering::MipsSETargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::SITargetLowering::SITargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

| virtual bool llvm::TargetLoweringBase::allowsMisalignedMemoryAccesses | ( | EVT | , |

| unsigned | AddrSpace = 0, |

||

| unsigned | Align = 1, |

||

| bool * | = nullptr |

||

| ) | const [inline, virtual] |

Determine if the target supports unaligned memory accesses.

This function returns true if the target allows unaligned memory accesses of the specified type in the given address space. If true, it also returns whether the unaligned memory access is "fast" in the last argument by reference. This is used, for example, in situations where an array copy/move/set is converted to a sequence of store operations. Its use helps to ensure that such replacements don't generate code that causes an alignment error (trap) on the target machine.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, llvm::SITargetLowering, llvm::MipsSETargetLowering, and llvm::Mips16TargetLowering.

Definition at line 796 of file TargetLowering.h.

Referenced by FindOptimalMemOpLowering().

| virtual bool llvm::TargetLoweringBase::allowTruncateForTailCall | ( | Type * | , |

| Type * | |||

| ) | const [inline, virtual] |

Return true if a truncation from Ty1 to Ty2 is permitted when deciding whether a call is in tail position. Typically this means that both results would be assigned to the same register or stack slot, but it could mean the target performs adequate checks of its own before proceeding with the tail call.

Reimplemented in llvm::final< T >, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1355 of file TargetLowering.h.

Referenced by getNoopInput().

| bool TargetLoweringBase::canOpTrap | ( | unsigned | Op, |

| EVT | VT | ||

| ) | const [virtual] |

Returns true if the operation can trap for the value type.

VT must be a legal type. By default, we optimistically assume most operations don't trap except for divide and remainder.

canOpTrap - Returns true if the operation can trap for the value type. VT must be a legal type.

Definition at line 870 of file TargetLoweringBase.cpp.

References llvm::ISD::FDIV, llvm::ISD::FREM, isTypeLegal(), llvm::ISD::SDIV, llvm::ISD::SREM, llvm::ISD::UDIV, and llvm::ISD::UREM.

| void llvm::TargetLoweringBase::clearOperationActions | ( | ) | [inline, protected] |

Remove all operation actions.

Definition at line 1132 of file TargetLowering.h.

| void llvm::TargetLoweringBase::clearRegisterClasses | ( | ) | [inline, protected] |

Remove all register classes.

Definition at line 1125 of file TargetLowering.h.

References llvm::MVT::LAST_VALUETYPE, and llvm::LibFunc::memset.

| void TargetLoweringBase::computeRegisterProperties | ( | ) | [protected] |

Once all of the register classes are added, this allows us to compute derived properties we expose.

computeRegisterProperties - Once all of the register classes are added, this allows us to compute derived properties we expose.

Definition at line 1026 of file TargetLoweringBase.cpp.

References llvm::MVT::f128, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, findRepresentativeClass(), llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::MVT::getPow2VectorType(), getPreferredVectorAction(), llvm::MVT::getScalarType(), llvm::MVT::getSizeInBits(), llvm::MVT::getVectorElementType(), llvm::MVT::getVectorNumElements(), getVectorTypeBreakdownMVT(), llvm::MVT::i1, llvm::MVT::i128, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::isInteger(), isTypeLegal(), llvm::MVT::isVoid, llvm::MVT::LAST_INTEGER_VALUETYPE, llvm::MVT::LAST_VALUETYPE, llvm::MVT::LAST_VECTOR_VALUETYPE, llvm_unreachable, llvm::MVT::MAX_ALLOWED_VALUETYPE, llvm::MVT::Other, llvm::MVT::ppcf128, llvm::MSP430ISD::RRC, llvm::TargetLoweringBase::ValueTypeActionImpl::setTypeAction(), TypeExpandFloat, TypeExpandInteger, TypePromoteInteger, TypeScalarizeVector, TypeSoftenFloat, TypeSplitVector, and TypeWidenVector.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::ARMTargetLowering::ARMTargetLowering(), llvm::HexagonTargetLowering::HexagonTargetLowering(), llvm::Mips16TargetLowering::Mips16TargetLowering(), llvm::MipsSETargetLowering::MipsSETargetLowering(), llvm::MSP430TargetLowering::MSP430TargetLowering(), llvm::NVPTXTargetLowering::NVPTXTargetLowering(), llvm::PPCTargetLowering::PPCTargetLowering(), llvm::R600TargetLowering::R600TargetLowering(), llvm::SITargetLowering::SITargetLowering(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), and llvm::XCoreTargetLowering::XCoreTargetLowering().

| virtual void llvm::TargetLoweringBase::emitLeadingFence | ( | IRBuilder<> & | Builder, |

| AtomicOrdering | Ord, | ||

| bool | IsStore, | ||

| bool | IsLoad | ||

| ) | const [inline, virtual] |

Inserts in the IR a target-specific intrinsic specifying a fence. It is called by AtomicExpandPass before expanding an AtomicRMW/AtomicCmpXchg/AtomicStore/AtomicLoad. RMW and CmpXchg set both IsStore and IsLoad to true. Backends with !getInsertFencesForAtomic() should keep a no-op here.

Reimplemented in llvm::ARMTargetLowering.

Definition at line 964 of file TargetLowering.h.

References getInsertFencesForAtomic().

| virtual Value* llvm::TargetLoweringBase::emitLoadLinked | ( | IRBuilder<> & | Builder, |

| Value * | Addr, | ||

| AtomicOrdering | Ord | ||

| ) | const [inline, virtual] |

Perform a load-linked operation on Addr, returning a "Value *" with the corresponding pointee type. This may entail some non-trivial operations to truncate or reconstruct types that will be illegal in the backend. See ARMISelLowering for an example implementation.

Reimplemented in llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 947 of file TargetLowering.h.

References llvm_unreachable.

| MachineBasicBlock * TargetLoweringBase::emitPatchPoint | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [protected] |

Replace/modify any TargetFrameIndex operands with a targte-dependent sequence of memory operands that is recognized by PrologEpilogInserter.

Definition at line 947 of file TargetLoweringBase.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstr::addMemOperand(), llvm::MachineInstrBuilder::addOperand(), llvm::BuildMI(), llvm::StackMaps::DirectMemRefOp, llvm::MachineInstr::eraseFromParent(), llvm::TargetSubtargetInfo::getDataLayout(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineOperand::getIndex(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::DataLayout::getPointerSize(), llvm::TargetMachine::getSubtargetImpl(), llvm::MachineBasicBlock::insert(), llvm::MachineOperand::isFI(), llvm::MachineInstr::mayLoad(), llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), llvm::MachineMemOperand::MOLoad, and llvm::MachineInstr::setMemRefs().

Referenced by llvm::AArch64TargetLowering::EmitInstrWithCustomInserter().

| virtual Value* llvm::TargetLoweringBase::emitStoreConditional | ( | IRBuilder<> & | Builder, |

| Value * | Val, | ||

| Value * | Addr, | ||

| AtomicOrdering | Ord | ||

| ) | const [inline, virtual] |

Perform a store-conditional operation to Addr. Return the status of the store. This should be 0 if the store succeeded, non-zero otherwise.

Reimplemented in llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 954 of file TargetLowering.h.

References llvm_unreachable.

| virtual void llvm::TargetLoweringBase::emitTrailingFence | ( | IRBuilder<> & | Builder, |

| AtomicOrdering | Ord, | ||

| bool | IsStore, | ||

| bool | IsLoad | ||

| ) | const [inline, virtual] |

Inserts in the IR a target-specific intrinsic specifying a fence. It is called by AtomicExpandPass after expanding an AtomicRMW/AtomicCmpXchg/AtomicStore/AtomicLoad. RMW and CmpXchg set both IsStore and IsLoad to true. Backends with !getInsertFencesForAtomic() should keep a no-op here.

Reimplemented in llvm::ARMTargetLowering.

Definition at line 974 of file TargetLowering.h.

References getInsertFencesForAtomic().

| std::pair< const TargetRegisterClass *, uint8_t > TargetLoweringBase::findRepresentativeClass | ( | MVT | VT | ) | const [protected, virtual] |

Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

findRepresentativeClass - Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

Reimplemented in llvm::final< T >, and llvm::ARMTargetLowering.

Definition at line 998 of file TargetLoweringBase.cpp.

References llvm::TargetRegisterInfo::getNumRegClasses(), llvm::TargetRegisterInfo::getRegClass(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::TargetRegisterClass::getSize(), llvm::TargetMachine::getSubtargetImpl(), getTargetMachine(), isLegalRC(), llvm::SuperRegClassIterator::isValid(), llvm::BitVector::setBitsInMask(), and llvm::MVT::SimpleTy.

Referenced by computeRegisterProperties().

| virtual bool llvm::TargetLoweringBase::GetAddrModeArguments | ( | IntrinsicInst * | , |

| SmallVectorImpl< Value * > & | , | ||

| Type *& | |||

| ) | const [inline, virtual] |

CodeGenPrepare sinks address calculations into the same BB as Load/Store instructions reading the address. This allows as much computation as possible to be done in the address mode for that operand. This hook lets targets also pass back when this should be done on intrinsics which load/store.

Definition at line 1280 of file TargetLowering.h.

| BooleanContent llvm::TargetLoweringBase::getBooleanContents | ( | bool | isVec, |

| bool | isFloat | ||

| ) | const [inline] |

For targets without i1 registers, this gives the nature of the high-bits of boolean values held in types wider than i1.

"Boolean values" are special true/false values produced by nodes like SETCC and consumed (as the condition) by nodes like SELECT and BRCOND. Not to be confused with general values promoted from i1. Some cpus distinguish between vectors of boolean and scalars; the isVec parameter selects between the two kinds. For example on X86 a scalar boolean should be zero extended from i1, while the elements of a vector of booleans should be sign extended from i1.

Some cpus also treat floating point types the same way as they treat vectors instead of the way they treat scalars.

Definition at line 296 of file TargetLowering.h.

Referenced by llvm::SelectionDAG::computeKnownBits(), llvm::SelectionDAG::ComputeNumSignBits(), llvm::SelectionDAG::FoldSetCC(), getBooleanContents(), llvm::SelectionDAG::getBoolExtOrTrunc(), llvm::SelectionDAG::getLogicalNOT(), llvm::TargetLowering::isConstFalseVal(), llvm::TargetLowering::isConstTrueVal(), and llvm::TargetLowering::SimplifySetCC().

| BooleanContent llvm::TargetLoweringBase::getBooleanContents | ( | EVT | Type | ) | const [inline] |

Definition at line 302 of file TargetLowering.h.

References getBooleanContents(), llvm::EVT::isFloatingPoint(), and llvm::EVT::isVector().

| const DenseMap<unsigned int, unsigned int>& llvm::TargetLoweringBase::getBypassSlowDivWidths | ( | ) | const [inline] |

Returns map of slow types for division or remainder with corresponding fast types

Definition at line 223 of file TargetLowering.h.

| unsigned TargetLoweringBase::getByValTypeAlignment | ( | Type * | Ty | ) | const [virtual] |

Return the desired alignment for ByVal or InAlloca aggregate function arguments in the caller parameter area. This is the actual alignment, not its logarithm.

getByValTypeAlignment - Return the desired alignment for ByVal aggregate function arguments in the caller parameter area. This is the actual alignment, not its logarithm.

Reimplemented in llvm::final< T >, and llvm::PPCTargetLowering.

Definition at line 1346 of file TargetLoweringBase.cpp.

References llvm::DataLayout::getABITypeAlignment().

Referenced by llvm::FastISel::lowerCallTo(), and llvm::TargetLowering::LowerCallTo().

| ISD::CondCode llvm::TargetLoweringBase::getCmpLibcallCC | ( | RTLIB::Libcall | Call | ) | const [inline] |

Get the CondCode that's to be used to test the result of the comparison libcall against zero.

Definition at line 1481 of file TargetLowering.h.

References llvm::Call.

Referenced by llvm::TargetLowering::softenSetCCOperands().

| MVT::SimpleValueType TargetLoweringBase::getCmpLibcallReturnType | ( | ) | const [virtual] |

Return the ValueType for comparison libcalls. Comparions libcalls include floating point comparion calls, and Ordered/Unordered check calls on floating point numbers.

Definition at line 1215 of file TargetLoweringBase.cpp.

References llvm::MVT::i32.

Referenced by llvm::TargetLowering::softenSetCCOperands().

| LegalizeAction llvm::TargetLoweringBase::getCondCodeAction | ( | ISD::CondCode | CC, |

| MVT | VT | ||

| ) | const [inline] |

Return how the condition code should be treated: either it is legal, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 604 of file TargetLowering.h.

References llvm::array_lengthof(), Promote, and llvm::MVT::SimpleTy.

Referenced by isCondCodeLegal(), and llvm::TargetLowering::SimplifySetCC().

| const DataLayout* llvm::TargetLoweringBase::getDataLayout | ( | ) | const [inline] |

Reimplemented in llvm::final< T >.

Definition at line 151 of file TargetLowering.h.

Referenced by llvm::ComputeValueVTs(), llvm::SelectionDAG::CreateStackTemporary(), llvm::XCoreSelectionDAGInfo::EmitTargetCodeForMemcpy(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), FindOptimalMemOpLowering(), llvm::SelectionDAG::getConstantPool(), llvm::SelectionDAG::getEVTAlignment(), llvm::SelectionDAG::getMemcpy(), getMemcpyLoadsAndStores(), llvm::SelectionDAG::getMemmove(), getMemmoveLoadsAndStores(), llvm::SelectionDAG::getMemset(), getMemsetStores(), llvm::NVPTXTargetLowering::getPrototype(), llvm::MSP430TargetLowering::getReturnAddressFrameIndex(), llvm::SparcTargetLowering::getSRetArgSize(), llvm::AArch64TargetLowering::getTgtMemIntrinsic(), llvm::ARMTargetLowering::getTgtMemIntrinsic(), llvm::SelectionDAG::InferPtrAlignment(), INITIALIZE_TM_PASS(), llvm::AArch64TargetLowering::isLegalAddressingMode(), IsSmallObject(), llvm::AMDGPUTargetLowering::isZExtFree(), llvm::NVPTXTargetLowering::LowerCall(), llvm::TargetLowering::LowerCallTo(), llvm::NVPTXTargetLowering::LowerFormalArguments(), llvm::NVPTXTargetLowering::LowerReturn(), llvm::MSP430TargetLowering::LowerRETURNADDR(), llvm::TargetLowering::ParseConstraints(), llvm::PPCTargetLowering::PerformDAGCombine(), llvm::FunctionLoweringInfo::set(), llvm::TargetLowering::SimplifySetCC(), llvm::SelectionDAGBuilder::visitSPDescriptorParent(), and XFormVExtractWithShuffleIntoLoad().

| unsigned llvm::TargetLoweringBase::getExceptionPointerRegister | ( | ) | const [inline] |

If a physical register, this returns the register that receives the exception address on entry to a landing pad.

Definition at line 856 of file TargetLowering.h.

Referenced by GetEHSpillList().

| unsigned llvm::TargetLoweringBase::getExceptionSelectorRegister | ( | ) | const [inline] |

If a physical register, this returns the register that receives the exception typeid on entry to a landing pad.

Definition at line 862 of file TargetLowering.h.

Referenced by GetEHSpillList().

| static ISD::NodeType llvm::TargetLoweringBase::getExtendForContent | ( | BooleanContent | Content | ) | [inline, static] |

Definition at line 125 of file TargetLowering.h.

References llvm::ISD::ANY_EXTEND, llvm_unreachable, llvm::ISD::SIGN_EXTEND, UndefinedBooleanContent, llvm::ISD::ZERO_EXTEND, ZeroOrNegativeOneBooleanContent, and ZeroOrOneBooleanContent.

Referenced by llvm::SelectionDAG::getBoolExtOrTrunc().

| LegalizeAction llvm::TargetLoweringBase::getIndexedLoadAction | ( | unsigned | IdxMode, |

| MVT | VT | ||

| ) | const [inline] |

Return how the indexed load should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 568 of file TargetLowering.h.

References llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isIndexedLoadLegal().

| LegalizeAction llvm::TargetLoweringBase::getIndexedStoreAction | ( | unsigned | IdxMode, |

| MVT | VT | ||

| ) | const [inline] |

Return how the indexed store should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 586 of file TargetLowering.h.

References llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isIndexedStoreLegal().

| bool llvm::TargetLoweringBase::getInsertFencesForAtomic | ( | ) | const [inline] |

Return whether the DAG builder should automatically insert fences and reduce ordering for atomics.

Definition at line 900 of file TargetLowering.h.

Referenced by llvm::ARMTargetLowering::emitLeadingFence(), emitLeadingFence(), llvm::ARMTargetLowering::emitTrailingFence(), and emitTrailingFence().

| unsigned llvm::TargetLoweringBase::getJumpBufAlignment | ( | ) | const [inline] |

Returns the target's jmp_buf alignment in bytes (if never set, the default is 0)

Definition at line 874 of file TargetLowering.h.

| unsigned llvm::TargetLoweringBase::getJumpBufSize | ( | ) | const [inline] |

Returns the target's jmp_buf size in bytes (if never set, the default is 200)

Definition at line 868 of file TargetLowering.h.

| CallingConv::ID llvm::TargetLoweringBase::getLibcallCallingConv | ( | RTLIB::Libcall | Call | ) | const [inline] |

Get the CallingConv that should be used for the specified libcall.

Definition at line 1491 of file TargetLowering.h.

References llvm::Call.

Referenced by llvm::XCoreSelectionDAGInfo::EmitTargetCodeForMemcpy(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), llvm::SelectionDAG::getMemcpy(), llvm::SelectionDAG::getMemmove(), llvm::SelectionDAG::getMemset(), and llvm::TargetLowering::makeLibCall().

| const char* llvm::TargetLoweringBase::getLibcallName | ( | RTLIB::Libcall | Call | ) | const [inline] |

Get the libcall routine name for the specified libcall.

Definition at line 1469 of file TargetLowering.h.

References llvm::Call.

Referenced by accumulateAndSortLibcalls(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), llvm::SelectionDAG::getMemcpy(), llvm::SelectionDAG::getMemmove(), llvm::SelectionDAG::getMemset(), isDivRemLibcallAvailable(), isSinCosLibcallAvailable(), LowerF128_FPEXTEND(), LowerF128_FPROUND(), LowerFP_TO_SINT(), LowerFP_TO_UINT(), llvm::SparcTargetLowering::LowerOperation(), LowerSINT_TO_FP(), LowerUINT_TO_FP(), llvm::TargetLowering::makeLibCall(), and llvm::SparcTargetLowering::ReplaceNodeResults().

| LegalizeAction llvm::TargetLoweringBase::getLoadExtAction | ( | unsigned | ExtType, |

| EVT | VT | ||

| ) | const [inline] |

Return how this load with extension should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 531 of file TargetLowering.h.

References Expand, llvm::EVT::getSimpleVT(), I, llvm::EVT::isExtended(), llvm::ISD::LAST_LOADEXT_TYPE, llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isLoadExtLegal().

| virtual unsigned llvm::TargetLoweringBase::getMaximalGlobalOffset | ( | ) | const [inline, virtual] |

Returns the maximal possible offset which can be used for loads / stores from the global.

Reimplemented in llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 914 of file TargetLowering.h.

Referenced by INITIALIZE_TM_PASS().

| unsigned llvm::TargetLoweringBase::getMaxStoresPerMemcpy | ( | bool | OptSize | ) | const [inline] |

Get maximum # of store operations permitted for llvm.memcpy.

This function returns the maximum number of store operations permitted to replace a call to llvm.memcpy. The value is set by the target at the performance threshold for such a replacement. If OptSize is true, return the limit for functions that have OptSize attribute.

Definition at line 773 of file TargetLowering.h.

References MaxStoresPerMemcpy, and MaxStoresPerMemcpyOptSize.

Referenced by getMemcpyLoadsAndStores().

| unsigned llvm::TargetLoweringBase::getMaxStoresPerMemmove | ( | bool | OptSize | ) | const [inline] |

Get maximum # of store operations permitted for llvm.memmove.

This function returns the maximum number of store operations permitted to replace a call to llvm.memmove. The value is set by the target at the performance threshold for such a replacement. If OptSize is true, return the limit for functions that have OptSize attribute.

Definition at line 783 of file TargetLowering.h.

References MaxStoresPerMemmove, and MaxStoresPerMemmoveOptSize.

Referenced by getMemmoveLoadsAndStores().

| unsigned llvm::TargetLoweringBase::getMaxStoresPerMemset | ( | bool | OptSize | ) | const [inline] |

Get maximum # of store operations permitted for llvm.memset.

This function returns the maximum number of store operations permitted to replace a call to llvm.memset. The value is set by the target at the performance threshold for such a replacement. If OptSize is true, return the limit for functions that have OptSize attribute.

Definition at line 763 of file TargetLowering.h.

References MaxStoresPerMemset, and MaxStoresPerMemsetOptSize.

Referenced by getMemsetStores().

| unsigned llvm::TargetLoweringBase::getMinFunctionAlignment | ( | ) | const [inline] |

Return the minimum function alignment.

Definition at line 884 of file TargetLowering.h.

Referenced by llvm::MachineFunction::MachineFunction().

| int llvm::TargetLoweringBase::getMinimumJumpTableEntries | ( | ) | const [inline] |

Return integer threshold on number of blocks to use jump tables rather than if sequence.

Definition at line 844 of file TargetLowering.h.

| unsigned llvm::TargetLoweringBase::getMinStackArgumentAlignment | ( | ) | const [inline] |

Return the minimum stack alignment of an argument.

Definition at line 879 of file TargetLowering.h.

| unsigned llvm::TargetLoweringBase::getNumRegisters | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline] |

Return the number of registers that this ValueType will eventually require.

This is one for any types promoted to live in larger registers, but may be more than one for types (like i64) that are split into pieces. For types like i140, which are first promoted then expanded, it is the number of registers needed to hold all the bits of the original type. For an i140 on a 32 bit machine this means 5 registers.

Definition at line 718 of file TargetLowering.h.

References llvm::array_lengthof(), getRegisterType(), llvm::EVT::getSimpleVT(), llvm::EVT::getSizeInBits(), llvm::MVT::getSizeInBits(), getVectorTypeBreakdown(), llvm::EVT::isInteger(), llvm::EVT::isSimple(), llvm::EVT::isVector(), llvm_unreachable, and llvm::MVT::SimpleTy.

Referenced by llvm::FunctionLoweringInfo::ComputePHILiveOutRegInfo(), llvm::FunctionLoweringInfo::CreateRegs(), GetRegistersForValue(), llvm::GetReturnInfo(), llvm::NVPTXTargetLowering::LowerCall(), llvm::FastISel::lowerCallTo(), llvm::TargetLowering::LowerCallTo(), llvm::NVPTXTargetLowering::LowerFormalArguments(), llvm::FastISel::selectExtractValue(), and llvm::FunctionLoweringInfo::set().

| const TargetLoweringObjectFile& llvm::TargetLoweringBase::getObjFileLowering | ( | ) | const [inline] |

Definition at line 152 of file TargetLowering.h.

Referenced by addPassesToGenerateCode(), llvm::TargetMachine::getNameWithPrefix(), llvm::AsmPrinter::getObjFileLowering(), llvm::TargetMachine::getSymbol(), and llvm::HexagonTargetLowering::LowerGLOBALADDRESS().

| LegalizeAction llvm::TargetLoweringBase::getOperationAction | ( | unsigned | Op, |

| EVT | VT | ||

| ) | const [inline] |

Return how this operation should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 488 of file TargetLowering.h.

References llvm::array_lengthof(), Custom, Expand, llvm::EVT::getSimpleVT(), I, llvm::EVT::isExtended(), and llvm::MVT::SimpleTy.

Referenced by getTypeToPromoteTo(), isOperationExpand(), isOperationLegal(), isOperationLegalOrCustom(), and isOperationLegalOrPromote().

| virtual EVT llvm::TargetLoweringBase::getOptimalMemOpType | ( | uint64_t | , |

| unsigned | , | ||

| unsigned | , | ||

| bool | , | ||

| bool | , | ||

| bool | , | ||

| MachineFunction & | |||

| ) | const [inline, virtual] |

Returns the target specific optimal type for load and store operations as a result of memset, memcpy, and memmove lowering.

If DstAlign is zero that means it's safe to destination alignment can satisfy any constraint. Similarly if SrcAlign is zero it means there isn't a need to check it against alignment requirement, probably because the source does not need to be loaded. If 'IsMemset' is true, that means it's expanding a memset. If 'ZeroMemset' is true, that means it's a memset of zero. 'MemcpyStrSrc' indicates whether the memcpy source is constant so it does not need to be loaded. It returns EVT::Other if the type should be determined using generic target-independent logic.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::ARMTargetLowering, and llvm::SITargetLowering.

Definition at line 814 of file TargetLowering.h.

References llvm::MVT::Other.

Referenced by FindOptimalMemOpLowering().

| unsigned TargetLoweringBase::getPointerSizeInBits | ( | uint32_t | AS = 0 | ) | const |

Definition at line 848 of file TargetLoweringBase.cpp.

References llvm::DataLayout::getPointerSizeInBits().

Referenced by getPointerTy(), and getPointerTypeSizeInBits().

| MVT TargetLoweringBase::getPointerTy | ( | uint32_t | AS = 0 | ) | const [virtual] |

Return the pointer type for the given address space, defaults to the pointer type from the data layout. FIXME: The default needs to be removed once all the code is updated.

Definition at line 844 of file TargetLoweringBase.cpp.

References llvm::MVT::getIntegerVT(), and getPointerSizeInBits().

Referenced by AddCombineToVPADDL(), addStackMapLiveVars(), CheckType(), CheckValueType(), llvm::SelectionDAG::CreateStackTemporary(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::XCoreSelectionDAGInfo::EmitTargetCodeForMemcpy(), llvm::AArch64SelectionDAGInfo::EmitTargetCodeForMemset(), llvm::X86SelectionDAGInfo::EmitTargetCodeForMemset(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), expandExp(), expandExp2(), expandPow(), ExpandUnalignedLoad(), ExpandUnalignedStore(), FindOptimalMemOpLowering(), getCopyFromParts(), GetExponent(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getMemcpy(), llvm::SelectionDAG::getMemmove(), llvm::SelectionDAG::getMemset(), getNoopInput(), llvm::TargetLowering::getPICJumpTableRelocBase(), llvm::NVPTXTargetLowering::getPrototype(), llvm::FastISel::getRegForGEPIndex(), llvm::MSP430TargetLowering::getReturnAddressFrameIndex(), llvm::ARMTargetLowering::getSetCCResultType(), getSetCCResultType(), llvm::NVPTXTargetLowering::getTgtMemIntrinsic(), llvm::SelectionDAGBuilder::getValueImpl(), getValueType(), getVectorIdxTy(), InsertFenceForAtomic(), isBLACompatibleAddress(), llvm::MSP430TargetLowering::LowerBlockAddress(), llvm::HexagonTargetLowering::LowerBlockAddress(), llvm::HexagonTargetLowering::LowerBR_JT(), llvm::HexagonTargetLowering::LowerCall(), llvm::SystemZTargetLowering::LowerCall(), llvm::NVPTXTargetLowering::LowerCall(), llvm::SparcTargetLowering::LowerCall_32(), llvm::SparcTargetLowering::LowerCall_64(), llvm::TargetLowering::LowerCallTo(), llvm::HexagonTargetLowering::LowerEH_RETURN(), LowerExtendedLoad(), llvm::MSP430TargetLowering::LowerExternalSymbol(), llvm::SparcTargetLowering::LowerF128_LibCallArg(), llvm::SparcTargetLowering::LowerF128Compare(), llvm::SparcTargetLowering::LowerF128Op(), LowerFABSorFNEG(), LowerFCOPYSIGN(), llvm::SystemZTargetLowering::LowerFormalArguments(), llvm::NVPTXTargetLowering::LowerFormalArguments(), llvm::SparcTargetLowering::LowerFormalArguments_32(), llvm::SparcTargetLowering::LowerFormalArguments_64(), LowerFSINCOS(), llvm::AMDGPUTargetLowering::LowerGlobalAddress(), llvm::MSP430TargetLowering::LowerGlobalAddress(), llvm::HexagonTargetLowering::LowerGLOBALADDRESS(), llvm::NVPTXTargetLowering::LowerGlobalAddress(), llvm::SparcTargetLowering::LowerGlobalTLSAddress(), llvm::MSP430TargetLowering::LowerJumpTable(), LowerMemOpCallTo(), llvm::SparcTargetLowering::LowerReturn_32(), llvm::MSP430TargetLowering::LowerRETURNADDR(), LowerRETURNADDR(), LowerSIGN_EXTEND_AVX512(), llvm::MSP430TargetLowering::LowerVASTART(), LowerVASTART(), LowerVectorBroadcast(), LowerZERO_EXTEND_AVX512(), llvm::SparcTargetLowering::makeAddress(), llvm::TargetLowering::makeLibCall(), llvm::PPCTargetLowering::PerformDAGCombine(), PerformEXTRACT_VECTOR_ELTCombine(), PerformLOADCombine(), PerformSTORECombine(), PrepareCall(), llvm::PPCTargetLowering::SelectAddressRegImm(), llvm::SelectionDAGISel::SelectCodeCommon(), llvm::FastISel::selectGetElementPtr(), llvm::TargetLowering::SimplifySetCC(), llvm::SparcTargetLowering::SparcTargetLowering(), llvm::SystemZTargetLowering::SystemZTargetLowering(), llvm::SelectionDAGBuilder::visitBitTestHeader(), llvm::SelectionDAGBuilder::visitJumpTable(), llvm::SelectionDAGBuilder::visitJumpTableHeader(), and llvm::SelectionDAGBuilder::visitSPDescriptorParent().

| unsigned TargetLoweringBase::getPointerTypeSizeInBits | ( | Type * | Ty | ) | const |

Definition at line 852 of file TargetLoweringBase.cpp.

References llvm::Type::getPointerAddressSpace(), getPointerSizeInBits(), and llvm::Type::isPointerTy().

Referenced by llvm::SelectionDAG::getGlobalAddress(), and llvm::SelectionDAG::InferPtrAlignment().

| virtual TargetLoweringBase::LegalizeTypeAction llvm::TargetLoweringBase::getPreferredVectorAction | ( | EVT | VT | ) | const [inline, virtual] |

Return the preferred vector type legalization action.

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::AArch64TargetLowering, and llvm::SITargetLowering.

Definition at line 191 of file TargetLowering.h.

References llvm::EVT::getVectorNumElements(), TypePromoteInteger, and TypeScalarizeVector.

Referenced by computeRegisterProperties().

| unsigned llvm::TargetLoweringBase::getPrefFunctionAlignment | ( | ) | const [inline] |

Return the preferred function alignment.

Definition at line 889 of file TargetLowering.h.

Referenced by llvm::MachineFunction::MachineFunction().

| unsigned llvm::TargetLoweringBase::getPrefLoopAlignment | ( | ) | const [inline] |

Return the preferred loop alignment.

Definition at line 894 of file TargetLowering.h.

| virtual const TargetRegisterClass* llvm::TargetLoweringBase::getRegClassFor | ( | MVT | VT | ) | const [inline, virtual] |

Return the register class that should be used for the specified value type.

Reimplemented in llvm::ARMTargetLowering.

Definition at line 320 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::FastISel::fastEmitInst_extractsubreg(), llvm::GenericScheduler::initPolicy(), llvm::SparcTargetLowering::LowerFormalArguments_64(), llvm::HexagonTargetLowering::LowerRETURNADDR(), LowerRETURNADDR(), llvm::ResourcePriorityQueue::rawRegPressureDelta(), llvm::ResourcePriorityQueue::scheduledNode(), llvm::FastISel::selectBitCast(), and llvm::FastISel::selectPatchpoint().

| MVT llvm::TargetLoweringBase::getRegisterType | ( | MVT | VT | ) | const [inline] |

Return the type of registers that this ValueType will eventually require.

Definition at line 684 of file TargetLowering.h.

References llvm::array_lengthof(), and llvm::MVT::SimpleTy.

Referenced by llvm::FunctionLoweringInfo::CreateRegs(), ExpandUnalignedLoad(), ExpandUnalignedStore(), getNumRegisters(), getRegisterType(), llvm::GetReturnInfo(), llvm::TargetLowering::getTypeForExtArgOrReturn(), getVectorTypeBreakdown(), getVectorTypeBreakdownMVT(), llvm::FastISel::lowerCallTo(), and llvm::TargetLowering::LowerCallTo().

| MVT llvm::TargetLoweringBase::getRegisterType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline] |

Return the type of registers that this ValueType will eventually require.

Definition at line 690 of file TargetLowering.h.

References llvm::array_lengthof(), getRegisterType(), llvm::EVT::getSimpleVT(), getTypeToTransformTo(), getVectorTypeBreakdown(), llvm::EVT::isInteger(), llvm::EVT::isSimple(), llvm::EVT::isVector(), llvm_unreachable, and llvm::MVT::SimpleTy.

| virtual uint8_t llvm::TargetLoweringBase::getRepRegClassCostFor | ( | MVT | VT | ) | const [inline, virtual] |

Return the cost of the 'representative' register class for the specified value type.

Definition at line 340 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by GetCostForDef().

| virtual const TargetRegisterClass* llvm::TargetLoweringBase::getRepRegClassFor | ( | MVT | VT | ) | const [inline, virtual] |

Return the 'representative' register class for the specified value type.

The 'representative' register class is the largest legal super-reg register class for the register class of the value type. For example, on i386 the rep register class for i8, i16, and i32 are GR32; while the rep register class is GR64 on x86_64.

Reimplemented in llvm::MipsSETargetLowering.

Definition at line 333 of file TargetLowering.h.

References llvm::MVT::SimpleTy.

Referenced by GetCostForDef().

| MVT TargetLoweringBase::getScalarShiftAmountTy | ( | EVT | LHSTy | ) | const [virtual] |

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::MipsTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, llvm::XCoreTargetLowering, llvm::SITargetLowering, llvm::SparcTargetLowering, and llvm::MSP430TargetLowering.

Definition at line 857 of file TargetLoweringBase.cpp.

References llvm::MVT::getIntegerVT(), and llvm::DataLayout::getPointerSize().

Referenced by getShiftAmountTy(), getVShift(), and lowerIntegerElementInsertionVectorShuffle().

| virtual int llvm::TargetLoweringBase::getScalingFactorCost | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [inline, virtual] |

Return the cost of the scaling factor used in the addressing mode represented by AM for this target, for a load/store of the specified type.

If the AM is supported, the return value must be >= 0. If the AM is not supported, it returns a negative value. TODO: Handle pre/postinc as well.

Reimplemented in llvm::final< T >, and llvm::AArch64TargetLowering.

Definition at line 1315 of file TargetLowering.h.

References isLegalAddressingMode().

| Sched::Preference llvm::TargetLoweringBase::getSchedulingPreference | ( | ) | const [inline] |

Return target scheduling preference.

Definition at line 307 of file TargetLowering.h.

Referenced by llvm::createDefaultScheduler(), llvm::PPCTargetLowering::getSchedulingPreference(), and llvm::ScheduleDAGSDNodes::newSUnit().

| virtual Sched::Preference llvm::TargetLoweringBase::getSchedulingPreference | ( | SDNode * | ) | const [inline, virtual] |

Some scheduler, e.g. hybrid, can switch to different scheduling heuristics for different nodes. This function returns the preference (or none) for the given node.

Reimplemented in llvm::PPCTargetLowering, and llvm::ARMTargetLowering.

Definition at line 314 of file TargetLowering.h.

References llvm::None.

| EVT TargetLoweringBase::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [virtual] |

Return the ValueType of the result of SETCC operations. Also used to obtain the target's preferred type for the condition operand of SELECT and BRCOND nodes. In the case of BRCOND the argument passed is MVT::Other since there are no other operands to get a type hint from.

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::ARMTargetLowering, llvm::MipsTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::SITargetLowering, llvm::SparcTargetLowering, and llvm::R600TargetLowering.

Definition at line 1210 of file TargetLoweringBase.cpp.

References getPointerTy(), llvm::EVT::isVector(), and llvm::MVT::SimpleTy.

Referenced by llvm::AMDGPUTargetLowering::LowerDIVREM24(), PerformSELECTCombine(), llvm::TargetLowering::SimplifySetCC(), llvm::TargetLowering::softenSetCCOperands(), llvm::SelectionDAGBuilder::visitBitTestCase(), llvm::SelectionDAGBuilder::visitBitTestHeader(), llvm::SelectionDAGBuilder::visitJumpTableHeader(), and llvm::SelectionDAGBuilder::visitSPDescriptorParent().

| EVT TargetLoweringBase::getShiftAmountTy | ( | EVT | LHSTy | ) | const |

Definition at line 861 of file TargetLoweringBase.cpp.

References getScalarShiftAmountTy(), llvm::EVT::isInteger(), and llvm::EVT::isVector().

Referenced by llvm::TargetLowering::BuildExactSDIV(), llvm::TargetLowering::BuildSDIV(), llvm::TargetLowering::BuildUDIV(), llvm::TargetLowering::expandFP_TO_SINT(), llvm::TargetLowering::expandMUL(), ExpandUnalignedLoad(), ExpandUnalignedStore(), llvm::SelectionDAG::getShiftAmountOperand(), LowerMUL_LOHI(), LowerVECTOR_SHUFFLEv16i8(), llvm::TargetLowering::SimplifyDemandedBits(), and llvm::TargetLowering::SimplifySetCC().

| MVT llvm::TargetLoweringBase::getSimpleValueType | ( | Type * | Ty, |

| bool | AllowUnknown = false |

||

| ) | const [inline] |

Return the MVT corresponding to this LLVM type. See getValueType.

Definition at line 674 of file TargetLowering.h.

References llvm::EVT::getSimpleVT(), and getValueType().

Referenced by llvm::TargetLowering::ParseConstraints().

| virtual bool llvm::TargetLoweringBase::getStackCookieLocation | ( | unsigned & | , |

| unsigned & | |||

| ) | const [inline, virtual] |

Return true if the target stores stack protector cookies at a fixed offset in some non-standard address space, and populates the address space and offset as appropriate.

Reimplemented in llvm::final< T >.

Definition at line 907 of file TargetLowering.h.

Referenced by CreatePrologue().

| unsigned llvm::TargetLoweringBase::getStackPointerRegisterToSaveRestore | ( | ) | const [inline] |

If a physical register, this specifies the register that llvm.savestack/llvm.restorestack should save and restore.

Definition at line 850 of file TargetLowering.h.

Referenced by llvm::TargetInstrInfo::isSchedulingBoundary(), llvm::HexagonTargetLowering::LowerDYNAMIC_STACKALLOC(), and llvm::FunctionLoweringInfo::set().

| const TargetMachine& llvm::TargetLoweringBase::getTargetMachine | ( | ) | const [inline] |

Definition at line 150 of file TargetLowering.h.

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::PPCTargetLowering::EmitAtomicBinary(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::MipsTargetLowering::EmitInstrWithCustomInserter(), llvm::ARMTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), llvm::MSP430TargetLowering::EmitShiftInstr(), llvm::SparcTargetLowering::expandAtomicRMW(), llvm::SparcTargetLowering::expandSelectCC(), findRepresentativeClass(), llvm::TargetLowering::getJumpTableEncoding(), llvm::MipsTargetLowering::getOpndList(), llvm::PPCTargetLowering::getRegForInlineAsmConstraint(), llvm::TargetLowering::getRegForInlineAsmConstraint(), llvm::ARMTargetLowering::getSchedulingPreference(), llvm::TargetLowering::isOffsetFoldingLegal(), IsSmallObject(), llvm::SystemZTargetLowering::LowerCall(), llvm::SparcTargetLowering::LowerCall_32(), llvm::SparcTargetLowering::LowerCall_64(), llvm::SITargetLowering::LowerFormalArguments(), llvm::AMDGPUTargetLowering::LowerGlobalAddress(), llvm::HexagonTargetLowering::LowerGLOBALADDRESS(), llvm::SparcTargetLowering::LowerGlobalTLSAddress(), llvm::SparcTargetLowering::makeAddress(), llvm::PPCTargetLowering::PerformDAGCombine(), llvm::SITargetLowering::PostISelFolding(), llvm::PPCTargetLowering::ReplaceNodeResults(), and llvm::SITargetLowering::shouldConvertConstantLoadToIntImm().

| virtual bool llvm::TargetLoweringBase::getTgtMemIntrinsic | ( | IntrinsicInfo & | , |

| const CallInst & | , | ||

| unsigned | |||

| ) | const [inline, virtual] |

Given an intrinsic, checks if on the target the intrinsic will need to map to a MemIntrinsicNode (touches memory). If this is the case, it returns true and store the intrinsic information into the IntrinsicInfo that was passed to the function.

Reimplemented in llvm::PPCTargetLowering, llvm::NVPTXTargetLowering, llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 450 of file TargetLowering.h.

| LegalizeAction llvm::TargetLoweringBase::getTruncStoreAction | ( | EVT | ValVT, |

| EVT | MemVT | ||

| ) | const [inline] |

Return how this store with truncation should be treated: either it is legal, needs to be promoted to a larger size, needs to be expanded to some other code sequence, or the target has a custom expander for it.

Definition at line 548 of file TargetLowering.h.

References Expand, llvm::EVT::getSimpleVT(), llvm::EVT::isExtended(), llvm::MVT::LAST_VALUETYPE, and llvm::MVT::SimpleTy.

Referenced by isTruncStoreLegal().

| LegalizeTypeAction llvm::TargetLoweringBase::getTypeAction | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline] |

Return how we should legalize values of this type, either it is already legal (return 'Legal') or we need to promote it to a larger type (return 'Promote'), or we need to expand it into multiple registers of smaller integer type (return 'Expand'). 'Custom' is not an option.

Definition at line 381 of file TargetLowering.h.

References getTypeConversion().

Referenced by llvm::SelectionDAG::getConstant(), getTypeToExpandTo(), getVectorTypeBreakdown(), and OptimizeNoopCopyExpression().

| LegalizeTypeAction llvm::TargetLoweringBase::getTypeAction | ( | MVT | VT | ) | const [inline] |

Definition at line 384 of file TargetLowering.h.

References llvm::TargetLoweringBase::ValueTypeActionImpl::getTypeAction().

| LegalizeKind llvm::TargetLoweringBase::getTypeConversion | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline] |

Definition at line 1673 of file TargetLowering.h.

References llvm::array_lengthof(), llvm::EVT::getIntegerVT(), llvm::EVT::getPow2VectorType(), llvm::EVT::getRoundIntegerType(), llvm::EVT::getSimpleVT(), llvm::EVT::getSizeInBits(), llvm::TargetLoweringBase::ValueTypeActionImpl::getTypeAction(), llvm::EVT::getVectorElementType(), llvm::MVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::MVT::getVectorVT(), llvm::EVT::isInteger(), llvm::EVT::isPow2VectorType(), llvm::isPowerOf2_32(), llvm::EVT::isSimple(), llvm::EVT::isVector(), llvm::NextPowerOf2(), llvm::MVT::SimpleTy, TypeExpandInteger, TypeLegal, TypePromoteInteger, TypeScalarizeVector, TypeSoftenFloat, TypeSplitVector, and TypeWidenVector.

Referenced by getTypeAction(), getTypeLegalizationCost(), and getTypeToTransformTo().

| std::pair< unsigned, MVT > TargetLoweringBase::getTypeLegalizationCost | ( | Type * | Ty | ) | const |

Estimate the cost of type-legalization and the legalized type.

Definition at line 1426 of file TargetLoweringBase.cpp.

References llvm::CallingConv::C, llvm::Type::getContext(), llvm::EVT::getSimpleVT(), getTypeConversion(), getValueType(), TypeExpandInteger, TypeLegal, and TypeSplitVector.

| EVT llvm::TargetLoweringBase::getTypeToExpandTo | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline] |

For types supported by the target, this is an identity function. For types that must be expanded (i.e. integer types that are larger than the largest integer register or illegal floating point types), this returns the largest legal type it will be expanded to.

Definition at line 402 of file TargetLowering.h.

References getTypeAction(), getTypeToTransformTo(), llvm::EVT::isVector(), llvm_unreachable, TypeExpandInteger, and TypeLegal.

| MVT llvm::TargetLoweringBase::getTypeToPromoteTo | ( | unsigned | Op, |

| MVT | VT | ||

| ) | const [inline] |

If the action for this operation is to promote, this method returns the ValueType to promote to.

Definition at line 626 of file TargetLowering.h.

References getOperationAction(), llvm::MVT::isFloatingPoint(), llvm::MVT::isInteger(), isTypeLegal(), llvm::MVT::isVoid, Promote, and llvm::MVT::SimpleTy.

| EVT llvm::TargetLoweringBase::getTypeToTransformTo | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline] |

For types supported by the target, this is an identity function. For types that must be promoted to larger types, this returns the larger type to promote to. For integer types that are larger than the largest integer register, this contains one step in the expansion to get to the smaller register. For illegal floating point types, this returns the integer type to transform to.

Definition at line 394 of file TargetLowering.h.

References getTypeConversion().

Referenced by llvm::FunctionLoweringInfo::ComputePHILiveOutRegInfo(), llvm::SelectionDAG::getConstant(), getMemcpyLoadsAndStores(), llvm::FastISel::getRegForValue(), getRegisterType(), llvm::SelectionDAG::GetSplitDestVTs(), getTypeToExpandTo(), getVectorTypeBreakdown(), OptimizeNoopCopyExpression(), and llvm::FastISel::selectBinaryOp().

| EVT llvm::TargetLoweringBase::getValueType | ( | Type * | Ty, |

| bool | AllowUnknown = false |

||

| ) | const [inline] |

Return the EVT corresponding to this LLVM type. This is fixed by the LLVM operations except for the pointer size. If AllowUnknown is true, this will return MVT::Other for types with no EVT counterpart (e.g. structs), otherwise it will assert.

Definition at line 653 of file TargetLowering.h.

References llvm::Type::getContext(), llvm::SequentialType::getElementType(), llvm::EVT::getEVT(), llvm::VectorType::getNumElements(), getPointerTy(), llvm::EVT::getTypeForEVT(), llvm::EVT::getVectorVT(), and llvm::Type::isVectorTy().

Referenced by CompactSwizzlableVector(), llvm::ComputeValueVTs(), llvm::NVPTXTargetLowering::getPrototype(), llvm::FastISel::getRegForValue(), getSimpleValueType(), llvm::NVPTXTargetLowering::getTgtMemIntrinsic(), getTypeLegalizationCost(), llvm::SelectionDAGBuilder::getValueImpl(), llvm::ARMTargetLowering::isLegalAddressingMode(), llvm::NVPTXTargetLowering::LowerCall(), llvm::TargetLowering::LowerCallTo(), llvm::NVPTXTargetLowering::LowerFormalArguments(), llvm::NVPTXTargetLowering::LowerReturn(), OptimizeExtractBits(), OptimizeNoopCopyExpression(), llvm::FastISel::selectBitCast(), llvm::FastISel::selectCast(), llvm::FastISel::selectExtractValue(), llvm::FastISel::selectFNeg(), and llvm::FastISel::selectOperator().

| const ValueTypeActionImpl& llvm::TargetLoweringBase::getValueTypeActions | ( | ) | const [inline] |

Definition at line 373 of file TargetLowering.h.

| virtual MVT llvm::TargetLoweringBase::getVectorIdxTy | ( | ) | const [inline, virtual] |

Returns the type to be used for the index operand of: ISD::INSERT_VECTOR_ELT, ISD::EXTRACT_VECTOR_ELT, ISD::INSERT_SUBVECTOR, and ISD::EXTRACT_SUBVECTOR

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 170 of file TargetLowering.h.

References getPointerTy().

Referenced by BuildVectorFromScalar(), llvm::SelectionDAG::ExtractVectorElements(), getCopyFromPartsVector(), llvm::SelectionDAG::SplitVector(), and llvm::SelectionDAG::UnrollVectorOp().

| unsigned TargetLoweringBase::getVectorTypeBreakdown | ( | LLVMContext & | Context, |

| EVT | VT, | ||

| EVT & | IntermediateVT, | ||

| unsigned & | NumIntermediates, | ||

| MVT & | RegisterVT | ||

| ) | const |

Vector types are broken down into some number of legal first class types. For example, EVT::v8f32 maps to 2 EVT::v4f32 with Altivec or SSE1, or 8 promoted EVT::f64 values with the X86 FP stack. Similarly, EVT::v2i64 turns into 4 EVT::i32 values with both PPC and X86.

This method returns the number of registers needed, and the VT for each register. It also returns the VT and quantity of the intermediate values before they are promoted/expanded.

getVectorTypeBreakdown - Vector types are broken down into some number of legal first class types. For example, MVT::v8f32 maps to 2 MVT::v4f32 with Altivec or SSE1, or 8 promoted MVT::f64 values with the X86 FP stack. Similarly, MVT::v2i64 turns into 4 MVT::i32 values with both PPC and X86.

This method returns the number of registers needed, and the VT for each register. It also returns the VT and quantity of the intermediate values before they are promoted/expanded.

Definition at line 1228 of file TargetLoweringBase.cpp.

References getRegisterType(), llvm::EVT::getSimpleVT(), llvm::EVT::getSizeInBits(), llvm::MVT::getSizeInBits(), getTypeAction(), getTypeToTransformTo(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::isPowerOf2_32(), isTypeLegal(), llvm::NextPowerOf2(), llvm::X86II::TA, TypePromoteInteger, and TypeWidenVector.

Referenced by getCopyFromPartsVector(), getNumRegisters(), and getRegisterType().

| bool llvm::TargetLoweringBase::hasBigEndianPartOrdering | ( | EVT | VT | ) | const [inline] |

When splitting a value of the specified type into parts, does the Lo or Hi part come first? This usually follows the endianness, except for ppcf128, where the Hi part always comes first.

Definition at line 746 of file TargetLowering.h.

References isBigEndian(), and llvm::MVT::ppcf128.

Referenced by getCopyFromParts().

| bool llvm::TargetLoweringBase::hasExtractBitsInsn | ( | ) | const [inline] |

Return true if the target has BitExtract instructions.

Definition at line 187 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::hasFloatingPointExceptions | ( | ) | const [inline] |

Return true if target supports floating point exceptions.

Definition at line 267 of file TargetLowering.h.

Referenced by llvm::SelectionDAG::getNode().

| virtual bool llvm::TargetLoweringBase::hasLoadLinkedStoreConditional | ( | ) | const [inline, virtual] |

True if AtomicExpandPass should use emitLoadLinked/emitStoreConditional and expand AtomicCmpXchgInst.

Reimplemented in llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 941 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::hasMultipleConditionRegisters | ( | ) | const [inline] |

Return true if multiple condition registers are available.

Definition at line 182 of file TargetLowering.h.

| virtual bool llvm::TargetLoweringBase::hasPairedLoad | ( | Type * | , |

| unsigned & | |||

| ) | const [inline, virtual] |

Return true if the target supplies and combines to a paired load two loaded values of type LoadedType next to each other in memory. RequiredAlignment gives the minimal alignment constraints that must be met to be able to select this paired load.

This information is *not* used to generate actual paired loads, but it is used to generate a sequence of loads that is easier to combine into a paired load. For instance, something like this: a = load i64* addr b = trunc i64 a to i32 c = lshr i64 a, 32 d = trunc i64 c to i32 will be optimized into: b = load i32* addr1 d = load i32* addr2 Where addr1 = addr2 +/- sizeof(i32).

In other words, unless the target performs a post-isel load combining, this information should not be provided because it will generate more loads.

Reimplemented in llvm::AArch64TargetLowering.

Definition at line 1400 of file TargetLowering.h.

| virtual bool llvm::TargetLoweringBase::hasPairedLoad | ( | EVT | , |

| unsigned & | |||

| ) | const [inline, virtual] |

Reimplemented in llvm::AArch64TargetLowering.

Definition at line 1405 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::hasTargetDAGCombine | ( | ISD::NodeType | NT | ) | const [inline] |

If true, the target has custom DAG combine transformations that it can perform for the specified node.

Definition at line 752 of file TargetLowering.h.

References llvm::array_lengthof().

| void TargetLoweringBase::initActions | ( | ) | [protected] |

Initialize all of the actions to default values.

Definition at line 734 of file TargetLoweringBase.cpp.

References llvm::ISD::ANY_EXTEND_VECTOR_INREG, llvm::array_lengthof(), llvm::ISD::ATOMIC_CMP_SWAP_WITH_SUCCESS, llvm::ISD::CONCAT_VECTORS, llvm::ISD::ConstantFP, llvm::ISD::DEBUGTRAP, Expand, llvm::MVT::f128, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::MVT::f80, llvm::ISD::FCEIL, llvm::ISD::FCOPYSIGN, llvm::ISD::FEXP, llvm::ISD::FEXP2, llvm::ISD::FFLOOR, llvm::ISD::FGETSIGN, llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::ISD::FLOG, llvm::ISD::FLOG10, llvm::ISD::FLOG2, llvm::ISD::FNEARBYINT, llvm::ISD::FRINT, llvm::ISD::FROUND, llvm::ISD::FTRUNC, llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VALUETYPE, llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::LibFunc::memset, llvm::MVT::Other, llvm::ISD::PRE_INC, llvm::ISD::PREFETCH, setIndexedLoadAction(), setIndexedStoreAction(), setOperationAction(), llvm::ISD::SIGN_EXTEND_VECTOR_INREG, llvm::ISD::TRAP, and llvm::ISD::ZERO_EXTEND_VECTOR_INREG.

Referenced by TargetLoweringBase().

| int TargetLoweringBase::InstructionOpcodeToISD | ( | unsigned | Opcode | ) | const |

Get the ISD node that corresponds to the Instruction class opcode.

Definition at line 1354 of file TargetLoweringBase.cpp.

References ADD, llvm::AddrSpaceCast, llvm::ISD::ADDRSPACECAST, llvm::Alloca, AND, llvm::APIntOps::And(), llvm::ISD::BITCAST, llvm::Call, llvm::ISD::EXTRACT_VECTOR_ELT, ExtractElement(), llvm::ExtractValue, llvm::ISD::FADD, llvm::FCmp, llvm::ISD::FDIV, llvm::ISD::FMUL, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::FPExt, llvm::FPToSI, llvm::ISD::FREM, llvm::ISD::FSUB, llvm::ISD::INSERT_VECTOR_ELT, llvm::InsertElement, llvm::IntToPtr, llvm::LandingPad, llvm_unreachable, llvm::SPII::Load, llvm::ISD::LOAD, llvm::LShr, llvm::ISD::MERGE_VALUES, llvm::ISD::MUL, OR, llvm::APIntOps::Or(), llvm::TargetOpcode::PHI, llvm::MipsISD::Ret, llvm::ISD::SDIV, llvm::MCID::Select, llvm::ISD::SELECT, llvm::ISD::SETCC, llvm::SExt, llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND, llvm::ISD::SINT_TO_FP, llvm::SIToFP, llvm::ISD::SRA, llvm::ISD::SREM, llvm::ISD::SRL, llvm::SPII::Store, llvm::ISD::STORE, SUB, llvm::Trunc, llvm::ISD::TRUNCATE, llvm::ISD::UDIV, llvm::ISD::UINT_TO_FP, llvm::ISD::UREM, llvm::UserOp1, llvm::VAArg, llvm::ISD::VECTOR_SHUFFLE, XOR, llvm::APIntOps::Xor(), and llvm::ISD::ZERO_EXTEND.

Referenced by SinkShiftAndTruncate().

| bool llvm::TargetLoweringBase::isBigEndian | ( | ) | const [inline] |

Definition at line 154 of file TargetLowering.h.

Referenced by ExpandBITCAST(), llvm::SelectionDAG::getConstant(), getCopyFromParts(), getCopyToParts(), hasBigEndianPartOrdering(), isExtendedBUILD_VECTOR(), isNEONModifiedImm(), PerformSTORECombine(), PerformVMOVRRDCombine(), and SkipExtensionForVMULL().

| bool llvm::TargetLoweringBase::isCondCodeLegal | ( | ISD::CondCode | CC, |

| MVT | VT | ||

| ) | const [inline] |

Return true if the specified condition code is legal on this target.

Definition at line 617 of file TargetLowering.h.

References Custom, getCondCodeAction(), and Legal.

Referenced by llvm::SelectionDAG::FoldSetCC(), llvm::R600TargetLowering::PerformDAGCombine(), and llvm::TargetLowering::SimplifySetCC().

| virtual bool llvm::TargetLoweringBase::isFAbsFree | ( | EVT | VT | ) | const [inline, virtual] |

Return true if an fabs operation is free to the point where it is never worthwhile to replace it with a bitwise operation.

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 1426 of file TargetLowering.h.

References llvm::EVT::isFloatingPoint().

| virtual bool llvm::TargetLoweringBase::isFMAFasterThanFMulAndFAdd | ( | EVT | ) | const [inline, virtual] |

Return true if an FMA operation is faster than a pair of fmul and fadd instructions. fmuladd intrinsics will be expanded to FMAs when this method returns true, otherwise fmuladd is expanded to fmul + fadd.

NOTE: This may be called before legalization on types for which FMAs are not legal, but should return true if those types will eventually legalize to types that support FMAs. After legalization, it will only be called on types that support FMAs (via Legal or Custom actions)

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::NVPTXTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, and llvm::SITargetLowering.

Definition at line 1439 of file TargetLowering.h.

| virtual bool llvm::TargetLoweringBase::isFNegFree | ( | EVT | VT | ) | const [inline, virtual] |

Return true if an fneg operation is free to the point where it is never worthwhile to replace it with a bitwise operation.

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 1419 of file TargetLowering.h.

References llvm::EVT::isFloatingPoint().

| virtual bool llvm::TargetLoweringBase::isFPImmLegal | ( | const APFloat & | , |

| EVT | |||

| ) | const [inline, virtual] |

Returns true if the target can instruction select the specified FP immediate natively. If false, the legalizer will materialize the FP immediate as a load from a constant pool.

Reimplemented in llvm::final< T >, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, and llvm::AMDGPUTargetLowering.

Definition at line 458 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::isIndexedLoadLegal | ( | unsigned | IdxMode, |

| EVT | VT | ||

| ) | const [inline] |

Return true if the specified indexed load is legal on this target.

Definition at line 576 of file TargetLowering.h.

References Custom, getIndexedLoadAction(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and Legal.

| bool llvm::TargetLoweringBase::isIndexedStoreLegal | ( | unsigned | IdxMode, |

| EVT | VT | ||

| ) | const [inline] |

Return true if the specified indexed load is legal on this target.

Definition at line 594 of file TargetLowering.h.

References Custom, getIndexedStoreAction(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and Legal.

| bool llvm::TargetLoweringBase::isIntDivCheap | ( | ) | const [inline] |

Return true if integer divide is usually cheaper than a sequence of several shifts, adds, and multiplies for this target.

Definition at line 216 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::isJumpExpensive | ( | ) | const [inline] |

Return true if Flow Control is an expensive operation that should be avoided.

Definition at line 232 of file TargetLowering.h.

| virtual bool llvm::TargetLoweringBase::isLegalAddImmediate | ( | int64_t | ) | const [inline, virtual] |

Return true if the specified immediate is legal add immediate, that is the target has add instructions which can add a register with the immediate without having to materialize the immediate into a register.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 1331 of file TargetLowering.h.

| bool TargetLoweringBase::isLegalAddressingMode | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [virtual] |

Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

The type may be VoidTy, in which case only return true if the addressing mode is legal for a load/store of any legal type. TODO: Handle pre/postinc as well.

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::XCoreTargetLowering, and llvm::SITargetLowering.

Definition at line 1454 of file TargetLoweringBase.cpp.

References llvm::TargetLoweringBase::AddrMode::BaseGV, llvm::TargetLoweringBase::AddrMode::BaseOffs, llvm::TargetLoweringBase::AddrMode::HasBaseReg, and llvm::TargetLoweringBase::AddrMode::Scale.

Referenced by canFoldInAddressingMode(), and getScalingFactorCost().

| virtual bool llvm::TargetLoweringBase::isLegalICmpImmediate | ( | int64_t | ) | const [inline, virtual] |

Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1324 of file TargetLowering.h.

Referenced by llvm::TargetLowering::SimplifySetCC().

| bool TargetLoweringBase::isLegalRC | ( | const TargetRegisterClass * | RC | ) | const [protected] |

Return true if the value types that can be represented by the specified register class are all legal.

isLegalRC - Return true if the value types that can be represented by the specified register class are all legal.

Definition at line 935 of file TargetLoweringBase.cpp.

References I, isTypeLegal(), llvm::TargetRegisterClass::vt_begin(), and llvm::TargetRegisterClass::vt_end().

Referenced by findRepresentativeClass(), and llvm::TargetLowering::getRegForInlineAsmConstraint().

| bool llvm::TargetLoweringBase::isLittleEndian | ( | ) | const [inline] |

Definition at line 155 of file TargetLowering.h.

Referenced by llvm::ARMTargetLowering::allowsMisalignedMemoryAccesses(), ExpandUnalignedLoad(), ExpandUnalignedStore(), getMemsetStringVal(), ShrinkLoadReplaceStoreWithStore(), and llvm::TargetLowering::SimplifySetCC().

| virtual bool llvm::TargetLoweringBase::isLoadBitCastBeneficial | ( | EVT | , |

| EVT | |||

| ) | const [inline, virtual] |

isLoadBitCastBeneficial() - Return true if the following transform is beneficial. fold (conv (load x)) -> (load (conv*)x) On architectures that don't natively support some vector loads efficiently, casting the load to a smaller vector of larger types and loading is more efficient, however, this can be undone by optimizations in dag combiner.

Reimplemented in llvm::AMDGPUTargetLowering.

Definition at line 247 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::isLoadExtLegal | ( | unsigned | ExtType, |

| EVT | VT | ||

| ) | const [inline] |

Return true if the specified load with extension is legal on this target.

Definition at line 540 of file TargetLowering.h.

References getLoadExtAction(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and Legal.

| bool llvm::TargetLoweringBase::isMaskAndBranchFoldingLegal | ( | ) | const [inline] |

Return if the target supports combining a chain like:

%andResult = and %val1, #imm-with-one-bit-set;

%icmpResult = icmp %andResult, 0

br i1 %icmpResult, label %dest1, label %dest2

into a single machine instruction of a form like:

brOnBitSet %register, #bitNumber, dest

Definition at line 262 of file TargetLowering.h.

References MaskAndBranchFoldingIsLegal.

| virtual bool llvm::TargetLoweringBase::isNarrowingProfitable | ( | EVT | , |

| EVT | |||

| ) | const [inline, virtual] |

Return true if it's profitable to narrow operations of type VT1 to VT2. e.g. on x86, it's profitable to narrow from i32 to i8 but not from i32 to i16.

Reimplemented in llvm::final< T >, and llvm::AMDGPUTargetLowering.

Definition at line 1446 of file TargetLowering.h.

| virtual bool llvm::TargetLoweringBase::isNoopAddrSpaceCast | ( | unsigned | SrcAS, |

| unsigned | DestAS | ||

| ) | const [inline, virtual] |

Returns true if a cast between SrcAS and DestAS is a noop.

Reimplemented in llvm::final< T >, llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 919 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::isOperationExpand | ( | unsigned | Op, |

| EVT | VT | ||

| ) | const [inline] |

Return true if the specified operation is illegal on this target or unlikely to be made legal with custom lowering. This is used to help guide high-level lowering decisions.

Definition at line 518 of file TargetLowering.h.

References Expand, getOperationAction(), and isTypeLegal().

| bool llvm::TargetLoweringBase::isOperationLegal | ( | unsigned | Op, |

| EVT | VT | ||

| ) | const [inline] |

Return true if the specified operation is legal on this target.

Definition at line 523 of file TargetLowering.h.

References getOperationAction(), isTypeLegal(), Legal, and llvm::MVT::Other.

Referenced by llvm::TargetLowering::BuildSDIV(), llvm::TargetLowering::BuildUDIV(), EltsFromConsecutiveLoads(), llvm::R600TargetLowering::PerformDAGCombine(), PerformShuffleCombine(), llvm::TargetLowering::SimplifySetCC(), and tryFoldToZero().

| bool llvm::TargetLoweringBase::isOperationLegalOrCustom | ( | unsigned | Op, |

| EVT | VT | ||

| ) | const [inline] |

Return true if the specified operation is legal on this target or can be made legal with custom lowering. This is used to help guide high-level lowering decisions.

Definition at line 500 of file TargetLowering.h.

References Custom, getOperationAction(), isTypeLegal(), Legal, and llvm::MVT::Other.

Referenced by areJTsAllowed(), buildFromShuffleMostly(), llvm::TargetLowering::BuildSDIV(), llvm::TargetLowering::BuildUDIV(), llvm::TargetLowering::expandMUL(), FindOptimalMemOpLowering(), isNegatibleForFree(), LowerExtendedLoad(), PerformSELECTCombine(), llvm::TargetLowering::SimplifyDemandedBits(), SinkShiftAndTruncate(), and XFormVExtractWithShuffleIntoLoad().

| bool llvm::TargetLoweringBase::isOperationLegalOrPromote | ( | unsigned | Op, |

| EVT | VT | ||

| ) | const [inline] |

Return true if the specified operation is legal on this target or can be made legal using promotion. This is used to help guide high-level lowering decisions.

Definition at line 509 of file TargetLowering.h.

References getOperationAction(), isTypeLegal(), Legal, llvm::MVT::Other, and Promote.

Referenced by WidenMaskArithmetic().

| bool llvm::TargetLoweringBase::isPow2SDivCheap | ( | ) | const [inline] |

Return true if pow2 sdiv is cheaper than a chain of sra/srl/add/sra.

Definition at line 228 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::isPredictableSelectExpensive | ( | ) | const [inline] |

Return true if selects are only cheaper than branches if the branch is unlikely to be predicted right.

Definition at line 236 of file TargetLowering.h.

References PredictableSelectIsExpensive.

| virtual bool llvm::TargetLoweringBase::isSafeMemOpType | ( | MVT | ) | const [inline, virtual] |

Returns true if it's safe to use load / store of the specified type to expand memcpy / memset inline.

This is mostly true for all types except for some special cases. For example, on X86 targets without SSE2 f64 load / store are done with fldl / fstpl which also does type conversion. Note the specified type doesn't have to be legal as the hook is used before type legalization.

Reimplemented in llvm::final< T >.

Definition at line 830 of file TargetLowering.h.

Referenced by FindOptimalMemOpLowering().

| bool llvm::TargetLoweringBase::isSelectExpensive | ( | ) | const [inline] |

Return true if the select operation is expensive for this target.

Definition at line 175 of file TargetLowering.h.

| virtual bool llvm::TargetLoweringBase::isSelectSupported | ( | SelectSupportKind | ) | const [inline, virtual] |

Reimplemented in llvm::ARMTargetLowering, and llvm::AMDGPUTargetLowering.

Definition at line 177 of file TargetLowering.h.

| virtual bool llvm::TargetLoweringBase::isShuffleMaskLegal | ( | const SmallVectorImpl< int > & | , |

| EVT | |||

| ) | const [inline, virtual] |

Targets can use this to indicate that they only support *some* VECTOR_SHUFFLE operations, those with specific masks. By default, if a target supports the VECTOR_SHUFFLE node, all mask values are assumed to be legal.

Reimplemented in llvm::final< T >, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, and llvm::MipsSETargetLowering.

Definition at line 466 of file TargetLowering.h.

Referenced by ExpandBVWithShuffles().

| bool llvm::TargetLoweringBase::isSlowDivBypassed | ( | ) | const [inline] |

Returns true if target has indicated at least one type should be bypassed.

Definition at line 219 of file TargetLowering.h.

References llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::empty().

| virtual bool llvm::TargetLoweringBase::isTruncateFree | ( | Type * | , |

| Type * | |||

| ) | const [inline, virtual] |

Return true if it's free to truncate a value of type Ty1 to type Ty2. e.g. On x86 it's free to truncate a i32 value in register EAX to i16 by referencing its sub-register AX.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, llvm::AMDGPUTargetLowering, llvm::MSP430TargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1346 of file TargetLowering.h.

Referenced by ExtendUsesToFormExtLoad(), getMemsetStores(), and llvm::TargetLowering::TargetLoweringOpt::ShrinkDemandedOp().

| virtual bool llvm::TargetLoweringBase::isTruncateFree | ( | EVT | , |

| EVT | |||

| ) | const [inline, virtual] |

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, llvm::AMDGPUTargetLowering, llvm::MSP430TargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1359 of file TargetLowering.h.

| bool llvm::TargetLoweringBase::isTruncStoreLegal | ( | EVT | ValVT, |

| EVT | MemVT | ||

| ) | const [inline] |

Return true if the specified store with truncation is legal on this target.

Definition at line 559 of file TargetLowering.h.

References llvm::EVT::getSimpleVT(), getTruncStoreAction(), llvm::EVT::isSimple(), isTypeLegal(), and Legal.

| bool llvm::TargetLoweringBase::isTypeLegal | ( | EVT | VT | ) | const [inline] |

Return true if the target has native support for the specified value type. This means that it has a register that directly holds it without promotions or expansions.

Definition at line 347 of file TargetLowering.h.

References llvm::array_lengthof(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and llvm::MVT::SimpleTy.