8

|

User Manual - «Covered» |

Finite state machine (FSM) coverage answers the question, "Did I reach all of the states and traverse all possible paths through a given state machine?"

There are two types of coverage detail for FSMs that Covered can handle:

- State coverage - answers the question "Were all states of an FSM hit during simulation?"

- State transition coverage - answers the question "Did the FSM transition between all states (that are achievable) in simulation?"

Example

Suppose the DUT comprised of the following finite state machine.

module test( clock );

input clock;

reg [1:0] state;

reg req, gnt;

parameter IDLE 2'b00;

parameter REQ 2'b01;

parameter WAIT 2'b10;

parameter GNT 2'b11;

initial

begin

req = 1'b0;

gnt = 1'b0;

repeat(4) @(posedge clock);

req <= 1'b1;

@(posedge clock);

req <= 1'b0;

gnt <= 1'b1;

@(posedge clock);

gnt <= 1'b0;

repeat(2) @(posedge clock);

end

always @(posedge clock)

case( state )

IDLE : state <= req ? REQ : IDLE;

REQ : state <= gnt ? GNT : WAIT;

WAIT : state <= gnt ? GNT : WAIT;

GNT : state <= IDLE;

default : state <= 2'bx;

endcase

endmodule

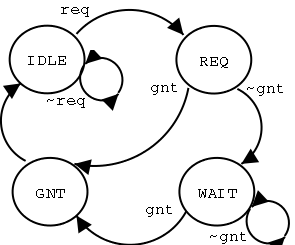

To help visualize this state machine, let's also display it as a digraph.

This state machine has four states: IDLE, REQ, WAIT, GNT. During simulation, 75% of the states were hit (3 out of 4) including IDLE, REQ and GNT. You can see that the WAIT state was never hit during simulation since the gnt signal was asserted the clock period after the req signal asserted.

Additionally, this state machine contains 7 state "arcs" which are represented in the digraph as arrowed lines. They are the following:

- IDLE -> IDLE (HIT)

- IDLE -> REQ (HIT)

- REQ -> WAIT (MISSED)

- REQ -> GNT (HIT)

- WAIT -> WAIT (MISSED)

- WAIT -> GNT (MISSED)

- GNT -> IDLE (HIT)

Counting the number of traversed arcs during simulation, we can see that we have covered 4 out of 7 (or 57%) of the possible arcs in this state machine.

Recommendations

For a design to pass full coverage, it is recommended that the FSM coverage for all finite state machines in the design to receive 100% coverage for the state coverage and 100% for all achievable state transitions. Since Covered will not determine which state transitions are achievable, it is up to the verification engineer to examine the executed state transitions to determine if 100% of possible transitions occurred.

[ 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 ]

License: GPL

This Manual was originally created with ManStyle.