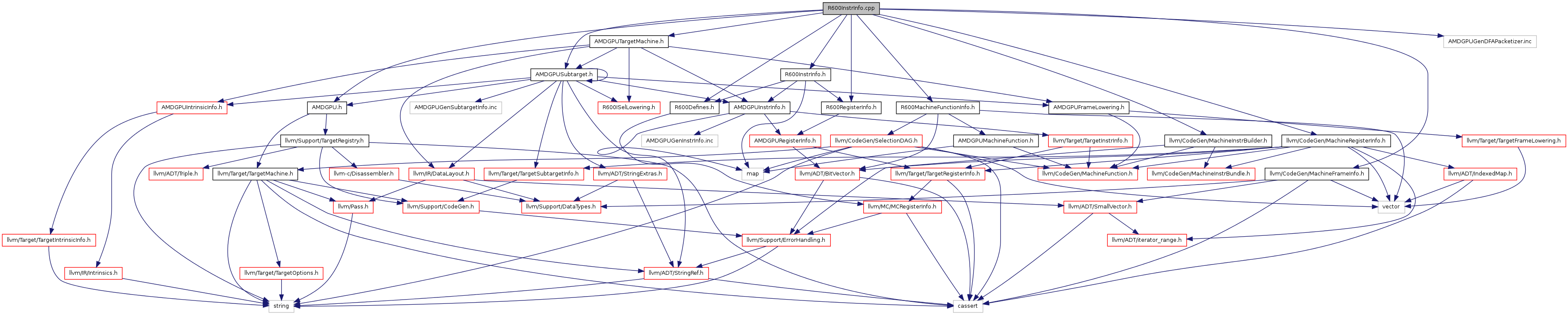

R600 Implementation of TargetInstrInfo. More...

#include "R600InstrInfo.h"#include "AMDGPU.h"#include "AMDGPUSubtarget.h"#include "AMDGPUTargetMachine.h"#include "R600Defines.h"#include "R600MachineFunctionInfo.h"#include "R600RegisterInfo.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "AMDGPUGenDFAPacketizer.inc"

Go to the source code of this file.

Defines | |

| #define | GET_INSTRINFO_CTOR_DTOR |

| #define | SRC_SEL_ROWS 11 |

| #define | OPERAND_CASE(Label) |

Functions | |

| static std::vector< std::pair < int, unsigned > > | Swizzle (std::vector< std::pair< int, unsigned > > Src, R600InstrInfo::BankSwizzle Swz) |

| static unsigned | getTransSwizzle (R600InstrInfo::BankSwizzle Swz, unsigned Op) |

| static bool | NextPossibleSolution (std::vector< R600InstrInfo::BankSwizzle > &SwzCandidate, unsigned Idx) |

| static bool | isConstCompatible (R600InstrInfo::BankSwizzle TransSwz, const std::vector< std::pair< int, unsigned > > &TransOps, unsigned ConstCount) |

| static bool | isPredicateSetter (unsigned Opcode) |

| static MachineInstr * | findFirstPredicateSetterFrom (MachineBasicBlock &MBB, MachineBasicBlock::iterator I) |

| static bool | isJump (unsigned Opcode) |

| static bool | isBranch (unsigned Opcode) |

| static MachineBasicBlock::iterator | FindLastAluClause (MachineBasicBlock &MBB) |

| static unsigned | getSlotedOps (unsigned Op, unsigned Slot) |

Detailed Description

R600 Implementation of TargetInstrInfo.

Definition in file R600InstrInfo.cpp.

Define Documentation

| #define GET_INSTRINFO_CTOR_DTOR |

Definition at line 28 of file R600InstrInfo.cpp.

| #define OPERAND_CASE | ( | Label | ) |

case Label: { \ static const unsigned Ops[] = \ { \ Label##_X, \ Label##_Y, \ Label##_Z, \ Label##_W \ }; \ return Ops[Slot]; \ }

Definition at line 1227 of file R600InstrInfo.cpp.

Referenced by getSlotedOps().

| #define SRC_SEL_ROWS 11 |

Definition at line 271 of file R600InstrInfo.cpp.

Referenced by llvm::R600InstrInfo::getSelIdx().

Function Documentation

| static MachineInstr* findFirstPredicateSetterFrom | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I | ||

| ) | [static] |

Definition at line 675 of file R600InstrInfo.cpp.

References llvm::MachineBasicBlock::begin(), llvm::MachineInstr::getOpcode(), I, isPredicateSetter(), and llvm::AArch64CC::MI.

Referenced by llvm::R600InstrInfo::InsertBranch(), and llvm::R600InstrInfo::RemoveBranch().

| static MachineBasicBlock::iterator FindLastAluClause | ( | MachineBasicBlock & | MBB | ) | [static] |

Definition at line 776 of file R600InstrInfo.cpp.

References llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::rbegin(), and llvm::MachineBasicBlock::rend().

Referenced by llvm::R600InstrInfo::InsertBranch(), and llvm::R600InstrInfo::RemoveBranch().

| static unsigned getSlotedOps | ( | unsigned | Op, |

| unsigned | Slot | ||

| ) | [static] |

Definition at line 1239 of file R600InstrInfo.cpp.

References llvm_unreachable, OPERAND_CASE, and llvm::LibFunc::write.

Referenced by llvm::R600InstrInfo::buildSlotOfVectorInstruction().

| static unsigned getTransSwizzle | ( | R600InstrInfo::BankSwizzle | Swz, |

| unsigned | Op | ||

| ) | [static] |

Definition at line 419 of file R600InstrInfo.cpp.

References llvm::R600InstrInfo::ALU_VEC_012_SCL_210, llvm::R600InstrInfo::ALU_VEC_021_SCL_122, llvm::R600InstrInfo::ALU_VEC_102_SCL_221, llvm::R600InstrInfo::ALU_VEC_120_SCL_212, and llvm_unreachable.

Referenced by isConstCompatible(), and llvm::R600InstrInfo::isLegalUpTo().

Definition at line 692 of file R600InstrInfo.cpp.

Referenced by llvm::R600InstrInfo::AnalyzeBranch(), and translateImmediate().

| static bool isConstCompatible | ( | R600InstrInfo::BankSwizzle | TransSwz, |

| const std::vector< std::pair< int, unsigned > > & | TransOps, | ||

| unsigned | ConstCount | ||

| ) | [static] |

Instructions in Trans slot can't read gpr at cycle 0 if they also read a const, and can't read a gpr at cycle 1 if they read 2 const.

Definition at line 532 of file R600InstrInfo.cpp.

References getTransSwizzle().

Referenced by llvm::R600InstrInfo::fitsReadPortLimitations().

Definition at line 688 of file R600InstrInfo.cpp.

Referenced by llvm::R600InstrInfo::AnalyzeBranch().

| static bool isPredicateSetter | ( | unsigned | Opcode | ) | [static] |

Definition at line 665 of file R600InstrInfo.cpp.

Referenced by llvm::R600InstrInfo::AnalyzeBranch(), llvm::R600InstrInfo::DefinesPredicate(), and findFirstPredicateSetterFrom().

| static bool NextPossibleSolution | ( | std::vector< R600InstrInfo::BankSwizzle > & | SwzCandidate, |

| unsigned | Idx | ||

| ) | [static] |

Given a swizzle sequence SwzCandidate and an index Idx, returns the next (in lexicographic term) swizzle sequence assuming that all swizzles after Idx can be skipped

Definition at line 496 of file R600InstrInfo.cpp.

References llvm::R600InstrInfo::ALU_VEC_012_SCL_210, and llvm::R600InstrInfo::ALU_VEC_210.

Referenced by llvm::R600InstrInfo::FindSwizzleForVectorSlot().

| static std::vector<std::pair<int, unsigned> > Swizzle | ( | std::vector< std::pair< int, unsigned > > | Src, |

| R600InstrInfo::BankSwizzle | Swz | ||

| ) | [static] |

Definition at line 390 of file R600InstrInfo.cpp.

References llvm::R600InstrInfo::ALU_VEC_012_SCL_210, llvm::R600InstrInfo::ALU_VEC_021_SCL_122, llvm::R600InstrInfo::ALU_VEC_102_SCL_221, llvm::R600InstrInfo::ALU_VEC_120_SCL_212, llvm::R600InstrInfo::ALU_VEC_201, llvm::R600InstrInfo::ALU_VEC_210, and std::swap().

Referenced by llvm::R600InstrInfo::isLegalUpTo().

1.7.6.1

1.7.6.1