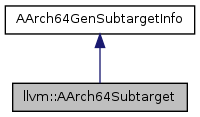

#include <AArch64Subtarget.h>

Detailed Description

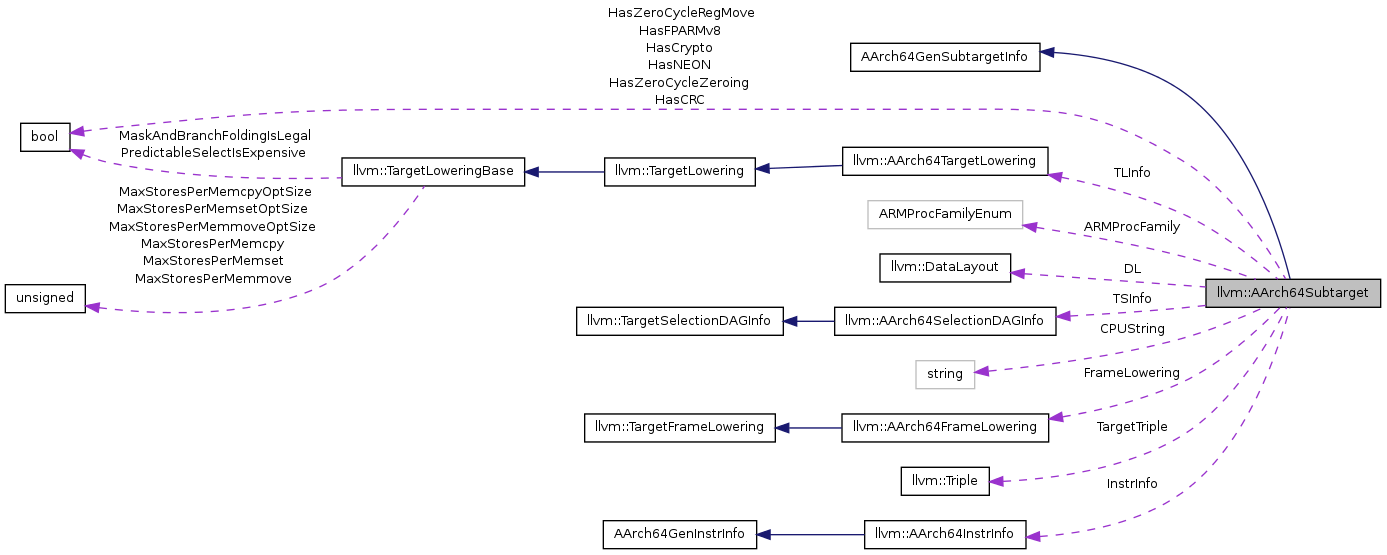

Definition at line 33 of file AArch64Subtarget.h.

Member Enumeration Documentation

enum llvm::AArch64Subtarget::ARMProcFamilyEnum [protected] |

Definition at line 35 of file AArch64Subtarget.h.

Constructor & Destructor Documentation

| AArch64Subtarget::AArch64Subtarget | ( | const std::string & | TT, |

| const std::string & | CPU, | ||

| const std::string & | FS, | ||

| TargetMachine & | TM, | ||

| bool | LittleEndian | ||

| ) |

This constructor initializes the data members to match that of the specified triple.

Definition at line 44 of file AArch64Subtarget.cpp.

Member Function Documentation

| unsigned char AArch64Subtarget::ClassifyGlobalReference | ( | const GlobalValue * | GV, |

| const TargetMachine & | TM | ||

| ) | const |

ClassifyGlobalReference - Find the target operand flags that describe how a global value should be referenced for the current subtarget.

Definition at line 65 of file AArch64Subtarget.cpp.

References llvm::TargetMachine::getCodeModel(), llvm::TargetMachine::getRelocationModel(), llvm::GlobalValue::hasAvailableExternallyLinkage(), llvm::GlobalValue::hasDefaultVisibility(), llvm::GlobalValue::hasLocalLinkage(), llvm::GlobalValue::isDeclaration(), llvm::GlobalValue::isMaterializable(), isTargetMachO(), llvm::GlobalValue::isWeakForLinker(), llvm::CodeModel::Large, llvm::AArch64II::MO_CONSTPOOL, llvm::AArch64II::MO_GOT, llvm::AArch64II::MO_NO_FLAG, llvm::CodeModel::Small, and llvm::Reloc::Static.

Referenced by llvm::AArch64InstrInfo::expandPostRAPseudo().

| bool AArch64Subtarget::enableEarlyIfConversion | ( | ) | const [override] |

Definition at line 133 of file AArch64Subtarget.cpp.

References EnableEarlyIfConvert.

| bool llvm::AArch64Subtarget::enableMachineScheduler | ( | ) | const [inline, override] |

Definition at line 88 of file AArch64Subtarget.h.

| bool llvm::AArch64Subtarget::enablePostMachineScheduler | ( | ) | const [inline, override] |

Definition at line 89 of file AArch64Subtarget.h.

References isCortexA53(), and isCortexA57().

| const char * AArch64Subtarget::getBZeroEntry | ( | ) | const |

This function returns the name of a function which has an interface like the non-standard bzero function, if such a function exists on the current subtarget and it is considered prefereable over memset with zero passed as the second argument. Otherwise it returns null.

Definition at line 116 of file AArch64Subtarget.cpp.

References isTargetDarwin().

| const DataLayout* llvm::AArch64Subtarget::getDataLayout | ( | ) | const [inline, override] |

Definition at line 84 of file AArch64Subtarget.h.

References DL.

| const AArch64FrameLowering* llvm::AArch64Subtarget::getFrameLowering | ( | ) | const [inline, override] |

Definition at line 77 of file AArch64Subtarget.h.

References FrameLowering.

| const AArch64InstrInfo* llvm::AArch64Subtarget::getInstrInfo | ( | ) | const [inline, override] |

Definition at line 83 of file AArch64Subtarget.h.

References InstrInfo.

Referenced by getRegisterInfo().

| unsigned llvm::AArch64Subtarget::getMaxInlineSizeThreshold | ( | ) | const [inline] |

getMaxInlineSizeThreshold - Returns the maximum memset / memcpy size that still makes it profitable to inline the call.

Definition at line 121 of file AArch64Subtarget.h.

| const AArch64RegisterInfo* llvm::AArch64Subtarget::getRegisterInfo | ( | ) | const [inline, override] |

Definition at line 85 of file AArch64Subtarget.h.

References getInstrInfo(), and llvm::AArch64InstrInfo::getRegisterInfo().

| const AArch64SelectionDAGInfo* llvm::AArch64Subtarget::getSelectionDAGInfo | ( | ) | const [inline, override] |

Definition at line 74 of file AArch64Subtarget.h.

References TSInfo.

| const AArch64TargetLowering* llvm::AArch64Subtarget::getTargetLowering | ( | ) | const [inline, override] |

Definition at line 80 of file AArch64Subtarget.h.

References TLInfo.

| bool llvm::AArch64Subtarget::hasCRC | ( | ) | const [inline] |

Definition at line 100 of file AArch64Subtarget.h.

References HasCRC.

| bool llvm::AArch64Subtarget::hasCrypto | ( | ) | const [inline] |

Definition at line 99 of file AArch64Subtarget.h.

References HasCrypto.

| bool llvm::AArch64Subtarget::hasFPARMv8 | ( | ) | const [inline] |

Definition at line 97 of file AArch64Subtarget.h.

References HasFPARMv8.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), and llvm::AArch64TargetLowering::getOptimalMemOpType().

| bool llvm::AArch64Subtarget::hasNEON | ( | ) | const [inline] |

Definition at line 98 of file AArch64Subtarget.h.

References HasNEON.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::AArch64InstrInfo::copyPhysReg(), llvm::AArch64InstrInfo::copyPhysRegTuple(), llvm::AArch64InstrInfo::loadRegFromStackSlot(), and llvm::AArch64InstrInfo::storeRegToStackSlot().

| bool llvm::AArch64Subtarget::hasZeroCycleRegMove | ( | ) | const [inline] |

Definition at line 93 of file AArch64Subtarget.h.

References HasZeroCycleRegMove.

Referenced by llvm::AArch64InstrInfo::copyPhysReg().

| bool llvm::AArch64Subtarget::hasZeroCycleZeroing | ( | ) | const [inline] |

Definition at line 95 of file AArch64Subtarget.h.

References HasZeroCycleZeroing.

Referenced by llvm::AArch64InstrInfo::copyPhysReg().

| bool llvm::AArch64Subtarget::isCortexA53 | ( | ) | const [inline] |

Definition at line 115 of file AArch64Subtarget.h.

References CPUString.

Referenced by enablePostMachineScheduler(), llvm::AArch64InstrInfo::isAsCheapAsAMove(), and useAA().

| bool llvm::AArch64Subtarget::isCortexA57 | ( | ) | const [inline] |

Definition at line 114 of file AArch64Subtarget.h.

References CPUString.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), llvm::AArch64TargetMachine::AArch64TargetMachine(), enablePostMachineScheduler(), llvm::AArch64InstrInfo::isAsCheapAsAMove(), and useAA().

| bool llvm::AArch64Subtarget::isCyclone | ( | ) | const [inline] |

Definition at line 113 of file AArch64Subtarget.h.

References CPUString.

Referenced by performSTORECombine().

| bool llvm::AArch64Subtarget::isLittleEndian | ( | ) | const [inline] |

Definition at line 102 of file AArch64Subtarget.h.

References DL, and llvm::DataLayout::isLittleEndian().

| bool llvm::AArch64Subtarget::isTargetCOFF | ( | ) | const [inline] |

Definition at line 109 of file AArch64Subtarget.h.

References llvm::Triple::isOSBinFormatCOFF(), and TargetTriple.

| bool llvm::AArch64Subtarget::isTargetDarwin | ( | ) | const [inline] |

Definition at line 104 of file AArch64Subtarget.h.

References llvm::Triple::isOSDarwin(), and TargetTriple.

Referenced by llvm::AArch64TargetLowering::CCAssignFnForCall(), getBZeroEntry(), llvm::AArch64RegisterInfo::getReservedRegs(), llvm::AArch64RegisterInfo::getTLSCallPreservedMask(), and llvm::AArch64RegisterInfo::isReservedReg().

| bool llvm::AArch64Subtarget::isTargetELF | ( | ) | const [inline] |

Definition at line 110 of file AArch64Subtarget.h.

References llvm::Triple::isOSBinFormatELF(), and TargetTriple.

Referenced by llvm::AArch64RegisterInfo::getTLSCallPreservedMask().

| bool llvm::AArch64Subtarget::isTargetIOS | ( | ) | const [inline] |

Definition at line 105 of file AArch64Subtarget.h.

References llvm::Triple::isiOS(), and TargetTriple.

| bool llvm::AArch64Subtarget::isTargetLinux | ( | ) | const [inline] |

Definition at line 106 of file AArch64Subtarget.h.

References llvm::Triple::isOSLinux(), and TargetTriple.

| bool llvm::AArch64Subtarget::isTargetMachO | ( | ) | const [inline] |

Definition at line 111 of file AArch64Subtarget.h.

References llvm::Triple::isOSBinFormatMachO(), and TargetTriple.

Referenced by llvm::AArch64TargetLowering::AArch64TargetLowering(), and ClassifyGlobalReference().

| bool llvm::AArch64Subtarget::isTargetWindows | ( | ) | const [inline] |

Definition at line 107 of file AArch64Subtarget.h.

References llvm::Triple::isOSWindows(), and TargetTriple.

| void AArch64Subtarget::overrideSchedPolicy | ( | MachineSchedPolicy & | Policy, |

| MachineInstr * | begin, | ||

| MachineInstr * | end, | ||

| unsigned | NumRegionInstrs | ||

| ) | const [override] |

Definition at line 124 of file AArch64Subtarget.cpp.

References llvm::MachineSchedPolicy::OnlyBottomUp, and llvm::MachineSchedPolicy::OnlyTopDown.

| void llvm::AArch64Subtarget::ParseSubtargetFeatures | ( | StringRef | CPU, |

| StringRef | FS | ||

| ) |

ParseSubtargetFeatures - Parses features string setting specified subtarget options. Definition of function is auto generated by tblgen.

| bool llvm::AArch64Subtarget::useAA | ( | ) | const [inline, override] |

Definition at line 117 of file AArch64Subtarget.h.

References isCortexA53(), and isCortexA57().

Member Data Documentation

ARMProcFamily - ARM processor family: Cortex-A53, Cortex-A57, and others.

Definition at line 38 of file AArch64Subtarget.h.

std::string llvm::AArch64Subtarget::CPUString [protected] |

CPUString - String name of used CPU.

Definition at line 52 of file AArch64Subtarget.h.

Referenced by isCortexA53(), isCortexA57(), and isCyclone().

const DataLayout llvm::AArch64Subtarget::DL [protected] |

Definition at line 57 of file AArch64Subtarget.h.

Referenced by getDataLayout(), and isLittleEndian().

Definition at line 58 of file AArch64Subtarget.h.

Referenced by getFrameLowering().

bool llvm::AArch64Subtarget::HasCRC [protected] |

Definition at line 43 of file AArch64Subtarget.h.

Referenced by hasCRC().

bool llvm::AArch64Subtarget::HasCrypto [protected] |

Definition at line 42 of file AArch64Subtarget.h.

Referenced by hasCrypto().

bool llvm::AArch64Subtarget::HasFPARMv8 [protected] |

Definition at line 40 of file AArch64Subtarget.h.

Referenced by hasFPARMv8().

bool llvm::AArch64Subtarget::HasNEON [protected] |

Definition at line 41 of file AArch64Subtarget.h.

Referenced by hasNEON().

bool llvm::AArch64Subtarget::HasZeroCycleRegMove [protected] |

Definition at line 46 of file AArch64Subtarget.h.

Referenced by hasZeroCycleRegMove().

bool llvm::AArch64Subtarget::HasZeroCycleZeroing [protected] |

Definition at line 49 of file AArch64Subtarget.h.

Referenced by hasZeroCycleZeroing().

AArch64InstrInfo llvm::AArch64Subtarget::InstrInfo [protected] |

Definition at line 59 of file AArch64Subtarget.h.

Referenced by getInstrInfo().

Triple llvm::AArch64Subtarget::TargetTriple [protected] |

TargetTriple - What processor and OS we're targeting.

Definition at line 55 of file AArch64Subtarget.h.

Referenced by isTargetCOFF(), isTargetDarwin(), isTargetELF(), isTargetIOS(), isTargetLinux(), isTargetMachO(), and isTargetWindows().

AArch64TargetLowering llvm::AArch64Subtarget::TLInfo [protected] |

Definition at line 61 of file AArch64Subtarget.h.

Referenced by getTargetLowering().

Definition at line 60 of file AArch64Subtarget.h.

Referenced by getSelectionDAGInfo().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1