#include <AArch64ISelLowering.h>

Public Member Functions | |

| AArch64TargetLowering (TargetMachine &TM) | |

| CCAssignFn * | CCAssignFnForCall (CallingConv::ID CC, bool IsVarArg) const |

| Selects the correct CCAssignFn for a given CallingConvention value. | |

| void | computeKnownBitsForTargetNode (const SDValue Op, APInt &KnownZero, APInt &KnownOne, const SelectionDAG &DAG, unsigned Depth=0) const override |

| MVT | getScalarShiftAmountTy (EVT LHSTy) const override |

| bool | allowsMisalignedMemoryAccesses (EVT VT, unsigned AddrSpace=0, unsigned Align=1, bool *Fast=nullptr) const override |

| SDValue | LowerOperation (SDValue Op, SelectionDAG &DAG) const override |

| LowerOperation - Provide custom lowering hooks for some operations. | |

| const char * | getTargetNodeName (unsigned Opcode) const override |

| This method returns the name of a target specific DAG node. | |

| SDValue | PerformDAGCombine (SDNode *N, DAGCombinerInfo &DCI) const override |

| unsigned | getFunctionAlignment (const Function *F) const |

| getFunctionAlignment - Return the Log2 alignment of this function. | |

| unsigned | getMaximalGlobalOffset () const override |

| bool | isNoopAddrSpaceCast (unsigned SrcAS, unsigned DestAS) const override |

| Returns true if a cast between SrcAS and DestAS is a noop. | |

| FastISel * | createFastISel (FunctionLoweringInfo &funcInfo, const TargetLibraryInfo *libInfo) const override |

| bool | isOffsetFoldingLegal (const GlobalAddressSDNode *GA) const override |

| bool | isFPImmLegal (const APFloat &Imm, EVT VT) const override |

| bool | isShuffleMaskLegal (const SmallVectorImpl< int > &M, EVT VT) const override |

| EVT | getSetCCResultType (LLVMContext &Context, EVT VT) const override |

| getSetCCResultType - Return the ISD::SETCC ValueType | |

| SDValue | ReconstructShuffle (SDValue Op, SelectionDAG &DAG) const |

| MachineBasicBlock * | EmitF128CSEL (MachineInstr *MI, MachineBasicBlock *BB) const |

| MachineBasicBlock * | EmitInstrWithCustomInserter (MachineInstr *MI, MachineBasicBlock *MBB) const override |

| bool | getTgtMemIntrinsic (IntrinsicInfo &Info, const CallInst &I, unsigned Intrinsic) const override |

| bool | isTruncateFree (Type *Ty1, Type *Ty2) const override |

| bool | isTruncateFree (EVT VT1, EVT VT2) const override |

| bool | isZExtFree (Type *Ty1, Type *Ty2) const override |

| bool | isZExtFree (EVT VT1, EVT VT2) const override |

| bool | isZExtFree (SDValue Val, EVT VT2) const override |

| bool | hasPairedLoad (Type *LoadedType, unsigned &RequiredAligment) const override |

| bool | hasPairedLoad (EVT LoadedType, unsigned &RequiredAligment) const override |

| bool | isLegalAddImmediate (int64_t) const override |

| bool | isLegalICmpImmediate (int64_t) const override |

| EVT | getOptimalMemOpType (uint64_t Size, unsigned DstAlign, unsigned SrcAlign, bool IsMemset, bool ZeroMemset, bool MemcpyStrSrc, MachineFunction &MF) const override |

| bool | isLegalAddressingMode (const AddrMode &AM, Type *Ty) const override |

| int | getScalingFactorCost (const AddrMode &AM, Type *Ty) const override |

| Return the cost of the scaling factor used in the addressing mode represented by AM for this target, for a load/store of the specified type. If the AM is supported, the return value must be >= 0. If the AM is not supported, it returns a negative value. | |

| bool | isFMAFasterThanFMulAndFAdd (EVT VT) const override |

| const MCPhysReg * | getScratchRegisters (CallingConv::ID CC) const override |

| bool | isDesirableToCommuteWithShift (const SDNode *N) const override |

| Returns false if N is a bit extraction pattern of (X >> C) & Mask. | |

| bool | shouldConvertConstantLoadToIntImm (const APInt &Imm, Type *Ty) const override |

| Returns true if it is beneficial to convert a load of a constant to just the constant itself. | |

| bool | hasLoadLinkedStoreConditional () const override |

| Value * | emitLoadLinked (IRBuilder<> &Builder, Value *Addr, AtomicOrdering Ord) const override |

| Value * | emitStoreConditional (IRBuilder<> &Builder, Value *Val, Value *Addr, AtomicOrdering Ord) const override |

| bool | shouldExpandAtomicLoadInIR (LoadInst *LI) const override |

| bool | shouldExpandAtomicStoreInIR (StoreInst *SI) const override |

| bool | shouldExpandAtomicRMWInIR (AtomicRMWInst *AI) const override |

| bool | useLoadStackGuardNode () const override |

| TargetLoweringBase::LegalizeTypeAction | getPreferredVectorAction (EVT VT) const override |

| Return the preferred vector type legalization action. | |

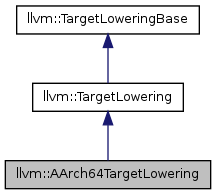

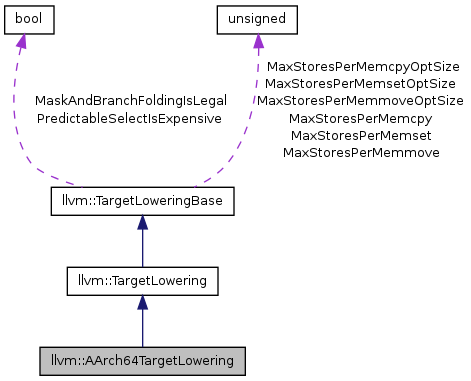

Detailed Description

Definition at line 203 of file AArch64ISelLowering.h.

Constructor & Destructor Documentation

| AArch64TargetLowering::AArch64TargetLowering | ( | TargetMachine & | TM | ) | [explicit] |

Definition at line 79 of file AArch64ISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::TargetLoweringBase::AddPromotedToType(), llvm::TargetLoweringBase::addRegisterClass(), Align(), llvm::ISD::ANY_EXTEND, llvm::array_lengthof(), llvm::ISD::BITCAST, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BRCOND, llvm::ISD::BSWAP, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::ISD::CONCAT_VECTORS, llvm::ISD::ConstantPool, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::TargetLoweringBase::Custom, llvm::ISD::DYNAMIC_STACKALLOC, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::MVT::f128, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::MVT::f80, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FCEIL, llvm::ISD::FCOPYSIGN, llvm::ISD::FCOS, llvm::ISD::FDIV, llvm::ISD::FEXP, llvm::ISD::FEXP2, llvm::ISD::FFLOOR, llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::ISD::FLOG, llvm::ISD::FLOG10, llvm::ISD::FLOG2, llvm::ISD::FMA, llvm::ISD::FMUL, llvm::ISD::FNEARBYINT, llvm::ISD::FNEG, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FPOW, llvm::ISD::FPOWI, llvm::ISD::FREM, llvm::ISD::FRINT, llvm::ISD::FROUND, llvm::ISD::FSIN, llvm::ISD::FSINCOS, llvm::ISD::FSQRT, llvm::ISD::FSUB, llvm::ISD::FTRUNC, llvm::TargetMachine::getSubtarget(), llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::AArch64Subtarget::hasFPARMv8(), llvm::AArch64Subtarget::hasNEON(), llvm::Sched::Hybrid, I, llvm::MVT::i1, llvm::MVT::i128, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::AArch64Subtarget::isCortexA57(), llvm::AArch64Subtarget::isTargetMachO(), llvm::ISD::JumpTable, llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::TargetLoweringBase::Legal, llvm::TargetLoweringBase::MaskAndBranchFoldingIsLegal, llvm::TargetLoweringBase::MaxStoresPerMemcpy, llvm::TargetLoweringBase::MaxStoresPerMemcpyOptSize, llvm::TargetLoweringBase::MaxStoresPerMemmove, llvm::TargetLoweringBase::MaxStoresPerMemmoveOptSize, llvm::TargetLoweringBase::MaxStoresPerMemset, llvm::TargetLoweringBase::MaxStoresPerMemsetOptSize, llvm::ISD::MUL, llvm::ISD::MULHS, llvm::ISD::MULHU, llvm::ISD::OR, llvm::MVT::Other, llvm::ISD::PRE_INC, llvm::TargetLoweringBase::PredictableSelectIsExpensive, llvm::ISD::PREFETCH, llvm::TargetLoweringBase::Promote, llvm::ISD::ROTL, llvm::ISD::SADDO, llvm::ISD::SDIVREM, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::TargetLoweringBase::setBooleanContents(), llvm::TargetLoweringBase::setBooleanVectorContents(), llvm::ISD::SETCC, llvm::TargetLoweringBase::setExceptionPointerRegister(), llvm::TargetLoweringBase::setExceptionSelectorRegister(), llvm::TargetLoweringBase::setHasExtractBitsInsn(), llvm::TargetLoweringBase::setIndexedLoadAction(), llvm::TargetLoweringBase::setIndexedStoreAction(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setMinFunctionAlignment(), llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setSchedulingPreference(), llvm::TargetLoweringBase::setStackPointerRegisterToSaveRestore(), llvm::TargetLoweringBase::setTargetDAGCombine(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SEXTLOAD, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SINT_TO_FP, llvm::ISD::SMUL_LOHI, llvm::ISD::SMULO, llvm::ISD::SRA_PARTS, llvm::ISD::SREM, llvm::ISD::SRL_PARTS, llvm::ISD::SSUBO, llvm::ISD::STACKRESTORE, llvm::ISD::STACKSAVE, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ISD::SUBC, llvm::ISD::SUBE, llvm::ISD::TRAP, llvm::ISD::UADDO, llvm::ISD::UDIVREM, llvm::ISD::UINT_TO_FP, llvm::ISD::UMUL_LOHI, llvm::ISD::UMULO, llvm::ISD::UREM, llvm::ISD::USUBO, llvm::MVT::v16i8, llvm::MVT::v1f64, llvm::MVT::v1i64, llvm::MVT::v2f32, llvm::MVT::v2f64, llvm::MVT::v2i16, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v4f16, llvm::MVT::v4f32, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v4i8, llvm::MVT::v8f16, llvm::MVT::v8i16, llvm::MVT::v8i8, llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VAEND, llvm::ISD::VASTART, llvm::ISD::VSELECT, llvm::ISD::XOR, llvm::ISD::ZERO_EXTEND, llvm::TargetLoweringBase::ZeroOrNegativeOneBooleanContent, llvm::TargetLoweringBase::ZeroOrOneBooleanContent, and llvm::ISD::ZEXTLOAD.

Member Function Documentation

| bool llvm::AArch64TargetLowering::allowsMisalignedMemoryAccesses | ( | EVT | VT, |

| unsigned | AddrSpace = 0, |

||

| unsigned | Align = 1, |

||

| bool * | Fast = nullptr |

||

| ) | const [inline, override, virtual] |

allowsMisalignedMemoryAccesses - Returns true if the target allows unaligned memory accesses. of the specified type.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 223 of file AArch64ISelLowering.h.

References llvm::CallingConv::Fast.

Referenced by getOptimalMemOpType().

| CCAssignFn * AArch64TargetLowering::CCAssignFnForCall | ( | CallingConv::ID | CC, |

| bool | IsVarArg | ||

| ) | const |

Selects the correct CCAssignFn for a given CallingConvention value.

Definition at line 1785 of file AArch64ISelLowering.cpp.

References llvm::CallingConv::C, llvm::CallingConv::Fast, llvm::AArch64Subtarget::isTargetDarwin(), llvm_unreachable, and llvm::CallingConv::WebKit_JS.

| void AArch64TargetLowering::computeKnownBitsForTargetNode | ( | const SDValue | Op, |

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [override, virtual] |

computeKnownBitsForTargetNode - Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

Reimplemented from llvm::TargetLowering.

Definition at line 665 of file AArch64ISelLowering.cpp.

References llvm::SelectionDAG::computeKnownBits(), llvm::AArch64ISD::CSEL, llvm::APInt::getBitWidth(), llvm::APInt::getHighBitsSet(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::EVT::getScalarType(), llvm::EVT::getSimpleVT(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::ConstantSDNode::getZExtValue(), llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::MVT::v16i8, llvm::MVT::v4i16, llvm::MVT::v8i16, and llvm::MVT::v8i8.

| FastISel * AArch64TargetLowering::createFastISel | ( | FunctionLoweringInfo & | funcInfo, |

| const TargetLibraryInfo * | libInfo | ||

| ) | const [override, virtual] |

createFastISel - This method returns a target specific FastISel object, or null if the target does not support "fast" ISel.

Reimplemented from llvm::TargetLowering.

Definition at line 737 of file AArch64ISelLowering.cpp.

| MachineBasicBlock * AArch64TargetLowering::EmitF128CSEL | ( | MachineInstr * | MI, |

| MachineBasicBlock * | BB | ||

| ) | const |

Definition at line 859 of file AArch64ISelLowering.cpp.

References llvm::MachineBasicBlock::addLiveIn(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getImm(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::MachineFunction::insert(), llvm::MachineOperand::isKill(), llvm::AArch64SysReg::NZCV, llvm::TargetOpcode::PHI, llvm::MachineBasicBlock::splice(), TII, and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

Referenced by EmitInstrWithCustomInserter().

| MachineBasicBlock * AArch64TargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::TargetLowering.

Definition at line 921 of file AArch64ISelLowering.cpp.

References llvm::MachineInstr::dump(), EmitF128CSEL(), llvm::TargetLoweringBase::emitPatchPoint(), llvm::MachineInstr::getOpcode(), llvm_unreachable, llvm::TargetOpcode::PATCHPOINT, and llvm::TargetOpcode::STACKMAP.

| Value * AArch64TargetLowering::emitLoadLinked | ( | IRBuilder<> & | Builder, |

| Value * | Addr, | ||

| AtomicOrdering | Ord | ||

| ) | const [override, virtual] |

Perform a load-linked operation on Addr, returning a "Value *" with the corresponding pointee type. This may entail some non-trivial operations to truncate or reconstruct types that will be illegal in the backend. See ARMISelLowering for an example implementation.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 8578 of file AArch64ISelLowering.cpp.

References llvm::IRBuilder< preserveNames, T, Inserter >::CreateBitCast(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateCall(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateExtractValue(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateOr(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateShl(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateTruncOrBitCast(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateZExt(), llvm::ConstantInt::get(), llvm::Module::getContext(), llvm::Intrinsic::getDeclaration(), llvm::IRBuilderBase::GetInsertBlock(), llvm::Type::getInt8PtrTy(), llvm::BasicBlock::getParent(), llvm::GlobalValue::getParent(), llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), llvm::tgtok::Int, and llvm::isAtLeastAcquire().

| Value * AArch64TargetLowering::emitStoreConditional | ( | IRBuilder<> & | Builder, |

| Value * | Val, | ||

| Value * | Addr, | ||

| AtomicOrdering | Ord | ||

| ) | const [override, virtual] |

Perform a store-conditional operation to Addr. Return the status of the store. This should be 0 if the store succeeded, non-zero otherwise.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 8613 of file AArch64ISelLowering.cpp.

References llvm::IRBuilder< preserveNames, T, Inserter >::CreateBitCast(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateCall2(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateCall3(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateLShr(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateTrunc(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateZExtOrBitCast(), llvm::Module::getContext(), llvm::Intrinsic::getDeclaration(), llvm::Function::getFunctionType(), llvm::IRBuilderBase::GetInsertBlock(), llvm::Type::getInt64Ty(), llvm::Type::getInt8PtrTy(), llvm::FunctionType::getParamType(), llvm::BasicBlock::getParent(), llvm::GlobalValue::getParent(), llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), llvm::tgtok::Int, and llvm::isAtLeastRelease().

| unsigned AArch64TargetLowering::getFunctionAlignment | ( | const Function * | F | ) | const |

getFunctionAlignment - Return the Log2 alignment of this function.

Definition at line 1774 of file AArch64ISelLowering.cpp.

| unsigned AArch64TargetLowering::getMaximalGlobalOffset | ( | ) | const [override, virtual] |

getMaximalGlobalOffset - Returns the maximal possible offset which can be used for loads / stores from the global.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 729 of file AArch64ISelLowering.cpp.

| EVT AArch64TargetLowering::getOptimalMemOpType | ( | uint64_t | , |

| unsigned | , | ||

| unsigned | , | ||

| bool | , | ||

| bool | , | ||

| bool | , | ||

| MachineFunction & | |||

| ) | const [override, virtual] |

Returns the target specific optimal type for load and store operations as a result of memset, memcpy, and memmove lowering.

If DstAlign is zero that means it's safe to destination alignment can satisfy any constraint. Similarly if SrcAlign is zero it means there isn't a need to check it against alignment requirement, probably because the source does not need to be loaded. If 'IsMemset' is true, that means it's expanding a memset. If 'ZeroMemset' is true, that means it's a memset of zero. 'MemcpyStrSrc' indicates whether the memcpy source is constant so it does not need to be loaded. It returns EVT::Other if the type should be determined using generic target-independent logic.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6401 of file AArch64ISelLowering.cpp.

References allowsMisalignedMemoryAccesses(), F(), llvm::MVT::f128, llvm::CallingConv::Fast, llvm::AttributeSet::FunctionIndex, llvm::Function::getAttributes(), llvm::MachineFunction::getFunction(), llvm::AttributeSet::hasAttribute(), llvm::AArch64Subtarget::hasFPARMv8(), llvm::MVT::i32, llvm::MVT::i64, memOpAlign(), and llvm::Attribute::NoImplicitFloat.

| TargetLoweringBase::LegalizeTypeAction AArch64TargetLowering::getPreferredVectorAction | ( | EVT | VT | ) | const [override, virtual] |

Return the preferred vector type legalization action.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 8541 of file AArch64ISelLowering.cpp.

References llvm::EVT::getSimpleVT(), llvm::TargetLoweringBase::TypeWidenVector, llvm::MVT::v1f32, llvm::MVT::v1i16, llvm::MVT::v1i32, and llvm::MVT::v1i8.

| MVT AArch64TargetLowering::getScalarShiftAmountTy | ( | EVT | LHSTy | ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 725 of file AArch64ISelLowering.cpp.

References llvm::MVT::i64.

| int AArch64TargetLowering::getScalingFactorCost | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

Return the cost of the scaling factor used in the addressing mode represented by AM for this target, for a load/store of the specified type. If the AM is supported, the return value must be >= 0. If the AM is not supported, it returns a negative value.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6489 of file AArch64ISelLowering.cpp.

References isLegalAddressingMode(), and llvm::TargetLoweringBase::AddrMode::Scale.

| const MCPhysReg * AArch64TargetLowering::getScratchRegisters | ( | CallingConv::ID | CC | ) | const [override, virtual] |

Returns a 0 terminated array of registers that can be safely used as scratch registers.

Reimplemented from llvm::TargetLowering.

Definition at line 6523 of file AArch64ISelLowering.cpp.

| EVT AArch64TargetLowering::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [override, virtual] |

getSetCCResultType - Return the ISD::SETCC ValueType

Reimplemented from llvm::TargetLoweringBase.

Definition at line 656 of file AArch64ISelLowering.cpp.

References llvm::EVT::changeVectorElementTypeToInteger(), llvm::MVT::i32, and llvm::EVT::isVector().

| const char * AArch64TargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

Definition at line 742 of file AArch64ISelLowering.cpp.

References llvm::AArch64ISD::ADC, llvm::AArch64ISD::ADCS, llvm::AArch64ISD::ADDlow, llvm::AArch64ISD::ADDS, llvm::AArch64ISD::ADRP, llvm::AArch64ISD::ANDS, llvm::AArch64ISD::BICi, llvm::AArch64ISD::BIT, llvm::AArch64ISD::BRCOND, llvm::AArch64ISD::BSL, llvm::AArch64ISD::CALL, llvm::AArch64ISD::CBNZ, llvm::AArch64ISD::CBZ, llvm::AArch64ISD::CMEQ, llvm::AArch64ISD::CMEQz, llvm::AArch64ISD::CMGE, llvm::AArch64ISD::CMGEz, llvm::AArch64ISD::CMGT, llvm::AArch64ISD::CMGTz, llvm::AArch64ISD::CMHI, llvm::AArch64ISD::CMHS, llvm::AArch64ISD::CMLEz, llvm::AArch64ISD::CMLTz, llvm::AArch64ISD::CSEL, llvm::AArch64ISD::CSINC, llvm::AArch64ISD::CSINV, llvm::AArch64ISD::CSNEG, llvm::AArch64ISD::DUP, llvm::AArch64ISD::DUPLANE16, llvm::AArch64ISD::DUPLANE32, llvm::AArch64ISD::DUPLANE64, llvm::AArch64ISD::DUPLANE8, llvm::AArch64ISD::EXT, llvm::AArch64ISD::EXTR, llvm::AArch64ISD::FCMEQ, llvm::AArch64ISD::FCMEQz, llvm::AArch64ISD::FCMGE, llvm::AArch64ISD::FCMGEz, llvm::AArch64ISD::FCMGT, llvm::AArch64ISD::FCMGTz, llvm::AArch64ISD::FCMLEz, llvm::AArch64ISD::FCMLTz, llvm::AArch64ISD::FCMP, llvm::AArch64ISD::FCSEL, llvm::AArch64ISD::FMAX, llvm::AArch64ISD::FMIN, llvm::AArch64ISD::FMOV, llvm::AArch64ISD::LD1DUPpost, llvm::AArch64ISD::LD1LANEpost, llvm::AArch64ISD::LD1x2post, llvm::AArch64ISD::LD1x3post, llvm::AArch64ISD::LD1x4post, llvm::AArch64ISD::LD2DUPpost, llvm::AArch64ISD::LD2LANEpost, llvm::AArch64ISD::LD2post, llvm::AArch64ISD::LD3DUPpost, llvm::AArch64ISD::LD3LANEpost, llvm::AArch64ISD::LD3post, llvm::AArch64ISD::LD4DUPpost, llvm::AArch64ISD::LD4LANEpost, llvm::AArch64ISD::LD4post, llvm::AArch64ISD::LOADgot, llvm::AArch64ISD::MOVI, llvm::AArch64ISD::MOVIedit, llvm::AArch64ISD::MOVImsl, llvm::AArch64ISD::MOVIshift, llvm::AArch64ISD::MVNImsl, llvm::AArch64ISD::MVNIshift, llvm::AArch64ISD::NEG, llvm::AArch64ISD::NOT, llvm::AArch64ISD::ORRi, llvm::AArch64ISD::RET_FLAG, llvm::AArch64ISD::REV16, llvm::AArch64ISD::REV32, llvm::AArch64ISD::REV64, llvm::AArch64ISD::SBC, llvm::AArch64ISD::SBCS, llvm::AArch64ISD::SITOF, llvm::AArch64ISD::SQSHL_I, llvm::AArch64ISD::SQSHLU_I, llvm::AArch64ISD::SRSHR_I, llvm::AArch64ISD::ST1x2post, llvm::AArch64ISD::ST1x3post, llvm::AArch64ISD::ST1x4post, llvm::AArch64ISD::ST2LANEpost, llvm::AArch64ISD::ST2post, llvm::AArch64ISD::ST3LANEpost, llvm::AArch64ISD::ST3post, llvm::AArch64ISD::ST4LANEpost, llvm::AArch64ISD::ST4post, llvm::AArch64ISD::SUBS, llvm::AArch64ISD::TBNZ, llvm::AArch64ISD::TBZ, llvm::AArch64ISD::TC_RETURN, llvm::AArch64ISD::THREAD_POINTER, llvm::AArch64ISD::TLSDESC_CALL, llvm::AArch64ISD::TRN1, llvm::AArch64ISD::TRN2, llvm::AArch64ISD::UITOF, llvm::AArch64ISD::UQSHL_I, llvm::AArch64ISD::URSHR_I, llvm::AArch64ISD::UZP1, llvm::AArch64ISD::UZP2, llvm::AArch64ISD::VASHR, llvm::AArch64ISD::VLSHR, llvm::AArch64ISD::VSHL, llvm::AArch64ISD::WrapperLarge, llvm::AArch64ISD::ZIP1, and llvm::AArch64ISD::ZIP2.

| bool AArch64TargetLowering::getTgtMemIntrinsic | ( | IntrinsicInfo & | Info, |

| const CallInst & | I, | ||

| unsigned | Intrinsic | ||

| ) | const [override, virtual] |

getTgtMemIntrinsic - Represent NEON load and store intrinsics as MemIntrinsicNodes. The associated MachineMemOperands record the alignment specified in the intrinsic calls.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6214 of file AArch64ISelLowering.cpp.

References llvm::TargetLoweringBase::IntrinsicInfo::align, llvm::DataLayout::getABITypeAlignment(), llvm::CallInst::getArgOperand(), llvm::Type::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::SequentialType::getElementType(), llvm::CallInst::getNumArgOperands(), llvm::Value::getType(), llvm::DataLayout::getTypeAllocSize(), llvm::EVT::getVectorVT(), llvm::MVT::getVT(), llvm::MVT::i128, llvm::MVT::i64, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::Type::isVectorTy(), llvm::TargetLoweringBase::IntrinsicInfo::memVT, llvm::TargetLoweringBase::IntrinsicInfo::offset, llvm::TargetLoweringBase::IntrinsicInfo::opc, llvm::TargetLoweringBase::IntrinsicInfo::ptrVal, llvm::TargetLoweringBase::IntrinsicInfo::readMem, llvm::TargetLoweringBase::IntrinsicInfo::vol, and llvm::TargetLoweringBase::IntrinsicInfo::writeMem.

| bool AArch64TargetLowering::hasLoadLinkedStoreConditional | ( | ) | const [override, virtual] |

True if AtomicExpandPass should use emitLoadLinked/emitStoreConditional and expand AtomicCmpXchgInst.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 8574 of file AArch64ISelLowering.cpp.

| bool AArch64TargetLowering::hasPairedLoad | ( | Type * | , |

| unsigned & | |||

| ) | const [override, virtual] |

Return true if the target supplies and combines to a paired load two loaded values of type LoadedType next to each other in memory. RequiredAlignment gives the minimal alignment constraints that must be met to be able to select this paired load.

This information is *not* used to generate actual paired loads, but it is used to generate a sequence of loads that is easier to combine into a paired load. For instance, something like this: a = load i64* addr b = trunc i64 a to i32 c = lshr i64 a, 32 d = trunc i64 c to i32 will be optimized into: b = load i32* addr1 d = load i32* addr2 Where addr1 = addr2 +/- sizeof(i32).

In other words, unless the target performs a post-isel load combining, this information should not be provided because it will generate more loads.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6374 of file AArch64ISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), llvm::Type::isFloatTy(), and llvm::Type::isIntegerTy().

| bool AArch64TargetLowering::hasPairedLoad | ( | EVT | LoadedType, |

| unsigned & | RequiredAligment | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6384 of file AArch64ISelLowering.cpp.

References llvm::EVT::getSizeInBits(), llvm::EVT::isFloatingPoint(), llvm::EVT::isInteger(), and llvm::EVT::isSimple().

| bool AArch64TargetLowering::isDesirableToCommuteWithShift | ( | const SDNode * | N | ) | const [override, virtual] |

Returns false if N is a bit extraction pattern of (X >> C) & Mask.

Reimplemented from llvm::TargetLowering.

Definition at line 6534 of file AArch64ISelLowering.cpp.

References llvm::ISD::AND, llvm::SDNode::getConstantOperandVal(), llvm::SDValue::getOpcode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::SDNode::getValueType(), llvm::MVT::i32, llvm::MVT::i64, llvm::isMask_64(), and llvm::ISD::SRL.

| bool AArch64TargetLowering::isFMAFasterThanFMulAndFAdd | ( | EVT | VT | ) | const [override, virtual] |

isFMAFasterThanFMulAndFAdd - Return true if an FMA operation is faster than a pair of fmul and fadd instructions. fmuladd intrinsics will be expanded to FMAs when this method returns true, otherwise fmuladd is expanded to fmul + fadd.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6505 of file AArch64ISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, llvm::EVT::getScalarType(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and llvm::MVT::SimpleTy.

| bool AArch64TargetLowering::isFPImmLegal | ( | const APFloat & | , |

| EVT | |||

| ) | const [override, virtual] |

Returns true if the target can instruction select the specified FP immediate natively. If false, the legalizer will materialize the FP immediate as a load from a constant pool.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 3988 of file AArch64ISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, llvm::AArch64_AM::getFP32Imm(), llvm::AArch64_AM::getFP64Imm(), and llvm::APFloat::isPosZero().

| bool AArch64TargetLowering::isLegalAddImmediate | ( | int64_t | ) | const [override, virtual] |

Return true if the specified immediate is legal add immediate, that is the target has add instructions which can add a register with the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6422 of file AArch64ISelLowering.cpp.

Referenced by isLegalICmpImmediate().

| bool AArch64TargetLowering::isLegalAddressingMode | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6438 of file AArch64ISelLowering.cpp.

References llvm::TargetLoweringBase::AddrMode::BaseGV, llvm::TargetLoweringBase::AddrMode::BaseOffs, llvm::TargetLoweringBase::getDataLayout(), llvm::DataLayout::getTypeSizeInBits(), llvm::TargetLoweringBase::AddrMode::HasBaseReg, llvm::isPowerOf2_64(), llvm::Type::isSized(), llvm::Log2_64(), and llvm::TargetLoweringBase::AddrMode::Scale.

Referenced by getScalingFactorCost().

| bool AArch64TargetLowering::isLegalICmpImmediate | ( | int64_t | ) | const [override, virtual] |

Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6430 of file AArch64ISelLowering.cpp.

References isLegalAddImmediate().

| bool llvm::AArch64TargetLowering::isNoopAddrSpaceCast | ( | unsigned | SrcAS, |

| unsigned | DestAS | ||

| ) | const [inline, override, virtual] |

Returns true if a cast between SrcAS and DestAS is a noop.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 249 of file AArch64ISelLowering.h.

| bool AArch64TargetLowering::isOffsetFoldingLegal | ( | const GlobalAddressSDNode * | GA | ) | const [override, virtual] |

Return true if folding a constant offset with the given GlobalAddress is legal. It is frequently not legal in PIC relocation models.

Reimplemented from llvm::TargetLowering.

Definition at line 3982 of file AArch64ISelLowering.cpp.

| bool AArch64TargetLowering::isShuffleMaskLegal | ( | const SmallVectorImpl< int > & | M, |

| EVT | VT | ||

| ) | const [override, virtual] |

isShuffleMaskLegal - Return true if the given shuffle mask can be codegen'd directly, or if it should be stack expanded.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 5939 of file AArch64ISelLowering.cpp.

References llvm::EVT::getSizeInBits(), llvm::EVT::getVectorNumElements(), llvm::EVT::is128BitVector(), llvm::EVT::is64BitVector(), isConcatMask(), isEXTMask(), isINSMask(), isREVMask(), llvm::ShuffleVectorSDNode::isSplatMask(), isTRN_v_undef_Mask(), isTRNMask(), isUZP_v_undef_Mask(), isUZPMask(), isZIP_v_undef_Mask(), isZIPMask(), and PerfectShuffleTable.

Referenced by ReconstructShuffle().

| bool AArch64TargetLowering::isTruncateFree | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if it's free to truncate a value of type Ty1 to type Ty2. e.g. On x86 it's free to truncate a i32 value in register EAX to i16 by referencing its sub-register AX.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6327 of file AArch64ISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), and llvm::Type::isIntegerTy().

| bool AArch64TargetLowering::isTruncateFree | ( | EVT | VT1, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6334 of file AArch64ISelLowering.cpp.

References llvm::EVT::getSizeInBits(), llvm::EVT::isInteger(), and llvm::EVT::isVector().

| bool AArch64TargetLowering::isZExtFree | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if any actual instruction that defines a value of type Ty1 implicitly zero-extends the value to Ty2 in the result register.

This does not necessarily include registers defined in unknown ways, such as incoming arguments, or copies from unknown virtual registers. Also, if isTruncateFree(Ty2, Ty1) is true, this does not necessarily apply to truncate instructions. e.g. on x86-64, all instructions that define 32-bit values implicit zero-extend the result out to 64 bits.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6344 of file AArch64ISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), and llvm::Type::isIntegerTy().

Referenced by isZExtFree().

| bool AArch64TargetLowering::isZExtFree | ( | EVT | VT1, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6351 of file AArch64ISelLowering.cpp.

References llvm::EVT::getSizeInBits(), llvm::EVT::isInteger(), and llvm::EVT::isVector().

| bool AArch64TargetLowering::isZExtFree | ( | SDValue | Val, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Return true if zero-extending the specific node Val to type VT2 is free (either because it's implicitly zero-extended such as ARM ldrb / ldrh or because it's folded such as X86 zero-extending loads).

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6359 of file AArch64ISelLowering.cpp.

References llvm::SDValue::getOpcode(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::EVT::isInteger(), llvm::EVT::isSimple(), llvm::EVT::isVector(), isZExtFree(), and llvm::ISD::LOAD.

| SDValue AArch64TargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerOperation - Provide custom lowering hooks for some operations.

Reimplemented from llvm::TargetLowering.

Definition at line 1671 of file AArch64ISelLowering.cpp.

References llvm::RTLIB::ADD_F128, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::ISD::AND, llvm::ISD::BITCAST, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::BUILD_VECTOR, llvm::ISD::ConstantPool, llvm::ISD::CTPOP, llvm::RTLIB::DIV_F128, llvm::ISD::EXTRACT_SUBVECTOR, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::ISD::FADD, llvm::ISD::FCOPYSIGN, llvm::ISD::FDIV, llvm::ISD::FMUL, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FRAMEADDR, llvm::ISD::FSINCOS, llvm::ISD::FSUB, llvm::SDValue::getOpcode(), llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::JumpTable, llvm_unreachable, LowerADDC_ADDE_SUBC_SUBE(), LowerBITCAST(), LowerPREFETCH(), LowerXALUO(), LowerXOR(), llvm::RTLIB::MUL_F128, llvm::ISD::OR, llvm::ISD::PREFETCH, llvm::ISD::RETURNADDR, llvm::ISD::SADDO, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::ISD::SETCC, llvm::ISD::SHL, llvm::ISD::SHL_PARTS, llvm::ISD::SINT_TO_FP, llvm::ISD::SMULO, llvm::ISD::SRA, llvm::ISD::SRA_PARTS, llvm::ISD::SRL, llvm::ISD::SRL_PARTS, llvm::ISD::SSUBO, llvm::RTLIB::SUB_F128, llvm::ISD::SUBC, llvm::ISD::SUBE, llvm::ISD::UADDO, llvm::ISD::UINT_TO_FP, llvm::ISD::UMULO, llvm::ISD::USUBO, llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VASTART, llvm::ISD::VECTOR_SHUFFLE, and llvm::ISD::XOR.

| SDValue AArch64TargetLowering::PerformDAGCombine | ( | SDNode * | N, |

| DAGCombinerInfo & | DCI | ||

| ) | const [override, virtual] |

This method will be invoked for all target nodes and for any target-independent nodes that the target has registered with invoke it for.

The semantics are as follows: Return Value: SDValue.Val == 0 - No change was made SDValue.Val == N - N was replaced, is dead, and is already handled. otherwise - N should be replaced by the returned Operand.

In addition, methods provided by DAGCombinerInfo may be used to perform more complex transformations.

Reimplemented from llvm::TargetLowering.

Definition at line 8311 of file AArch64ISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::ANY_EXTEND, llvm::ISD::BITCAST, llvm::AArch64ISD::BRCOND, llvm::ISD::CONCAT_VECTORS, llvm::AArch64ISD::CSEL, llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::AArch64ISD::DUP, llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::ISD::MUL, llvm::ISD::OR, performAddSubLongCombine(), performBitcastCombine(), performBRCONDCombine(), performConcatVectorsCombine(), performCONDCombine(), performExtendCombine(), performIntrinsicCombine(), performIntToFpCombine(), performMulCombine(), performNEONPostLDSTCombine(), performORCombine(), performPostLD1Combine(), performSelectCombine(), performSTORECombine(), performVSelectCombine(), performXorCombine(), llvm::ISD::SELECT, llvm::ISD::SIGN_EXTEND, llvm::ISD::SINT_TO_FP, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ISD::UINT_TO_FP, llvm::ISD::VSELECT, llvm::ISD::XOR, and llvm::ISD::ZERO_EXTEND.

| SDValue AArch64TargetLowering::ReconstructShuffle | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 4315 of file AArch64ISelLowering.cpp.

References llvm::SmallVectorTemplateCommon< T >::begin(), llvm::ISD::BITCAST, llvm::EVT::bitsLT(), llvm::ISD::BUILD_VECTOR, llvm::ISD::CONCAT_VECTORS, DEBUG, llvm::SmallVectorTemplateCommon< T >::end(), llvm::AArch64ISD::EXT, llvm::ISD::EXTRACT_SUBVECTOR, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), getExtFactor(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::SelectionDAG::getVectorShuffle(), llvm::EVT::getVectorVT(), llvm::MVT::i32, isShuffleMaskLegal(), llvm::operator==(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SmallVectorTemplateCommon< T >::size(), llvm::Sched::Source, and llvm::ISD::UNDEF.

| bool AArch64TargetLowering::shouldConvertConstantLoadToIntImm | ( | const APInt & | Imm, |

| Type * | Ty | ||

| ) | const [override, virtual] |

Returns true if it is beneficial to convert a load of a constant to just the constant itself.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 6549 of file AArch64ISelLowering.cpp.

References llvm::countLeadingZeros(), llvm::Type::getPrimitiveSizeInBits(), llvm::APInt::getSExtValue(), llvm::Type::isIntegerTy(), and llvm::AArch64_AM::isLogicalImmediate().

| bool AArch64TargetLowering::shouldExpandAtomicLoadInIR | ( | LoadInst * | LI | ) | const [override, virtual] |

Returns true if the given (atomic) load should be expanded by the IR-level AtomicExpand pass into a load-linked instruction (through emitLoadLinked()).

Reimplemented from llvm::TargetLoweringBase.

Definition at line 8563 of file AArch64ISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), and llvm::Value::getType().

| bool AArch64TargetLowering::shouldExpandAtomicRMWInIR | ( | AtomicRMWInst * | RMWI | ) | const [override, virtual] |

Returns true if the given AtomicRMW should be expanded by the IR-level AtomicExpand pass into a loop using LoadLinked/StoreConditional.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 8569 of file AArch64ISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), and llvm::Value::getType().

| bool AArch64TargetLowering::shouldExpandAtomicStoreInIR | ( | StoreInst * | SI | ) | const [override, virtual] |

Returns true if the given (atomic) store should be expanded by the IR-level AtomicExpand pass into an "atomic xchg" which ignores its input.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 8555 of file AArch64ISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), and llvm::StoreInst::getValueOperand().

| bool AArch64TargetLowering::useLoadStackGuardNode | ( | ) | const [override, virtual] |

If this function returns true, SelectionDAGBuilder emits a LOAD_STACK_GUARD node when it is lowering Intrinsic::stackprotector.

Reimplemented from llvm::TargetLowering.

Definition at line 8536 of file AArch64ISelLowering.cpp.

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1