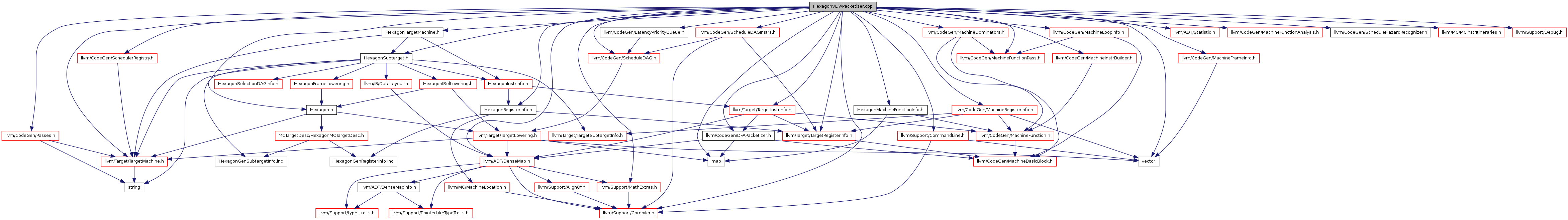

#include "llvm/CodeGen/DFAPacketizer.h"#include "Hexagon.h"#include "HexagonMachineFunctionInfo.h"#include "HexagonRegisterInfo.h"#include "HexagonSubtarget.h"#include "HexagonTargetMachine.h"#include "llvm/ADT/DenseMap.h"#include "llvm/ADT/Statistic.h"#include "llvm/CodeGen/LatencyPriorityQueue.h"#include "llvm/CodeGen/MachineDominators.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineFunctionAnalysis.h"#include "llvm/CodeGen/MachineFunctionPass.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineLoopInfo.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/Passes.h"#include "llvm/CodeGen/ScheduleDAG.h"#include "llvm/CodeGen/ScheduleDAGInstrs.h"#include "llvm/CodeGen/ScheduleHazardRecognizer.h"#include "llvm/CodeGen/SchedulerRegistry.h"#include "llvm/MC/MCInstrItineraries.h"#include "llvm/Support/CommandLine.h"#include "llvm/Support/Compiler.h"#include "llvm/Support/Debug.h"#include "llvm/Support/MathExtras.h"#include "llvm/Target/TargetInstrInfo.h"#include "llvm/Target/TargetMachine.h"#include "llvm/Target/TargetRegisterInfo.h"#include <map>#include <vector>

Go to the source code of this file.

Define Documentation

| #define DEBUG_TYPE "packets" |

Definition at line 53 of file HexagonVLIWPacketizer.cpp.

Enumeration Type Documentation

| enum PredicateKind |

Definition at line 454 of file HexagonVLIWPacketizer.cpp.

Function Documentation

| static bool DoesModifyCalleeSavedReg | ( | MachineInstr * | MI, |

| const TargetRegisterInfo * | TRI | ||

| ) | [static] |

DoesModifyCalleeSavedReg - Returns true if the instruction modifies a callee-saved register.

Definition at line 391 of file HexagonVLIWPacketizer.cpp.

References llvm::TargetRegisterInfo::getCalleeSavedRegs(), and llvm::MachineInstr::modifiesRegister().

| static MachineOperand& GetPostIncrementOperand | ( | MachineInstr * | MI, |

| const HexagonInstrInfo * | QII | ||

| ) | [static] |

Definition at line 473 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getDesc(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDef(), llvm::HexagonInstrInfo::isPostIncrement(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), llvm_unreachable, llvm::MCInstrDesc::mayLoad(), and llvm::MCInstrDesc::mayStore().

| static unsigned getPredicatedRegister | ( | MachineInstr * | MI, |

| const HexagonInstrInfo * | QII | ||

| ) | [static] |

Gets the predicate register of a predicated instruction.

We use the following rule: The first predicate register that is a use is the predicate register of a predicated instruction.

Definition at line 840 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineOperand::getReg(), llvm::HexagonInstrInfo::isPredicated(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), llvm_unreachable, llvm::MachineInstr::operands_begin(), and llvm::MachineInstr::operands_end().

| static PredicateKind getPredicateSense | ( | MachineInstr * | MI, |

| const HexagonInstrInfo * | QII | ||

| ) | [static] |

Returns true if an instruction is predicated on p0 and false if it's predicated on !p0.

Definition at line 462 of file HexagonVLIWPacketizer.cpp.

References llvm::HexagonInstrInfo::isPredicated(), llvm::HexagonInstrInfo::isPredicatedTrue(), PK_False, PK_True, and PK_Unknown.

| static MachineOperand& GetStoreValueOperand | ( | MachineInstr * | MI | ) | [static] |

Definition at line 513 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getNumOperands(), and llvm::MachineInstr::getOperand().

| INITIALIZE_PASS_BEGIN | ( | HexagonPacketizer | , |

| "packets" | , | ||

| "Hexagon Packetizer" | , | ||

| false | , | ||

| false | |||

| ) |

| static bool IsControlFlow | ( | MachineInstr * | MI | ) | [static] |

Definition at line 380 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::isCall(), and llvm::MCInstrDesc::isTerminator().

| static bool IsDirectJump | ( | MachineInstr * | MI | ) | [static] |

Definition at line 368 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode().

| static bool IsIndirectCall | ( | MachineInstr * | MI | ) | [static] |

Definition at line 266 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode().

| static bool IsLoopN | ( | MachineInstr * | MI | ) | [static] |

Definition at line 384 of file HexagonVLIWPacketizer.cpp.

References llvm::MachineInstr::getOpcode().

| static bool IsRegDependence | ( | const SDep::Kind | DepType | ) | [static] |

Definition at line 363 of file HexagonVLIWPacketizer.cpp.

References llvm::SDep::Anti, llvm::SDep::Data, and llvm::SDep::Output.

| static bool IsSchedBarrier | ( | MachineInstr * | MI | ) | [static] |

Definition at line 372 of file HexagonVLIWPacketizer.cpp.

References llvm::HexagonISD::BARRIER, and llvm::MachineInstr::getOpcode().

Variable Documentation

| Hexagon false |

Definition at line 180 of file HexagonVLIWPacketizer.cpp.

| Hexagon Packetizer |

Definition at line 180 of file HexagonVLIWPacketizer.cpp.

cl::opt<bool> PacketizeVolatiles("hexagon-packetize-volatiles", cl::ZeroOrMore, cl::Hidden, cl::init(true), cl::desc("Allow non-solo packetization of volatile memory references")) [static] |

Definition at line 180 of file HexagonVLIWPacketizer.cpp.

1.7.6.1

1.7.6.1