#include <MachineOperand.h>

Detailed Description

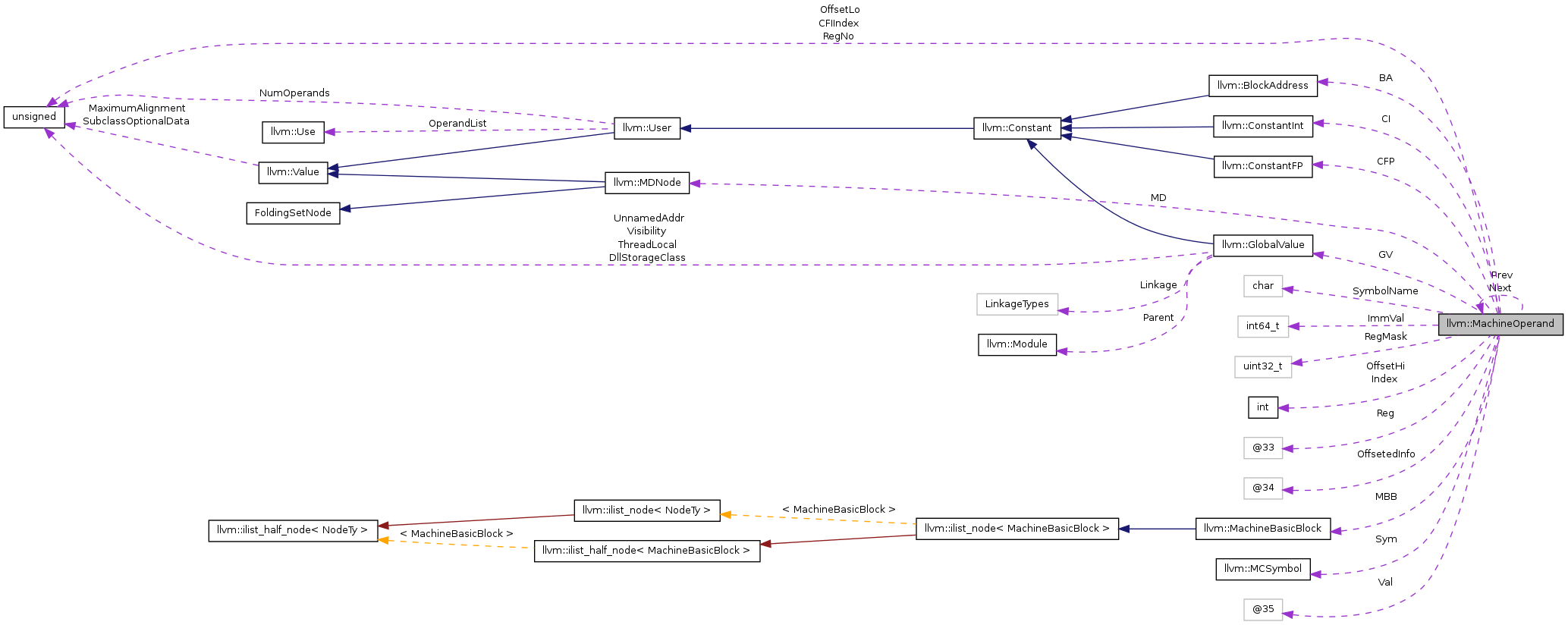

MachineOperand class - Representation of each machine instruction operand.

This class isn't a POD type because it has a private constructor, but its destructor must be trivial. Functions like MachineInstr::addOperand(), MachineRegisterInfo::moveOperands(), and MF::DeleteMachineInstr() depend on not having to call the MachineOperand destructor.

Definition at line 43 of file MachineOperand.h.

Member Enumeration Documentation

- Enumerator:

MO_Register Register operand.

MO_Immediate Immediate operand.

MO_CImmediate Immediate >64bit operand.

MO_FPImmediate Floating-point immediate operand.

MO_MachineBasicBlock MachineBasicBlock reference.

MO_FrameIndex Abstract Stack Frame Index.

MO_ConstantPoolIndex MO_TargetIndex Target-dependent index+offset operand.

MO_JumpTableIndex Address of indexed Jump Table for switch.

MO_ExternalSymbol Name of external global symbol.

MO_GlobalAddress Address of a global value.

MO_BlockAddress Address of a basic block.

MO_RegisterMask Mask of preserved registers.

MO_RegisterLiveOut Mask of live-out registers.

MO_Metadata Metadata reference (for debug info)

MO_MCSymbol MCSymbol reference (for debug/eh info)

MO_CFIIndex MCCFIInstruction index.

Definition at line 45 of file MachineOperand.h.

Member Function Documentation

| void llvm::MachineOperand::addTargetFlag | ( | unsigned | F | ) | [inline] |

Definition at line 198 of file MachineOperand.h.

Referenced by llvm::HexagonInstrInfo::immediateExtend().

| void MachineOperand::ChangeToImmediate | ( | int64_t | ImmVal | ) |

ChangeToImmediate - Replace this operand with a new immediate operand of the specified value. If an operand is known to be an immediate already, the setImm method should be used.

Definition at line 112 of file MachineInstr.cpp.

References llvm::MachineBasicBlock::getParent(), getParent(), ImmVal, isReg(), isTied(), MBB, llvm::AArch64CC::MI, and MO_Immediate.

Referenced by llvm::SIInstrInfo::commuteInstruction(), llvm::SIRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::Thumb1RegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseInstrInfo::FoldImmediate(), foldImmediates(), llvm::HexagonInstrInfo::PredicateInstruction(), replaceFI(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::rewriteAArch64FrameIndex(), llvm::rewriteARMFrameIndex(), llvm::Thumb1RegisterInfo::rewriteFrameIndex(), and llvm::rewriteT2FrameIndex().

| void MachineOperand::ChangeToRegister | ( | unsigned | Reg, |

| bool | isDef, | ||

| bool | isImp = false, |

||

| bool | isKill = false, |

||

| bool | isDead = false, |

||

| bool | isUndef = false, |

||

| bool | isDebug = false |

||

| ) |

ChangeToRegister - Replace this operand with a new register operand of the specified value. If an operand is known to be an register already, the setReg method should be used.

Definition at line 129 of file MachineInstr.cpp.

References llvm::MachineRegisterInfo::addRegOperandToUseList(), llvm::MachineBasicBlock::getParent(), getParent(), isDead(), isDebug(), isDef(), isKill(), isReg(), isUndef(), MBB, llvm::AArch64CC::MI, MO_Register, Reg, and llvm::MachineRegisterInfo::removeRegOperandFromUseList().

Referenced by llvm::SIInstrInfo::commuteInstruction(), llvm::SIRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::SystemZRegisterInfo::eliminateFrameIndex(), llvm::Thumb1RegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), llvm::SIInstrInfo::legalizeOpWithMove(), llvm::SIInstrInfo::moveSMRDToVALU(), llvm::HexagonInstrInfo::PredicateInstruction(), replaceFI(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::rewriteAArch64FrameIndex(), llvm::rewriteARMFrameIndex(), llvm::Thumb1RegisterInfo::rewriteFrameIndex(), and llvm::rewriteT2FrameIndex().

| void llvm::MachineOperand::clearParent | ( | ) | [inline] |

clearParent - Reset the parent pointer.

The MachineOperand copy constructor also copies ParentMI, expecting the original to be deleted. If a MachineOperand is ever stored outside a MachineInstr, the parent pointer must be cleared.

Never call clearParent() on an operand in a MachineInstr.

Definition at line 218 of file MachineOperand.h.

| static bool llvm::MachineOperand::clobbersPhysReg | ( | const uint32_t * | RegMask, |

| unsigned | PhysReg | ||

| ) | [inline, static] |

clobbersPhysReg - Returns true if this RegMask clobbers PhysReg. It is sometimes necessary to detach the register mask pointer from its machine operand. This static method can be used for such detached bit mask pointers.

Definition at line 471 of file MachineOperand.h.

Referenced by llvm::MachineOperandIteratorBase::analyzePhysReg(), callClobbersAnyYmmReg(), canClobberPhysRegDefs(), canClobberReachingPhysRegUse(), CheckForLiveRegDefMasked(), clobbersAllYmmRegs(), clobbersCTR(), clobbersPhysReg(), llvm::ARMBaseInstrInfo::DefinesPredicate(), llvm::PPCInstrInfo::DefinesPredicate(), llvm::MachineInstr::findRegisterDefOperandIdx(), initReachingDef(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::LivePhysRegs::removeRegsInMask(), and llvm::Thumb1RegisterInfo::saveScavengerRegister().

| bool llvm::MachineOperand::clobbersPhysReg | ( | unsigned | PhysReg | ) | const [inline] |

clobbersPhysReg - Returns true if this RegMask operand clobbers PhysReg.

Definition at line 478 of file MachineOperand.h.

References clobbersPhysReg(), and getRegMask().

| static MachineOperand llvm::MachineOperand::CreateBA | ( | const BlockAddress * | BA, |

| int64_t | Offset, | ||

| unsigned char | TargetFlags = 0 |

||

| ) | [inline, static] |

Definition at line 652 of file MachineOperand.h.

References BA, MO_BlockAddress, OffsetedInfo, setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addBlockAddress().

| static MachineOperand llvm::MachineOperand::CreateCFIIndex | ( | unsigned | CFIIndex | ) | [inline, static] |

Definition at line 696 of file MachineOperand.h.

References CFIIndex, and MO_CFIIndex.

Referenced by llvm::MachineInstrBuilder::addCFIIndex().

| static MachineOperand llvm::MachineOperand::CreateCImm | ( | const ConstantInt * | CI | ) | [inline, static] |

Definition at line 564 of file MachineOperand.h.

References CI, and MO_CImmediate.

Referenced by llvm::MachineInstrBuilder::addCImm().

| static MachineOperand llvm::MachineOperand::CreateCPI | ( | unsigned | Idx, |

| int | Offset, | ||

| unsigned char | TargetFlags = 0 |

||

| ) | [inline, static] |

Definition at line 613 of file MachineOperand.h.

References MO_ConstantPoolIndex, setIndex(), setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addConstantPoolIndex().

| static MachineOperand llvm::MachineOperand::CreateES | ( | const char * | SymName, |

| unsigned char | TargetFlags = 0 |

||

| ) | [inline, static] |

Definition at line 644 of file MachineOperand.h.

References MO_ExternalSymbol, OffsetedInfo, setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addExternalSymbol().

| static MachineOperand llvm::MachineOperand::CreateFI | ( | int | Idx | ) | [inline, static] |

Definition at line 608 of file MachineOperand.h.

References MO_FrameIndex, and setIndex().

Referenced by llvm::MachineInstrBuilder::addFrameIndex(), llvm::X86AddressMode::getFullAddress(), and llvm::FastISel::selectIntrinsicCall().

| static MachineOperand llvm::MachineOperand::CreateFPImm | ( | const ConstantFP * | CFP | ) | [inline, static] |

Definition at line 570 of file MachineOperand.h.

References CFP, and MO_FPImmediate.

Referenced by llvm::MachineInstrBuilder::addFPImm().

| static MachineOperand llvm::MachineOperand::CreateGA | ( | const GlobalValue * | GV, |

| int64_t | Offset, | ||

| unsigned char | TargetFlags = 0 |

||

| ) | [inline, static] |

Definition at line 636 of file MachineOperand.h.

References GV, MO_GlobalAddress, OffsetedInfo, setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addGlobalAddress(), and llvm::X86AddressMode::getFullAddress().

| static MachineOperand llvm::MachineOperand::CreateImm | ( | int64_t | Val | ) | [inline, static] |

Definition at line 558 of file MachineOperand.h.

References MO_Immediate, and setImm().

Referenced by llvm::MachineInstrBuilder::addImm(), llvm::XCoreInstrInfo::AnalyzeBranch(), llvm::HexagonInstrInfo::AnalyzeBranch(), llvm::SparcInstrInfo::AnalyzeBranch(), llvm::MSP430InstrInfo::AnalyzeBranch(), llvm::PPCInstrInfo::AnalyzeBranch(), llvm::SystemZInstrInfo::AnalyzeBranch(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::X86AddressMode::getFullAddress(), llvm::SIInstrInfo::moveSMRDToVALU(), llvm::SIInstrInfo::moveToVALU(), parseCondBranch(), llvm::HexagonInstrInfo::ReverseBranchCondition(), llvm::FastISel::selectPatchpoint(), and llvm::FastISel::selectStackmap().

| static MachineOperand llvm::MachineOperand::CreateJTI | ( | unsigned | Idx, |

| unsigned char | TargetFlags = 0 |

||

| ) | [inline, static] |

Definition at line 629 of file MachineOperand.h.

References MO_JumpTableIndex, setIndex(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addJumpTableIndex().

| static MachineOperand llvm::MachineOperand::CreateMBB | ( | MachineBasicBlock * | MBB, |

| unsigned char | TargetFlags = 0 |

||

| ) | [inline, static] |

Definition at line 601 of file MachineOperand.h.

References MO_MachineBasicBlock, setMBB(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addMBB().

| static MachineOperand llvm::MachineOperand::CreateMCSymbol | ( | MCSymbol * | Sym | ) | [inline, static] |

Definition at line 690 of file MachineOperand.h.

References MO_MCSymbol, and Sym.

Referenced by llvm::MachineInstrBuilder::addSym().

| static MachineOperand llvm::MachineOperand::CreateMetadata | ( | const MDNode * | Meta | ) | [inline, static] |

Definition at line 684 of file MachineOperand.h.

References MD, and MO_Metadata.

Referenced by llvm::MachineInstrBuilder::addMetadata().

| static MachineOperand llvm::MachineOperand::CreateReg | ( | unsigned | Reg, |

| bool | isDef, | ||

| bool | isImp = false, |

||

| bool | isKill = false, |

||

| bool | isDead = false, |

||

| bool | isUndef = false, |

||

| bool | isEarlyClobber = false, |

||

| unsigned | SubReg = 0, |

||

| bool | isDebug = false, |

||

| bool | isInternalRead = false |

||

| ) | [inline, static] |

Definition at line 576 of file MachineOperand.h.

References isDead(), isDebug(), isDef(), isEarlyClobber(), isInternalRead(), isKill(), isUndef(), MO_Register, Reg, RegNo, and setSubReg().

Referenced by llvm::MachineInstrBuilder::addReg(), llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterDefined(), llvm::MachineInstr::addRegisterKilled(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::PPCInstrInfo::AnalyzeBranch(), llvm::R600InstrInfo::AnalyzeBranch(), llvm::X86AddressMode::getFullAddress(), INITIALIZE_PASS(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::rewriteT2FrameIndex(), llvm::FastISel::selectIntrinsicCall(), llvm::FastISel::selectPatchpoint(), llvm::FastISel::selectStackmap(), and llvm::tryFoldSPUpdateIntoPushPop().

| static MachineOperand llvm::MachineOperand::CreateRegLiveOut | ( | const uint32_t * | Mask | ) | [inline, static] |

Definition at line 678 of file MachineOperand.h.

References MO_RegisterLiveOut, and RegMask.

| static MachineOperand llvm::MachineOperand::CreateRegMask | ( | const uint32_t * | Mask | ) | [inline, static] |

CreateRegMask - Creates a register mask operand referencing Mask. The operand does not take ownership of the memory referenced by Mask, it must remain valid for the lifetime of the operand.

A RegMask operand represents a set of non-clobbered physical registers on an instruction that clobbers many registers, typically a call. The bit mask has a bit set for each physreg that is preserved by this instruction, as described in the documentation for TargetRegisterInfo::getCallPreservedMask().

Any physreg with a 0 bit in the mask is clobbered by the instruction.

Definition at line 672 of file MachineOperand.h.

References MO_RegisterMask, and RegMask.

Referenced by llvm::MachineInstrBuilder::addRegMask(), and llvm::FastISel::selectPatchpoint().

| static MachineOperand llvm::MachineOperand::CreateTargetIndex | ( | unsigned | Idx, |

| int64_t | Offset, | ||

| unsigned char | TargetFlags = 0 |

||

| ) | [inline, static] |

Definition at line 621 of file MachineOperand.h.

References MO_TargetIndex, setIndex(), setOffset(), and setTargetFlags().

Referenced by llvm::MachineInstrBuilder::addTargetIndex().

| const BlockAddress* llvm::MachineOperand::getBlockAddress | ( | ) | const [inline] |

Definition at line 438 of file MachineOperand.h.

References isBlockAddress().

Referenced by llvm::MSP430MCInstLower::GetBlockAddressSymbol(), llvm::SystemZMCInstLower::getExpr(), llvm::hash_value(), llvm::HexagonLowerToMC(), isIdenticalTo(), llvm::AArch64MCInstLower::lowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineInstrToMCInst(), LowerSymbolOperand(), and llvm::MipsAsmPrinter::printOperand().

| unsigned llvm::MachineOperand::getCFIIndex | ( | ) | const [inline] |

Definition at line 448 of file MachineOperand.h.

References isCFIIndex().

Referenced by llvm::AsmPrinter::emitCFIInstruction(), llvm::hash_value(), and isIdenticalTo().

| const ConstantInt* llvm::MachineOperand::getCImm | ( | ) | const [inline] |

Definition at line 412 of file MachineOperand.h.

References isCImm().

Referenced by emitDebugValueComment(), getDebugLocValue(), llvm::hash_value(), and isIdenticalTo().

| const ConstantFP* llvm::MachineOperand::getFPImm | ( | ) | const [inline] |

Definition at line 417 of file MachineOperand.h.

References isFPImm().

Referenced by llvm::DwarfUnit::addConstantFPValue(), compareMachineOp(), emitDebugValueComment(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), foldImmediates(), getDebugLocValue(), llvm::hash_value(), llvm::HexagonLowerToMC(), isIdenticalTo(), llvm::SIInstrInfo::isInlineConstant(), and llvm::ARMAsmPrinter::lowerOperand().

| const GlobalValue* llvm::MachineOperand::getGlobal | ( | ) | const [inline] |

Definition at line 433 of file MachineOperand.h.

References isGlobal().

Referenced by llvm::MachineInstrBuilder::addDisp(), llvm::X86FrameLowering::adjustForHiPEPrologue(), llvm::EHStreamer::callToNoUnwindFunction(), llvm::ARMFrameLowering::emitEpilogue(), llvm::PPCFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::SystemZMCInstLower::getExpr(), llvm::MSP430MCInstLower::GetGlobalAddressSymbol(), llvm::AArch64MCInstLower::GetGlobalAddressSymbol(), GetSymbolFromOperand(), llvm::hash_value(), llvm::HexagonLowerToMC(), isIdenticalTo(), llvm::ARMAsmPrinter::lowerOperand(), LowerSymbolOperand(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printSymbolOperand(), and llvm::ARMBaseInstrInfo::produceSameValue().

| int64_t llvm::MachineOperand::getImm | ( | ) | const [inline] |

Definition at line 407 of file MachineOperand.h.

References isImm().

Referenced by llvm::DwarfUnit::addConstantValue(), llvm::MachineInstrBuilder::addDisp(), llvm::R600InstrInfo::addFlag(), adjustDefLatency(), llvm::SITargetLowering::AdjustInstrPostInstrSelection(), llvm::HexagonInstrInfo::analyzeCompare(), llvm::SystemZInstrInfo::analyzeCompare(), llvm::AArch64InstrInfo::analyzeCompare(), llvm::PPCInstrInfo::analyzeCompare(), llvm::ARMBaseInstrInfo::analyzeCompare(), llvm::R600InstrInfo::buildSlotOfVectorInstruction(), canCompareBeNewValueJump(), canFoldIntoCSel(), canShrink(), llvm::R600InstrInfo::clearFlag(), llvm::SIInstrInfo::commuteInstruction(), llvm::PPCInstrInfo::commuteInstruction(), compareMachineOp(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::SystemZInstrInfo::convertToThreeAddress(), llvm::SparcFrameLowering::eliminateCallFramePseudoInstr(), llvm::MSP430FrameLowering::eliminateCallFramePseudoInstr(), llvm::XCoreFrameLowering::eliminateCallFramePseudoInstr(), llvm::Thumb1FrameLowering::eliminateCallFramePseudoInstr(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), emitDebugValueComment(), llvm::PPCFrameLowering::emitEpilogue(), llvm::AArch64FrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::AArch64TargetLowering::EmitF128CSEL(), EmitGCCInlineAsmStr(), llvm::SystemZAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::X86AsmPrinter::EmitInstruction(), llvm::MipsAsmPrinter::EmitInstruction(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), llvm::ARMAsmPrinter::EmitJump2Table(), llvm::ARMAsmPrinter::EmitJumpTable(), EmitMSInlineAsmStr(), llvm::SparcTargetLowering::expandSelectCC(), llvm::MachineInstr::findInlineAsmFlagIdx(), llvm::MachineInstr::findTiedOperandIdx(), llvm::PPCInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), foldImmediates(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), llvm::AArch64InstrInfo::genAlternativeCodeSequence(), llvm::SystemZInstrInfo::getBranchInfo(), llvm::SystemZInstrInfo::getCompareAndBranch(), getDebugLocValue(), llvm::TargetInstrInfo::getExtractSubregInputs(), llvm::ARMBaseRegisterInfo::getFrameIndexInstrOffset(), llvm::TargetInstrInfo::getInsertSubregInputs(), llvm::ARMBaseInstrInfo::getInsertSubregLikeInputs(), llvm::getInstrPredicate(), llvm::MipsInstrInfo::GetInstSizeInBytes(), llvm::ARMBaseInstrInfo::GetInstSizeInBytes(), llvm::SIInstrInfo::getLdStBaseRegImmOfs(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfs(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfsWidth(), llvm::NVPTXInstrInfo::getLdStCodeAddrSpace(), getMemoryOpOffset(), getNumMicroOpsSwiftLdSt(), llvm::ARMBaseInstrInfo::getPredicate(), llvm::TargetInstrInfo::getRegSequenceInputs(), getSrcFromCopy(), llvm::R600InstrInfo::getSrcs(), getTruncatedShiftCount(), llvm::PatchPointOpers::getVarIdx(), llvm::AArch64InstrInfo::hasExtendedReg(), llvm::hash_value(), HashMachineInstr(), llvm::AArch64InstrInfo::hasShiftedReg(), llvm::HexagonLowerToMC(), INITIALIZE_PASS(), invertBccCondition(), llvm::isAArch64FrameOffsetLegal(), llvm::AArch64InstrInfo::isAsCheapAsAMove(), llvm::AArch64InstrInfo::isCoalescableExtInstr(), isCompareZero(), llvm::HexagonInstrInfo::isConstExtended(), llvm::PPCRegisterInfo::isFrameOffsetLegal(), llvm::AArch64InstrInfo::isGPRCopy(), llvm::AArch64InstrInfo::isGPRZero(), isGreaterThan6BitTFRI(), isGreaterThan8BitTFRI(), isIdenticalTo(), llvm::SIInstrInfo::isInlineConstant(), llvm::HexagonInstrInfo::isLoadFromStackSlot(), llvm::SparcInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::PPCInstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), isMatchingDecrement(), isMatchingIncrement(), isMatchingUpdateInsn(), llvm::isParamLoad(), llvm::HexagonInstrInfo::isPredicable(), llvm::R600InstrInfo::isPredicable(), llvm::ARMBaseInstrInfo::isPredicated(), isRedundantFlagInstr(), llvm::isScale(), llvm::AArch64InstrInfo::isScaledAddr(), isShift(), isSimpleBD12Move(), isSimpleMove(), llvm::SystemZInstrInfo::isStackSlotCopy(), llvm::HexagonInstrInfo::isStoreToStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::SparcInstrInfo::isStoreToStackSlot(), llvm::PPCInstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), isSuitableForMask(), llvm::ARMBaseInstrInfo::isSwiftFastImmShift(), isZeroImm(), llvm::MipsInstrInfo::isZeroImm(), llvm::SIInstrInfo::legalizeOperands(), llvm::MSP430MCInstLower::Lower(), llvm::XCoreMCInstLower::LowerOperand(), llvm::MipsMCInstLower::LowerOperand(), llvm::SystemZMCInstLower::lowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineInstrToMCInst(), lowerRIEfLow(), lowerRIHigh(), lowerRILow(), llvm::MachineInstr::mayLoad(), llvm::MachineInstr::mayStore(), llvm::SIInstrInfo::moveSMRDToVALU(), llvm::SIInstrInfo::moveToVALU(), llvm::PPCRegisterInfo::needsFrameBaseReg(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeSelect(), llvm::HexagonInstrInfo::PredicateInstruction(), llvm::MachineInstr::print(), llvm::SystemZAsmPrinter::PrintAsmMemoryOperand(), llvm::HexagonAsmPrinter::PrintAsmMemoryOperand(), llvm::SystemZAsmPrinter::PrintAsmOperand(), llvm::ARMAsmPrinter::PrintAsmOperand(), llvm::X86AsmPrinter::PrintAsmOperand(), llvm::MipsAsmPrinter::PrintAsmOperand(), llvm::AsmPrinter::PrintAsmOperand(), llvm::MipsAsmPrinter::printFCCOperand(), printIntelMemReference(), printLeaMemReference(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printOperand(), printPCRelImm(), llvm::MipsAsmPrinter::printUnsignedImm(), llvm::MipsAsmPrinter::printUnsignedImm8(), llvm::StackMaps::recordStackMap(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::R600InstrInfo::ReverseBranchCondition(), llvm::rewriteAArch64FrameIndex(), llvm::rewriteARMFrameIndex(), llvm::Thumb1RegisterInfo::rewriteFrameIndex(), llvm::rewriteT2FrameIndex(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::AArch64InstrInfo::shouldClusterLoads(), and llvm::SIInstrInfo::splitSMRD().

| int llvm::MachineOperand::getIndex | ( | ) | const [inline] |

Definition at line 427 of file MachineOperand.h.

References isCPI(), isFI(), isJTI(), and isTargetIndex().

Referenced by llvm::ARMBaseInstrInfo::duplicate(), llvm::SIRegisterInfo::eliminateFrameIndex(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::NVPTXRegisterInfo::eliminateFrameIndex(), llvm::Thumb1RegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::MipsRegisterInfo::eliminateFrameIndex(), llvm::AArch64RegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), emitDebugValueComment(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::X86AsmPrinter::EmitInstruction(), llvm::MipsAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitJump2Table(), llvm::ARMAsmPrinter::EmitJumpTable(), llvm::TargetLoweringBase::emitPatchPoint(), llvm::MSP430MCInstLower::GetConstantPoolIndexSymbol(), llvm::SystemZMCInstLower::getExpr(), llvm::ARMBaseInstrInfo::GetInstSizeInBytes(), llvm::MSP430MCInstLower::GetJumpTableSymbol(), llvm::hash_value(), HashMachineInstr(), llvm::HexagonLowerToMC(), isIdenticalTo(), llvm::MipsSEInstrInfo::isLoadFromStackSlot(), llvm::XCoreInstrInfo::isLoadFromStackSlot(), llvm::HexagonInstrInfo::isLoadFromStackSlot(), llvm::SparcInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::PPCInstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), isSimpleMove(), llvm::SystemZInstrInfo::isStackSlotCopy(), llvm::MipsSEInstrInfo::isStoreToStackSlot(), llvm::XCoreInstrInfo::isStoreToStackSlot(), llvm::HexagonInstrInfo::isStoreToStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::SparcInstrInfo::isStoreToStackSlot(), llvm::PPCInstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), llvm::AArch64MCInstLower::lowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineInstrToMCInst(), LowerSymbolOperand(), MatchingStackOffset(), llvm::BranchFolder::OptimizeFunction(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printSymbolOperand(), llvm::ARMBaseInstrInfo::produceSameValue(), and llvm::ARMBaseInstrInfo::reMaterialize().

| MachineBasicBlock* llvm::MachineOperand::getMBB | ( | ) | const [inline] |

Definition at line 422 of file MachineOperand.h.

References isMBB().

Referenced by llvm::XCoreInstrInfo::AnalyzeBranch(), llvm::HexagonInstrInfo::AnalyzeBranch(), llvm::NVPTXInstrInfo::AnalyzeBranch(), llvm::MipsInstrInfo::AnalyzeBranch(), llvm::PPCInstrInfo::AnalyzeBranch(), llvm::AArch64InstrInfo::AnalyzeBranch(), llvm::SystemZInstrInfo::AnalyzeBranch(), llvm::R600InstrInfo::AnalyzeBranch(), BBIsJumpedOver(), EmitGCCInlineAsmStr(), llvm::LiveRangeCalc::extendToUses(), findCorrespondingPred(), getDestBlock(), llvm::HexagonInstrInfo::getDotNewPredJumpOp(), llvm::SystemZMCInstLower::getExpr(), getPHIDeps(), getPHISrcRegOpIdx(), getTargetMBB(), llvm::hash_value(), HashMachineInstr(), llvm::HexagonLowerToMC(), isIdenticalTo(), llvm::SIInstrInfo::legalizeOperands(), llvm::MSP430MCInstLower::Lower(), llvm::AArch64MCInstLower::lowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineInstrToMCInst(), LowerSymbolOperand(), parseCondBranch(), llvm::PPCInstrInfo::PredicateInstruction(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

| MCSymbol* llvm::MachineOperand::getMCSymbol | ( | ) | const [inline] |

Definition at line 443 of file MachineOperand.h.

References isMCSymbol().

Referenced by llvm::hash_value(), and isIdenticalTo().

| const MDNode* llvm::MachineOperand::getMetadata | ( | ) | const [inline] |

Definition at line 495 of file MachineOperand.h.

References isMetadata().

Referenced by llvm::MachineInstr::emitError(), llvm::MachineInstr::getDebugVariable(), llvm::hash_value(), isIdenticalTo(), and llvm::MachineInstr::print().

| int64_t llvm::MachineOperand::getOffset | ( | ) | const [inline] |

getOffset - Return the offset from the symbol in this operand. This always returns 0 for ExternalSymbol operands.

Definition at line 455 of file MachineOperand.h.

References isBlockAddress(), isCPI(), isGlobal(), isSymbol(), and isTargetIndex().

Referenced by llvm::MachineInstrBuilder::addDisp(), llvm::ARMFrameLowering::emitEpilogue(), llvm::PPCFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::SystemZMCInstLower::getExpr(), GetSymbolRef(), llvm::hash_value(), HashMachineInstr(), isIdenticalTo(), llvm::MSP430MCInstLower::LowerSymbolOperand(), llvm::AArch64MCInstLower::lowerSymbolOperandDarwin(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printSymbolOperand(), and llvm::ARMBaseInstrInfo::produceSameValue().

| MachineInstr* llvm::MachineOperand::getParent | ( | ) | [inline] |

getParent - Return the instruction that this operand belongs to.

Definition at line 207 of file MachineOperand.h.

Referenced by llvm::MachineOperandIteratorBase::analyzeVirtReg(), ChangeToImmediate(), ChangeToRegister(), llvm::MachineInstr::emitError(), llvm::MachineInstr::eraseFromBundle(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::eraseFromParentAndMarkDBGValuesForRemoval(), llvm::MachineRegisterInfo::defusechain_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::getOperandNo(), llvm::MachineInstr::getRegClassConstraint(), GetSymbolRef(), llvm::MachineInstr::isIdenticalTo(), llvm::MachineInstr::isInvariantLoad(), isKilled(), llvm::MachineRegisterInfo::defusechain_instr_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::operator*(), llvm::MachineRegisterInfo::defusechain_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::operator++(), llvm::MachineRegisterInfo::defusechain_instr_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::operator++(), llvm::MachineRegisterInfo::defusechain_instr_iterator< ReturnUses, ReturnDefs, SkipDebug, ByOperand, ByInstr, ByBundle >::operator->(), print(), llvm::MachineInstr::print(), llvm::MachineInstr::removeFromBundle(), llvm::MachineInstr::removeFromParent(), llvm::MachineSSAUpdater::RewriteUse(), setIsDef(), setReg(), llvm::FastISel::tryToFoldLoad(), UpdatePredRedefs(), and llvm::MachineRegisterInfo::verifyUseList().

| const MachineInstr* llvm::MachineOperand::getParent | ( | ) | const [inline] |

Definition at line 208 of file MachineOperand.h.

| unsigned llvm::MachineOperand::getReg | ( | ) | const [inline] |

getReg - Returns the register number.

Definition at line 264 of file MachineOperand.h.

References isReg().

Referenced by addLiveInRegs(), llvm::ScheduleDAGInstrs::addPhysRegDataDeps(), llvm::ScheduleDAGInstrs::addPhysRegDeps(), llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterDefined(), llvm::MachineInstr::addRegisterKilled(), llvm::MachineRegisterInfo::addRegOperandToUseList(), llvm::ScheduleDAGInstrs::addSchedBarrierDeps(), llvm::ScheduleDAGInstrs::addVRegDefDeps(), llvm::ScheduleDAGInstrs::addVRegUseDeps(), llvm::SITargetLowering::AdjustInstrPostInstrSelection(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::HexagonInstrInfo::analyzeCompare(), llvm::SystemZInstrInfo::analyzeCompare(), llvm::AArch64InstrInfo::analyzeCompare(), llvm::PPCInstrInfo::analyzeCompare(), llvm::ARMBaseInstrInfo::analyzeCompare(), llvm::MachineOperandIteratorBase::analyzePhysReg(), llvm::MachineOperandIteratorBase::analyzeVirtReg(), biasPhysRegCopy(), llvm::CriticalAntiDepBreaker::BreakAntiDependencies(), llvm::ARMBaseInstrInfo::breakPartialRegDependency(), llvm::ScheduleDAGInstrs::buildSchedGraph(), llvm::R600InstrInfo::buildSlotOfVectorInstruction(), canCombineWithMUL(), canCompareBeNewValueJump(), canFoldCopy(), canFoldIntoCSel(), canFoldIntoMOVCC(), llvm::MachineInstr::clearRegisterKills(), clobbersCTR(), RegisterOperands::collect(), collectDebugValues(), llvm::SIInstrInfo::commuteInstruction(), llvm::PPCInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), compareMachineOp(), computeOthers(), llvm::TargetSchedModel::computeOutputLatency(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::SystemZInstrInfo::convertToThreeAddress(), copyHint(), llvm::SSAUpdaterTraits< MachineSSAUpdater >::CreateEmptyPHI(), definesCPSR(), llvm::HexagonInstrInfo::DefinesPredicate(), llvm::ARMBaseInstrInfo::DefinesPredicate(), llvm::PPCInstrInfo::DefinesPredicate(), llvm::MSP430RegisterInfo::eliminateFrameIndex(), llvm::XCoreRegisterInfo::eliminateFrameIndex(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::Thumb1RegisterInfo::eliminateFrameIndex(), llvm::HexagonRegisterInfo::eliminateFrameIndex(), llvm::PPCRegisterInfo::eliminateFrameIndex(), llvm::ARMBaseRegisterInfo::eliminateFrameIndex(), llvm::PPCTargetLowering::EmitAtomicBinary(), emitDebugValueComment(), llvm::PPCTargetLowering::emitEHSjLjLongJmp(), llvm::PPCTargetLowering::emitEHSjLjSetJmp(), llvm::ARMFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::AsmPrinter::emitImplicitDef(), llvm::SystemZAsmPrinter::EmitInstruction(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::X86AsmPrinter::EmitInstruction(), llvm::R600TargetLowering::EmitInstrWithCustomInserter(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::XCoreTargetLowering::EmitInstrWithCustomInserter(), llvm::MSP430TargetLowering::EmitInstrWithCustomInserter(), llvm::PPCTargetLowering::EmitInstrWithCustomInserter(), emitKill(), EmitMonitor(), llvm::PPCTargetLowering::EmitPartwordAtomicBinary(), EmitPCMPSTRI(), EmitPCMPSTRM(), llvm::MSP430TargetLowering::EmitShiftInstr(), EmitXBegin(), llvm::MachineInstr::eraseFromParentAndMarkDBGValuesForRemoval(), eraseGPOpnd(), eraseIfDead(), Expand2AddrUndef(), llvm::SparcTargetLowering::expandAtomicRMW(), expandLoadStackGuard(), llvm::SparcTargetLowering::expandSelectCC(), findDeadCallerSavedReg(), findHoistingInsertPosAndDeps(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::MachineInstr::findRegisterUseOperandIdx(), finishConvertToThreeAddress(), llvm::ScheduleDAGInstrs::fixupKills(), llvm::PPCInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), foldImmediates(), llvm::TargetInstrInfo::foldMemoryOperand(), llvm::AArch64InstrInfo::foldMemoryOperandImpl(), llvm::SystemZInstrInfo::foldMemoryOperandImpl(), foldPatchpoint(), forceReg(), llvm::RegScavenger::forward(), genMadd(), genMaddR(), getCallTargetRegOpnd(), getDebugLocValue(), llvm::TargetInstrInfo::getExtractSubregInputs(), llvm::ARMBaseInstrInfo::getExtractSubregLikeInputs(), getFPReg(), llvm::MachineInstrExpressionTrait::getHashValue(), llvm::TargetInstrInfo::getInsertSubregInputs(), llvm::ARMBaseInstrInfo::getInsertSubregLikeInputs(), llvm::getInstrPredicate(), llvm::SIInstrInfo::getLdStBaseRegImmOfs(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfs(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfsWidth(), getNumMicroOpsSwiftLdSt(), llvm::PPCInstrInfo::getOperandLatency(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::SIInstrInfo::getOpRegClass(), llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance(), getPHIDeps(), llvm::SSAUpdaterTraits< MachineSSAUpdater >::GetPHIValue(), GetPostIncrementOperand(), getPredicatedRegister(), llvm::TargetInstrInfo::getRegSequenceInputs(), llvm::ARMBaseInstrInfo::getRegSequenceLikeInputs(), getSrcFromCopy(), llvm::R600InstrInfo::getSrcs(), llvm::SSAUpdaterTraits< MachineSSAUpdater >::GetUndefVal(), llvm::MachineSSAUpdater::GetValueInMiddleOfBlock(), HandleVRSaveUpdate(), llvm::hash_value(), HashMachineInstr(), hasLiveCondCodeDef(), hasRAWHazard(), hasVGPROperands(), hasYmmReg(), llvm::HexagonLowerToMC(), INITIALIZE_PASS(), insertDivByZeroTrap(), isCandidateStore(), llvm::AArch64InstrInfo::isCoalescableExtInstr(), llvm::PPCInstrInfo::isCoalescableExtInstr(), llvm::MachineInstr::isConstantValuePHI(), isCopyToReg(), llvm::IsCPSRDead< MachineInstr >(), isCSRestore(), llvm::isDescribedByReg(), llvm::AArch64InstrInfo::isFPRCopy(), isFullCopyOf(), llvm::AArch64InstrInfo::isGPRCopy(), llvm::AArch64InstrInfo::isGPRZero(), isIdenticalTo(), llvm::MachineInstr::isIdenticalTo(), llvm::MachineInstr::isIdentityCopy(), llvm::MipsSEInstrInfo::isLoadFromStackSlot(), llvm::XCoreInstrInfo::isLoadFromStackSlot(), llvm::HexagonInstrInfo::isLoadFromStackSlot(), llvm::SparcInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::PPCInstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), isLocalCopy(), isMatchingDecrement(), isMatchingIncrement(), isMatchingUpdateInsn(), llvm::NVPTXInstrInfo::isMoveInstr(), isNopCopy(), isOperandKill(), llvm::SIInstrInfo::isOperandLegal(), isPartialRegisterLoad(), isPhysicalRegCopy(), llvm::R600InstrInfo::isPredicated(), isRedundantFlagInstr(), IsSafeAndProfitableToMove(), isShift(), isSimpleBD12Move(), isSimpleMove(), isSourceDefinedByImplicitDef(), llvm::MipsSEInstrInfo::isStoreToStackSlot(), llvm::XCoreInstrInfo::isStoreToStackSlot(), llvm::HexagonInstrInfo::isStoreToStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::SparcInstrInfo::isStoreToStackSlot(), llvm::PPCInstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), isSuitableForMask(), isTwoAddrUse(), isVGPR(), llvm::final< T >::isX86_64ExtendedReg(), llvm::SIInstrInfo::legalizeOperands(), llvm::Mips16InstrInfo::loadImmediate(), llvm::MSP430MCInstLower::Lower(), llvm::PPCRegisterInfo::lowerCRBitRestore(), llvm::PPCRegisterInfo::lowerCRBitSpilling(), llvm::PPCRegisterInfo::lowerCRRestore(), llvm::PPCRegisterInfo::lowerCRSpilling(), llvm::PPCRegisterInfo::lowerDynamicAlloc(), llvm::XCoreMCInstLower::LowerOperand(), llvm::MipsMCInstLower::LowerOperand(), llvm::SystemZMCInstLower::lowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineInstrToMCInst(), lowerRIEfLow(), lowerRIHigh(), lowerRILow(), llvm::PPCRegisterInfo::lowerVRSAVERestore(), llvm::PPCRegisterInfo::lowerVRSAVESpilling(), MaySpeculate(), MIIsInTerminatorSequence(), llvm::MachineRegisterInfo::moveOperands(), llvm::SIInstrInfo::moveSMRDToVALU(), llvm::SIInstrInfo::moveToVALU(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::PPCInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeSelect(), llvm::HexagonInstrInfo::PredicateInstruction(), print(), llvm::MachineInstr::print(), llvm::SystemZAsmPrinter::PrintAsmMemoryOperand(), llvm::ARMAsmPrinter::PrintAsmMemoryOperand(), llvm::MipsAsmPrinter::PrintAsmMemoryOperand(), printAsmMRegister(), llvm::ARMAsmPrinter::PrintAsmOperand(), llvm::MipsAsmPrinter::PrintAsmOperand(), printIntelMemReference(), printLeaMemReference(), printMemReference(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printOperand(), llvm::ARMBaseInstrInfo::produceSameValue(), llvm::MachineInstr::readsWritesVirtualRegister(), registerADRCandidate(), llvm::ARMBaseInstrInfo::reMaterialize(), llvm::TargetInstrInfo::reMaterialize(), removeCopies(), removeIPMBasedCompare(), removeKillInfo(), llvm::MachineRegisterInfo::removeRegOperandFromUseList(), llvm::LiveVariables::removeVirtualRegisterDead(), llvm::LiveVariables::removeVirtualRegisterKilled(), llvm::LiveVariables::removeVirtualRegistersKilled(), llvm::LiveIntervals::repairIntervalsInRange(), llvm::PPCFrameLowering::replaceFPWithRealFP(), resultTests(), llvm::R600InstrInfo::ReverseBranchCondition(), llvm::rewriteAArch64FrameIndex(), llvm::Thumb1RegisterInfo::rewriteFrameIndex(), llvm::rewriteT2FrameIndex(), llvm::SelectionDAGISel::runOnMachineFunction(), llvm::Thumb1RegisterInfo::saveScavengerRegister(), llvm::RegScavenger::scavengeRegister(), llvm::R600SchedStrategy::schedNode(), llvm::FastISel::selectIntrinsicCall(), llvm::ARMBaseInstrInfo::setExecutionDomain(), llvm::MachineInstr::setPhysRegsDeadExcept(), setReg(), llvm::MachineBasicBlock::SplitCriticalEdge(), llvm::MachineInstr::substituteRegister(), llvm::ScheduleDAGInstrs::toggleKillFlag(), TrackDefUses(), trackRegDefsUses(), transferImpOps(), llvm::tryFoldSPUpdateIntoPushPop(), tryOrrMovk(), trySequenceOfOnes(), tryToreplicateChunks(), UpdateCPSRDef(), UpdateCPSRUse(), llvm::AntiDepBreaker::UpdateDbgValue(), UpdateOperandRegClass(), updatePhysDepsDownwards(), updatePhysDepsUpwards(), llvm::SIInstrInfo::verifyInstruction(), VerifyLowRegs(), and llvm::MachineRegisterInfo::verifyUseList().

| const uint32_t* llvm::MachineOperand::getRegLiveOut | ( | ) | const [inline] |

getRegLiveOut - Returns a bit mask of live-out registers.

Definition at line 490 of file MachineOperand.h.

References isRegLiveOut().

| const uint32_t* llvm::MachineOperand::getRegMask | ( | ) | const [inline] |

getRegMask - Returns a bit mask of registers preserved by this RegMask operand.

Definition at line 484 of file MachineOperand.h.

References isRegMask().

Referenced by clobbersPhysReg(), llvm::ScheduleDAGInstrs::fixupKills(), llvm::hash_value(), isIdenticalTo(), and trackRegDefsUses().

| unsigned llvm::MachineOperand::getSubReg | ( | ) | const [inline] |

Definition at line 269 of file MachineOperand.h.

References isReg().

Referenced by llvm::MachineInstr::addRegisterDefined(), canFoldCopy(), llvm::SIInstrInfo::commuteInstruction(), llvm::PPCInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), llvm::SystemZInstrInfo::convertToThreeAddress(), copyHint(), foldPatchpoint(), llvm::TargetInstrInfo::getExtractSubregInputs(), llvm::ARMBaseInstrInfo::getExtractSubregLikeInputs(), llvm::TargetInstrInfo::getInsertSubregInputs(), llvm::ARMBaseInstrInfo::getInsertSubregLikeInputs(), llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance(), llvm::MachineInstr::getRegClassConstraintEffect(), llvm::TargetInstrInfo::getRegSequenceInputs(), llvm::ARMBaseInstrInfo::getRegSequenceLikeInputs(), getSrcFromCopy(), llvm::hash_value(), INITIALIZE_PASS(), llvm::MachineInstr::isFullCopy(), isIdenticalTo(), llvm::MachineInstr::isIdentityCopy(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineInstrToMCInst(), llvm::PPCInstrInfo::optimizeCompareInstr(), print(), llvm::ARMAsmPrinter::printOperand(), readsReg(), llvm::MachineInstr::readsWritesVirtualRegister(), llvm::LiveIntervals::repairIntervalsInRange(), resultTests(), substPhysReg(), and substVirtReg().

| const char* llvm::MachineOperand::getSymbolName | ( | ) | const [inline] |

Definition at line 462 of file MachineOperand.h.

References isSymbol().

Referenced by llvm::ARMFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::SystemZMCInstLower::getExpr(), llvm::MSP430MCInstLower::GetExternalSymbolSymbol(), llvm::AArch64MCInstLower::GetExternalSymbolSymbol(), llvm::AArch64InstrInfo::GetInstSizeInBytes(), llvm::MSP430InstrInfo::GetInstSizeInBytes(), llvm::MipsInstrInfo::GetInstSizeInBytes(), llvm::ARMBaseInstrInfo::GetInstSizeInBytes(), llvm::SystemZInstrInfo::getInstSizeInBytes(), llvm::PPCInstrInfo::GetInstSizeInBytes(), GetSymbolFromOperand(), llvm::hash_value(), llvm::HexagonLowerToMC(), isIdenticalTo(), llvm::ARMAsmPrinter::lowerOperand(), LowerSymbolOperand(), and llvm::AArch64MCInstLower::lowerSymbolOperandELF().

| unsigned llvm::MachineOperand::getTargetFlags | ( | ) | const [inline] |

Definition at line 190 of file MachineOperand.h.

References isReg().

Referenced by llvm::MachineInstrBuilder::addDisp(), computeOthers(), llvm::ARMFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::ARMAsmPrinter::EmitInstruction(), llvm::X86AsmPrinter::EmitInstruction(), llvm::MSP430MCInstLower::GetBlockAddressSymbol(), llvm::MSP430MCInstLower::GetConstantPoolIndexSymbol(), llvm::MSP430MCInstLower::GetExternalSymbolSymbol(), llvm::MSP430MCInstLower::GetGlobalAddressSymbol(), llvm::MSP430MCInstLower::GetJumpTableSymbol(), GetSymbolFromOperand(), GetSymbolRef(), llvm::hash_value(), isCandidateLoad(), llvm::HexagonInstrInfo::isConstExtended(), isIdenticalTo(), llvm::SystemZMCInstLower::lowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), LowerSymbolOperand(), llvm::MSP430MCInstLower::LowerSymbolOperand(), llvm::AArch64MCInstLower::lowerSymbolOperandDarwin(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printSymbolOperand(), and registerADRCandidate().

| MachineOperandType llvm::MachineOperand::getType | ( | ) | const [inline] |

getType - Returns the MachineOperandType for this operand.

Definition at line 188 of file MachineOperand.h.

Referenced by llvm::MachineInstrBuilder::addDisp(), llvm::MachineInstr::addOperand(), canDefBePartOfLOH(), compareMachineOp(), llvm::SystemZMCInstLower::getExpr(), llvm::hash_value(), HashMachineInstr(), llvm::HexagonLowerToMC(), IsAnAddressOperand(), isIdenticalTo(), llvm::MSP430MCInstLower::Lower(), llvm::XCoreMCInstLower::LowerOperand(), llvm::MipsMCInstLower::LowerOperand(), llvm::SystemZMCInstLower::lowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::LowerPPCMachineInstrToMCInst(), LowerSymbolOperand(), print(), llvm::X86AsmPrinter::PrintAsmOperand(), llvm::MipsAsmPrinter::PrintAsmOperand(), llvm::AsmPrinter::PrintAsmOperand(), printLeaMemReference(), llvm::HexagonAsmPrinter::printOperand(), llvm::ARMAsmPrinter::printOperand(), llvm::MipsAsmPrinter::printOperand(), printOperand(), printPCRelImm(), and printSymbolOperand().

| bool llvm::MachineOperand::isBlockAddress | ( | ) | const [inline] |

isBlockAddress - Tests if this is a MO_BlockAddress operand.

Definition at line 249 of file MachineOperand.h.

References MO_BlockAddress.

Referenced by getBlockAddress(), getOffset(), and setOffset().

| bool llvm::MachineOperand::isCFIIndex | ( | ) | const [inline] |

Definition at line 257 of file MachineOperand.h.

References MO_CFIIndex.

Referenced by getCFIIndex().

| bool llvm::MachineOperand::isCImm | ( | ) | const [inline] |

isCImm - Test if this is a MO_CImmediate operand.

Definition at line 231 of file MachineOperand.h.

References MO_CImmediate.

Referenced by emitDebugValueComment(), getCImm(), and getDebugLocValue().

| bool llvm::MachineOperand::isCPI | ( | ) | const [inline] |

isCPI - Tests if this is a MO_ConstantPoolIndex operand.

Definition at line 239 of file MachineOperand.h.

References MO_ConstantPoolIndex.

Referenced by canFoldIntoMOVCC(), llvm::X86AsmPrinter::EmitInstruction(), getIndex(), getOffset(), llvm::isLeaMem(), setIndex(), and setOffset().

| bool llvm::MachineOperand::isDead | ( | ) | const [inline] |

Definition at line 289 of file MachineOperand.h.

References isReg().

Referenced by llvm::ScheduleDAGInstrs::addPhysRegDeps(), llvm::MachineInstr::addRegisterDead(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::MachineInstr::allDefsAreDead(), llvm::MachineOperandIteratorBase::analyzePhysReg(), canFoldIntoMOVCC(), ChangeToRegister(), RegisterOperands::collect(), llvm::PPCInstrInfo::commuteInstruction(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), CreateReg(), definesCPSR(), findHoistingInsertPosAndDeps(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::ARMBaseInstrInfo::FoldImmediate(), hasLiveCondCodeDef(), llvm::IsCPSRDead< MachineInstr >(), llvm::MachineInstr::isIdenticalTo(), llvm::HexagonInstrInfo::PredicateInstruction(), print(), tryOrrMovk(), trySequenceOfOnes(), tryToreplicateChunks(), and UpdateCPSRDef().

| bool llvm::MachineOperand::isDebug | ( | ) | const [inline] |

Definition at line 319 of file MachineOperand.h.

References isReg().

Referenced by ChangeToRegister(), CreateReg(), hasYmmReg(), llvm::HexagonInstrInfo::PredicateInstruction(), setIsDef(), and setIsKill().

| bool llvm::MachineOperand::isDef | ( | ) | const [inline] |

Definition at line 279 of file MachineOperand.h.

References isReg().

Referenced by addLiveInRegs(), llvm::ScheduleDAGInstrs::addPhysRegDataDeps(), llvm::ScheduleDAGInstrs::addPhysRegDeps(), llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterDefined(), llvm::MachineRegisterInfo::addRegOperandToUseList(), llvm::ScheduleDAGInstrs::addSchedBarrierDeps(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::MachineOperandIteratorBase::analyzePhysReg(), llvm::MachineOperandIteratorBase::analyzeVirtReg(), llvm::CriticalAntiDepBreaker::BreakAntiDependencies(), llvm::ScheduleDAGInstrs::buildSchedGraph(), canFoldIntoMOVCC(), ChangeToRegister(), clobbersCTR(), RegisterOperands::collect(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), CreateReg(), definesCPSR(), llvm::HexagonInstrInfo::DefinesPredicate(), llvm::ARMBaseInstrInfo::DefinesPredicate(), llvm::PPCInstrInfo::DefinesPredicate(), emitKill(), llvm::MachineInstr::eraseFromParentAndMarkDBGValuesForRemoval(), findDeadCallerSavedReg(), findDefIdx(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::ScheduleDAGInstrs::fixupKills(), llvm::RegScavenger::forward(), llvm::MachineInstrExpressionTrait::getHashValue(), llvm::PatchPointOpers::getNextScratchIdx(), GetPostIncrementOperand(), llvm::hash_value(), hasLiveCondCodeDef(), INITIALIZE_PASS(), isIdenticalTo(), llvm::MachineInstr::isIdenticalTo(), llvm::MachineInstr::isRegTiedToUseOperand(), IsSafeAndProfitableToMove(), llvm::Mips16InstrInfo::loadImmediate(), MaySpeculate(), MIIsInTerminatorSequence(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::PatchPointOpers::PatchPointOpers(), llvm::HexagonInstrInfo::PredicateInstruction(), print(), llvm::MachineInstr::print(), llvm::LiveVariables::removeVirtualRegisterDead(), llvm::LiveIntervals::repairIntervalsInRange(), resultTests(), llvm::MachineInstr::setPhysRegsDeadExcept(), llvm::MachineInstr::tieOperands(), trackRegDefsUses(), and UpdateCPSRUse().

| bool llvm::MachineOperand::isEarlyClobber | ( | ) | const [inline] |

Definition at line 309 of file MachineOperand.h.

References isReg().

Referenced by CreateReg(), dumpMachineInstrRangeWithSlotIndex(), llvm::LiveRangeCalc::extendToUses(), llvm::PatchPointOpers::getNextScratchIdx(), and print().

| bool llvm::MachineOperand::isFI | ( | ) | const [inline] |

isFI - Tests if this is a MO_FrameIndex operand.

Definition at line 237 of file MachineOperand.h.

References MO_FrameIndex.

Referenced by canFoldIntoMOVCC(), emitDebugValueComment(), llvm::TargetLoweringBase::emitPatchPoint(), getFrameIndexOperandNum(), getIndex(), isCSRestore(), llvm::PPCRegisterInfo::isFrameOffsetLegal(), llvm::ARMBaseRegisterInfo::isFrameOffsetLegal(), llvm::isLeaMem(), llvm::MipsSEInstrInfo::isLoadFromStackSlot(), llvm::XCoreInstrInfo::isLoadFromStackSlot(), llvm::HexagonInstrInfo::isLoadFromStackSlot(), llvm::SparcInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::PPCInstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), llvm::isMem(), llvm::SIInstrInfo::isOperandLegal(), isSimpleMove(), llvm::SystemZInstrInfo::isStackSlotCopy(), llvm::MipsSEInstrInfo::isStoreToStackSlot(), llvm::XCoreInstrInfo::isStoreToStackSlot(), llvm::HexagonInstrInfo::isStoreToStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::SparcInstrInfo::isStoreToStackSlot(), llvm::PPCInstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), MatchingStackOffset(), llvm::AArch64RegisterInfo::needsFrameBaseReg(), llvm::ARMBaseRegisterInfo::needsFrameBaseReg(), llvm::Thumb1RegisterInfo::resolveFrameIndex(), llvm::AArch64RegisterInfo::resolveFrameIndex(), llvm::PPCRegisterInfo::resolveFrameIndex(), llvm::ARMBaseRegisterInfo::resolveFrameIndex(), llvm::SelectionDAGISel::runOnMachineFunction(), setIndex(), UpdateOperandRegClass(), and llvm::SIInstrInfo::verifyInstruction().

| bool llvm::MachineOperand::isFPImm | ( | ) | const [inline] |

isFPImm - Tests if this is a MO_FPImmediate operand.

Definition at line 233 of file MachineOperand.h.

References MO_FPImmediate.

Referenced by llvm::DwarfUnit::addConstantFPValue(), llvm::SIInstrInfo::commuteInstruction(), emitDebugValueComment(), foldImmediates(), getDebugLocValue(), getFPImm(), llvm::SIInstrInfo::isImmOperandLegal(), llvm::SIInstrInfo::isInlineConstant(), llvm::SIInstrInfo::isLiteralConstant(), llvm::SIInstrInfo::isOperandLegal(), and llvm::SIInstrInfo::verifyInstruction().

| bool llvm::MachineOperand::isGlobal | ( | ) | const [inline] |

isGlobal - Tests if this is a MO_GlobalAddress operand.

Definition at line 245 of file MachineOperand.h.

References MO_GlobalAddress.

Referenced by llvm::X86FrameLowering::adjustForHiPEPrologue(), llvm::EHStreamer::callToNoUnwindFunction(), llvm::ARMFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), getGlobal(), getOffset(), GetSymbolFromOperand(), llvm::HexagonInstrInfo::isConstExtended(), llvm::isLeaMem(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), llvm::HexagonInstrInfo::PredicateInstruction(), and setOffset().

| bool MachineOperand::isIdenticalTo | ( | const MachineOperand & | Other | ) | const |

isIdenticalTo - Return true if this operand is identical to the specified operand. Note: This method ignores isKill and isDead properties.

isIdenticalTo - Return true if this operand is identical to the specified operand. Note that this should stay in sync with the hash_value overload below.

Definition at line 170 of file MachineInstr.cpp.

References getBlockAddress(), getCFIIndex(), getCImm(), getFPImm(), getGlobal(), getImm(), getIndex(), getMBB(), getMCSymbol(), getMetadata(), getOffset(), getReg(), getRegMask(), getSubReg(), getSymbolName(), getTargetFlags(), getType(), isDef(), llvm_unreachable, MO_BlockAddress, MO_CFIIndex, MO_CImmediate, MO_ConstantPoolIndex, MO_ExternalSymbol, MO_FPImmediate, MO_FrameIndex, MO_GlobalAddress, MO_Immediate, MO_JumpTableIndex, MO_MachineBasicBlock, MO_MCSymbol, MO_Metadata, MO_Register, MO_RegisterLiveOut, MO_RegisterMask, MO_TargetIndex, and llvm::LibFunc::strcmp.

Referenced by llvm::MachineInstr::isIdenticalTo(), and llvm::ARMBaseInstrInfo::produceSameValue().

| bool llvm::MachineOperand::isImm | ( | ) | const [inline] |

isImm - Tests if this is a MO_Immediate operand.

Definition at line 229 of file MachineOperand.h.

References MO_Immediate.

Referenced by llvm::DwarfUnit::addConstantValue(), llvm::SystemZInstrInfo::analyzeCompare(), llvm::R600InstrInfo::buildSlotOfVectorInstruction(), canFoldIntoCSel(), emitDebugValueComment(), llvm::PPCFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), llvm::HexagonFrameLowering::emitPrologue(), llvm::MachineInstr::findInlineAsmFlagIdx(), llvm::MachineInstr::findTiedOperandIdx(), llvm::PPCInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), foldImmediates(), llvm::AArch64InstrInfo::genAlternativeCodeSequence(), getDebugLocValue(), llvm::TargetInstrInfo::getExtractSubregInputs(), llvm::R600InstrInfo::getFlagOp(), getImm(), llvm::TargetInstrInfo::getInsertSubregInputs(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfs(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfsWidth(), llvm::TargetInstrInfo::getRegSequenceInputs(), llvm::AArch64InstrInfo::hasExtendedReg(), llvm::AArch64InstrInfo::hasShiftedReg(), llvm::HexagonInstrInfo::immediateExtend(), isCompareZero(), llvm::HexagonInstrInfo::isConstExtended(), llvm::AArch64InstrInfo::isGPRZero(), llvm::SIInstrInfo::isImmOperandLegal(), llvm::MachineInstr::isIndirectDebugValue(), llvm::SIInstrInfo::isInlineConstant(), llvm::isLeaMem(), llvm::SIInstrInfo::isLiteralConstant(), llvm::MipsSEInstrInfo::isLoadFromStackSlot(), llvm::XCoreInstrInfo::isLoadFromStackSlot(), llvm::HexagonInstrInfo::isLoadFromStackSlot(), llvm::SparcInstrInfo::isLoadFromStackSlot(), llvm::AArch64InstrInfo::isLoadFromStackSlot(), llvm::PPCInstrInfo::isLoadFromStackSlot(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), isMatchingUpdateInsn(), llvm::SIInstrInfo::isOperandLegal(), llvm::isParamLoad(), llvm::isScale(), llvm::MipsSEInstrInfo::isStoreToStackSlot(), llvm::XCoreInstrInfo::isStoreToStackSlot(), llvm::HexagonInstrInfo::isStoreToStackSlot(), llvm::AArch64InstrInfo::isStoreToStackSlot(), llvm::SparcInstrInfo::isStoreToStackSlot(), llvm::PPCInstrInfo::isStoreToStackSlot(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), llvm::SIInstrInfo::isTriviallyReMaterializable(), isZeroImm(), llvm::MipsInstrInfo::isZeroImm(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::moveSMRDToVALU(), llvm::SIInstrInfo::moveToVALU(), llvm::HexagonInstrInfo::PredicateInstruction(), llvm::TargetInstrInfo::PredicateInstruction(), llvm::MachineInstr::print(), llvm::HexagonAsmPrinter::PrintAsmMemoryOperand(), llvm::SystemZAsmPrinter::PrintAsmOperand(), llvm::HexagonAsmPrinter::PrintAsmOperand(), llvm::ARMAsmPrinter::PrintAsmOperand(), llvm::X86AsmPrinter::PrintAsmOperand(), llvm::MipsAsmPrinter::PrintAsmOperand(), printIntelMemReference(), llvm::MipsAsmPrinter::printUnsignedImm(), llvm::MipsAsmPrinter::printUnsignedImm8(), setImm(), llvm::R600InstrInfo::setImmOperand(), and llvm::SIInstrInfo::verifyInstruction().

| bool llvm::MachineOperand::isImplicit | ( | ) | const [inline] |

Definition at line 284 of file MachineOperand.h.

References isReg().

Referenced by llvm::MachineInstr::addOperand(), llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterKilled(), llvm::AggressiveAntiDepBreaker::BreakAntiDependencies(), llvm::TargetSchedModel::computeOperandLatency(), llvm::MachineInstr::copyImplicitOps(), EmitPCMPSTRI(), EmitPCMPSTRM(), llvm::PatchPointOpers::getNextScratchIdx(), llvm::MachineInstr::getNumExplicitOperands(), llvm::ARMBaseInstrInfo::getOperandLatency(), llvm::HexagonLowerToMC(), INITIALIZE_PASS(), llvm::SystemZMCInstLower::lower(), llvm::MSP430MCInstLower::Lower(), llvm::XCoreMCInstLower::LowerOperand(), llvm::MipsMCInstLower::LowerOperand(), llvm::AArch64MCInstLower::lowerOperand(), LowerOperand(), llvm::ARMAsmPrinter::lowerOperand(), llvm::PatchPointOpers::PatchPointOpers(), llvm::HexagonInstrInfo::PredicateInstruction(), print(), llvm::MachineInstr::print(), llvm::SIInstrInfo::verifyInstruction(), and VerifyLowRegs().

| bool llvm::MachineOperand::isInternalRead | ( | ) | const [inline] |

Definition at line 304 of file MachineOperand.h.

References isReg().

Referenced by CreateReg(), INITIALIZE_PASS(), print(), and readsReg().

| bool llvm::MachineOperand::isJTI | ( | ) | const [inline] |

isJTI - Tests if this is a MO_JumpTableIndex operand.

Definition at line 243 of file MachineOperand.h.

References MO_JumpTableIndex.

Referenced by canFoldIntoMOVCC(), getIndex(), GetSymbolRef(), llvm::isLeaMem(), llvm::MSP430MCInstLower::LowerSymbolOperand(), llvm::AArch64MCInstLower::lowerSymbolOperandDarwin(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), llvm::BranchFolder::OptimizeFunction(), and setIndex().

| bool llvm::MachineOperand::isKill | ( | ) | const [inline] |

Definition at line 294 of file MachineOperand.h.

References isReg().

Referenced by llvm::MachineInstr::addRegisterKilled(), llvm::MachineOperandIteratorBase::analyzePhysReg(), ChangeToRegister(), llvm::MachineInstr::clearRegisterKills(), llvm::PPCInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::SystemZInstrInfo::convertToThreeAddress(), CreateReg(), llvm::AArch64TargetLowering::EmitF128CSEL(), llvm::MachineInstr::findRegisterUseOperandIdx(), finishConvertToThreeAddress(), llvm::ScheduleDAGInstrs::fixupKills(), llvm::ARMBaseInstrInfo::FoldImmediate(), llvm::TargetInstrInfo::foldMemoryOperand(), genMadd(), genMaddR(), insertDivByZeroTrap(), InsertFPConstInst(), InsertFPImmInst(), InsertSPConstInst(), InsertSPImmInst(), llvm::MachineInstr::isIdenticalTo(), isOperandKill(), llvm::PPCRegisterInfo::lowerCRBitSpilling(), llvm::PPCRegisterInfo::lowerCRSpilling(), llvm::PPCRegisterInfo::lowerDynamicAlloc(), llvm::PPCRegisterInfo::lowerVRSAVESpilling(), llvm::HexagonInstrInfo::PredicateInstruction(), print(), removeKillInfo(), llvm::LiveVariables::removeVirtualRegisterKilled(), llvm::LiveVariables::removeVirtualRegistersKilled(), llvm::ScheduleDAGInstrs::toggleKillFlag(), and UpdateCPSRUse().

| bool llvm::MachineOperand::isMBB | ( | ) | const [inline] |

isMBB - Tests if this is a MO_MachineBasicBlock operand.

Definition at line 235 of file MachineOperand.h.

References MO_MachineBasicBlock.

Referenced by llvm::PPCInstrInfo::AnalyzeBranch(), llvm::SystemZInstrInfo::AnalyzeBranch(), getMBB(), getTargetMBB(), llvm::HexagonInstrInfo::immediateExtend(), llvm::HexagonInstrInfo::isConstExtended(), llvm::TargetInstrInfo::PredicateInstruction(), llvm::SystemZInstrInfo::RemoveBranch(), and setMBB().

| bool llvm::MachineOperand::isMCSymbol | ( | ) | const [inline] |

Definition at line 256 of file MachineOperand.h.

References MO_MCSymbol.

Referenced by getMCSymbol().

| bool llvm::MachineOperand::isMetadata | ( | ) | const [inline] |

isMetadata - Tests if this is a MO_Metadata operand.

Definition at line 255 of file MachineOperand.h.

References MO_Metadata.

Referenced by llvm::MachineInstr::emitError(), EmitGCCInlineAsmStr(), EmitMSInlineAsmStr(), getMetadata(), and llvm::MachineInstr::print().

| bool llvm::MachineOperand::isReg | ( | ) | const [inline] |

isReg - Tests if this is a MO_Register operand.

Definition at line 227 of file MachineOperand.h.

References MO_Register.

Referenced by addLiveInRegs(), llvm::MachineInstr::addOperand(), llvm::MachineInstr::addRegisterDead(), llvm::MachineInstr::addRegisterDefined(), llvm::MachineInstr::addRegisterKilled(), llvm::ScheduleDAGInstrs::addSchedBarrierDeps(), addTargetFlag(), llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::MachineInstr::allDefsAreDead(), llvm::SystemZInstrInfo::analyzeCompare(), llvm::MachineOperandIteratorBase::analyzePhysReg(), llvm::MachineOperandIteratorBase::analyzeVirtReg(), llvm::CriticalAntiDepBreaker::BreakAntiDependencies(), llvm::ScheduleDAGInstrs::buildSchedGraph(), canCombineWithMUL(), canFoldIntoMOVCC(), ChangeToImmediate(), ChangeToRegister(), llvm::MachineInstr::clearKillInfo(), llvm::MachineInstr::clearRegisterKills(), clobbersCTR(), RegisterOperands::collect(), collectDebugValues(), llvm::SIInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::MachineInstr::copyImplicitOps(), definesCPSR(), llvm::HexagonInstrInfo::DefinesPredicate(), llvm::ARMBaseInstrInfo::DefinesPredicate(), llvm::PPCInstrInfo::DefinesPredicate(), earlyUseOperand(), emitDebugValueComment(), llvm::X86FrameLowering::emitEpilogue(), llvm::X86AsmPrinter::EmitInstruction(), llvm::SITargetLowering::EmitInstrWithCustomInserter(), emitKill(), EmitPCMPSTRI(), EmitPCMPSTRM(), llvm::MachineInstr::eraseFromParentAndMarkDBGValuesForRemoval(), eraseGPOpnd(), llvm::TargetInstrInfo::findCommutedOpIndices(), findDeadCallerSavedReg(), findDefIdx(), findHoistingInsertPosAndDeps(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::MachineInstr::findRegisterUseOperandIdx(), llvm::MachineInstr::findTiedOperandIdx(), findUseIdx(), finishConvertToThreeAddress(), llvm::ScheduleDAGInstrs::fixupKills(), llvm::PPCInstrInfo::FoldImmediate(), foldImmediates(), forceReg(), llvm::RegScavenger::forward(), FuseInst(), getCallTargetRegOpnd(), getDebugLocValue(), getFPReg(), llvm::MachineInstrExpressionTrait::getHashValue(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfs(), llvm::AArch64InstrInfo::getLdStBaseRegImmOfsWidth(), llvm::PatchPointOpers::getNextScratchIdx(), llvm::MachineInstr::getNumExplicitOperands(), GetPostIncrementOperand(), getPredicatedRegister(), getReg(), llvm::MachineInstr::getRegClassConstraint(), llvm::MachineInstr::getRegClassConstraintEffect(), getSubReg(), getTargetFlags(), llvm::SIInstrInfo::getVALUOp(), HandleVRSaveUpdate(), hasLiveCondCodeDef(), llvm::AArch64InstrInfo::hasPattern(), hasVGPROperands(), hasYmmReg(), INITIALIZE_PASS(), llvm::IsCPSRDead< MachineInstr >(), isDead(), isDebug(), isDef(), llvm::isDescribedByReg(), isEarlyClobber(), llvm::AArch64InstrInfo::isFPRCopy(), llvm::MachineInstr::isIdenticalTo(), isImplicit(), llvm::MachineInstr::isIndirectDebugValue(), isInternalRead(), isKill(), llvm::isLeaMem(), llvm::ARMBaseInstrInfo::isLoadFromStackSlot(), llvm::isMem(), isMemoryOp(), llvm::NVPTXInstrInfo::isMoveInstr(), llvm::SIInstrInfo::isOperandLegal(), llvm::MachineInstr::isRegTiedToDefOperand(), llvm::MachineInstr::isRegTiedToUseOperand(), IsSafeAndProfitableToMove(), llvm::ARMBaseInstrInfo::isStoreToStackSlot(), isTied(), isTwoAddrUse(), isUndef(), isUse(), isVGPR(), llvm::final< T >::isX86_64ExtendedReg(), llvm::SIInstrInfo::legalizeOperands(), llvm::SIInstrInfo::legalizeOpWithMove(), llvm::Mips16InstrInfo::loadImmediate(), llvm::SystemZMCInstLower::lower(), MaySpeculate(), MIIsInTerminatorSequence(), llvm::MachineRegisterInfo::moveOperands(), llvm::SIInstrInfo::moveSMRDToVALU(), llvm::SIInstrInfo::moveToVALU(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::HexagonInstrInfo::PredicateInstruction(), llvm::TargetInstrInfo::PredicateInstruction(), llvm::MachineInstr::print(), llvm::HexagonAsmPrinter::PrintAsmMemoryOperand(), llvm::ARMAsmPrinter::PrintAsmMemoryOperand(), llvm::MipsAsmPrinter::PrintAsmMemoryOperand(), llvm::HexagonAsmPrinter::PrintAsmOperand(), llvm::ARMAsmPrinter::PrintAsmOperand(), llvm::X86AsmPrinter::PrintAsmOperand(), llvm::MipsAsmPrinter::PrintAsmOperand(), readsReg(), llvm::MachineInstr::readsWritesVirtualRegister(), removeKillInfo(), llvm::MachineInstr::RemoveOperand(), llvm::LiveVariables::removeVirtualRegisterDead(), llvm::LiveVariables::removeVirtualRegisterKilled(), llvm::LiveVariables::removeVirtualRegistersKilled(), llvm::LiveIntervals::repairIntervalsInRange(), llvm::PPCFrameLowering::replaceFPWithRealFP(), resultTests(), llvm::Thumb1RegisterInfo::saveScavengerRegister(), llvm::RegScavenger::scavengeRegister(), llvm::R600SchedStrategy::schedNode(), llvm::FastISel::selectIntrinsicCall(), setImplicit(), setIsDead(), setIsDebug(), setIsDef(), setIsEarlyClobber(), setIsInternalRead(), setIsKill(), setIsUndef(), llvm::MachineInstr::setPhysRegsDeadExcept(), setSubReg(), setTargetFlags(), llvm::MachineInstr::substituteRegister(), TrackDefUses(), trackRegDefsUses(), transferImpOps(), UpdateCPSRDef(), UpdateCPSRUse(), llvm::AntiDepBreaker::UpdateDbgValue(), UpdateOperandRegClass(), llvm::SIInstrInfo::verifyInstruction(), VerifyLowRegs(), and llvm::MachineRegisterInfo::verifyUseList().

| bool llvm::MachineOperand::isRegLiveOut | ( | ) | const [inline] |

isRegLiveOut - Tests if this is a MO_RegisterLiveOut operand.

Definition at line 253 of file MachineOperand.h.

References MO_RegisterLiveOut.

Referenced by getRegLiveOut().

| bool llvm::MachineOperand::isRegMask | ( | ) | const [inline] |

isRegMask - Tests if this is a MO_RegisterMask operand.

Definition at line 251 of file MachineOperand.h.

References MO_RegisterMask.

Referenced by llvm::MachineInstr::addOperand(), llvm::MachineOperandIteratorBase::analyzePhysReg(), callClobbersAnyYmmReg(), clobbersCTR(), llvm::MachineInstr::copyImplicitOps(), llvm::ARMBaseInstrInfo::DefinesPredicate(), llvm::PPCInstrInfo::DefinesPredicate(), findHoistingInsertPosAndDeps(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::ScheduleDAGInstrs::fixupKills(), getRegMask(), hasYmmReg(), llvm::AArch64InstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::Thumb1RegisterInfo::saveScavengerRegister(), llvm::MachineInstr::setPhysRegsDeadExcept(), and trackRegDefsUses().

| bool llvm::MachineOperand::isSymbol | ( | ) | const [inline] |

isSymbol - Tests if this is a MO_ExternalSymbol operand.

Definition at line 247 of file MachineOperand.h.

References MO_ExternalSymbol.

Referenced by llvm::ARMFrameLowering::emitEpilogue(), llvm::X86FrameLowering::emitEpilogue(), getOffset(), GetSymbolFromOperand(), getSymbolName(), llvm::HexagonInstrInfo::isConstExtended(), llvm::AArch64MCInstLower::lowerSymbolOperandELF(), and setOffset().

| bool llvm::MachineOperand::isTargetIndex | ( | ) | const [inline] |

isTargetIndex - Tests if this is a MO_TargetIndex operand.

Definition at line 241 of file MachineOperand.h.

References MO_TargetIndex.

Referenced by getIndex(), getOffset(), llvm::SIInstrInfo::isOperandLegal(), setIndex(), and setOffset().

| bool llvm::MachineOperand::isTied | ( | ) | const [inline] |

Definition at line 314 of file MachineOperand.h.

References isReg().

Referenced by llvm::MachineInstr::addOperand(), canFoldIntoMOVCC(), ChangeToImmediate(), llvm::MachineInstr::findTiedOperandIdx(), llvm::MachineInstr::isRegTiedToDefOperand(), llvm::MachineInstr::isRegTiedToUseOperand(), print(), llvm::MachineInstr::RemoveOperand(), and llvm::MachineInstr::tieOperands().

| bool llvm::MachineOperand::isUndef | ( | ) | const [inline] |

Definition at line 299 of file MachineOperand.h.

References isReg().

Referenced by llvm::MachineInstr::addRegisterKilled(), ChangeToRegister(), CreateReg(), llvm::ScheduleDAGInstrs::fixupKills(), llvm::RegScavenger::forward(), llvm::IsCPSRDead< MachineInstr >(), isLocalCopy(), isMemoryOp(), llvm::HexagonInstrInfo::PredicateInstruction(), print(), readsReg(), llvm::MachineInstr::readsWritesVirtualRegister(), llvm::LiveIntervals::repairIntervalsInRange(), llvm::Thumb1RegisterInfo::saveScavengerRegister(), llvm::RegScavenger::scavengeRegister(), llvm::MachineBasicBlock::SplitCriticalEdge(), UpdateCPSRDef(), and UpdateCPSRUse().

| bool llvm::MachineOperand::isUse | ( | ) | const [inline] |

Definition at line 274 of file MachineOperand.h.

References isReg().

Referenced by llvm::MachineInstr::addOperand(), llvm::ScheduleDAGInstrs::addPhysRegDeps(), llvm::MachineInstr::addRegisterKilled(), llvm::MachineInstr::allDefsAreDead(), llvm::CriticalAntiDepBreaker::BreakAntiDependencies(), llvm::MachineInstr::clearKillInfo(), llvm::MachineInstr::clearRegisterKills(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), findHoistingInsertPosAndDeps(), llvm::MachineInstr::findRegisterUseOperandIdx(), llvm::MachineInstr::findTiedOperandIdx(), llvm::ScheduleDAGInstrs::fixupKills(), llvm::RegScavenger::forward(), getCallTargetRegOpnd(), GetPostIncrementOperand(), getPredicatedRegister(), llvm::MachineInstr::getRegClassConstraint(), INITIALIZE_PASS(), llvm::IsCPSRDead< MachineInstr >(), llvm::MachineInstr::isRegTiedToDefOperand(), isTwoAddrUse(), llvm::HexagonInstrInfo::PredicateInstruction(), print(), readsReg(), llvm::MachineInstr::readsWritesVirtualRegister(), llvm::LiveIntervals::repairIntervalsInRange(), llvm::RegScavenger::scavengeRegister(), llvm::MachineInstr::tieOperands(), TrackDefUses(), trackRegDefsUses(), transferImpOps(), UpdateCPSRDef(), and llvm::SIInstrInfo::verifyInstruction().

| void MachineOperand::print | ( | raw_ostream & | OS, |

| const TargetMachine * | TM = nullptr |

||

| ) | const |

print - Print the specified machine operand.

Definition at line 261 of file MachineInstr.cpp.

References llvm::MachineBasicBlock::getParent(), getParent(), getReg(), llvm::TargetSubtargetInfo::getRegisterInfo(), getSubReg(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetMachine::getTarget(), getType(), isDead(), isDef(), isEarlyClobber(), isImplicit(), isInternalRead(), isKill(), isTied(), isUndef(), isUse(), MBB, llvm::AArch64CC::MI, and MO_Register.

Referenced by llvm::operator<<(), and llvm::MachineInstr::print().

| bool llvm::MachineOperand::readsReg | ( | ) | const [inline] |

readsReg - Returns true if this operand reads the previous value of its register. A use operand with the <undef> flag set doesn't read its register. A sub-register def implicitly reads the other parts of the register being redefined unless the <undef> flag is set.

This refers to reading the register value from before the current instruction or bundle. Internal bundle reads are not included.

Definition at line 331 of file MachineOperand.h.

References getSubReg(), isInternalRead(), isReg(), isUndef(), and isUse().

Referenced by llvm::ScheduleDAGInstrs::addSchedBarrierDeps(), llvm::MachineOperandIteratorBase::analyzePhysReg(), llvm::MachineOperandIteratorBase::analyzeVirtReg(), llvm::ScheduleDAGInstrs::buildSchedGraph(), RegisterOperands::collect(), llvm::ConnectedVNInfoEqClasses::Distribute(), findUseIdx(), and llvm::ARMBaseInstrInfo::getPartialRegUpdateClearance().

| void llvm::MachineOperand::setImm | ( | int64_t | immVal | ) | [inline] |

Definition at line 504 of file MachineOperand.h.

References isImm().

Referenced by llvm::R600InstrInfo::addFlag(), llvm::R600InstrInfo::buildSlotOfVectorInstruction(), llvm::R600InstrInfo::clearFlag(), llvm::PPCInstrInfo::commuteInstruction(), CreateImm(), llvm::ARMBaseInstrInfo::duplicate(), llvm::HexagonFrameLowering::emitPrologue(), llvm::R600InstrInfo::InsertBranch(), invertBccCondition(), llvm::ARMBaseInstrInfo::PredicateInstruction(), llvm::R600InstrInfo::PredicateInstruction(), llvm::TargetInstrInfo::PredicateInstruction(), llvm::R600InstrInfo::ReverseBranchCondition(), and llvm::R600InstrInfo::setImmOperand().

| void llvm::MachineOperand::setImplicit | ( | bool | Val = true | ) | [inline] |

Definition at line 367 of file MachineOperand.h.

Referenced by llvm::ARMBaseInstrInfo::optimizeSelect().

| void llvm::MachineOperand::setIndex | ( | int | Idx | ) | [inline] |

Definition at line 516 of file MachineOperand.h.

References isCPI(), isFI(), isJTI(), and isTargetIndex().

Referenced by CreateCPI(), CreateFI(), CreateJTI(), CreateTargetIndex(), and llvm::ARMBaseInstrInfo::duplicate().

| void llvm::MachineOperand::setIsDead | ( | bool | Val = true | ) | [inline] |

Definition at line 378 of file MachineOperand.h.

Referenced by llvm::MachineInstr::addRegisterDead(), llvm::ARMBaseInstrInfo::convertToThreeAddress(), llvm::MSP430FrameLowering::eliminateCallFramePseudoInstr(), llvm::X86FrameLowering::eliminateCallFramePseudoInstr(), llvm::MSP430FrameLowering::emitEpilogue(), emitIncrement(), llvm::MSP430FrameLowering::emitPrologue(), llvm::X86FrameLowering::emitPrologue(), emitSPUpdate(), llvm::LiveVariables::removeVirtualRegisterDead(), and llvm::MachineInstr::setPhysRegsDeadExcept().

| void llvm::MachineOperand::setIsDebug | ( | bool | Val = true | ) | [inline] |

Definition at line 398 of file MachineOperand.h.

Referenced by llvm::FastISel::selectIntrinsicCall().

| void MachineOperand::setIsDef | ( | bool | Val = true | ) |

Change a def to a use, or a use to a def.

Definition at line 91 of file MachineInstr.cpp.

References llvm::MachineRegisterInfo::addRegOperandToUseList(), llvm::MachineBasicBlock::getParent(), getParent(), isDebug(), isReg(), MBB, llvm::AArch64CC::MI, llvm::MachineRegisterInfo::removeRegOperandFromUseList(), and Val.

Referenced by llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), and setIsUse().

| void llvm::MachineOperand::setIsEarlyClobber | ( | bool | Val = true | ) | [inline] |

Definition at line 393 of file MachineOperand.h.

Referenced by llvm::MachineInstr::addOperand().

| void llvm::MachineOperand::setIsInternalRead | ( | bool | Val = true | ) | [inline] |

Definition at line 388 of file MachineOperand.h.

Referenced by INITIALIZE_PASS().

| void llvm::MachineOperand::setIsKill | ( | bool | Val = true | ) | [inline] |

Definition at line 372 of file MachineOperand.h.

References isDebug(), isReg(), and Val.

Referenced by llvm::ScheduleDAGInstrs::addPhysRegDeps(), llvm::MachineInstr::addRegisterKilled(), llvm::MachineInstr::clearKillInfo(), llvm::MachineInstr::clearRegisterKills(), llvm::PPCInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), llvm::R600InstrInfo::copyPhysReg(), earlyUseOperand(), llvm::ARMBaseInstrInfo::FoldImmediate(), insertDivByZeroTrap(), removeKillInfo(), llvm::LiveVariables::removeVirtualRegisterKilled(), llvm::LiveVariables::removeVirtualRegistersKilled(), and llvm::ScheduleDAGInstrs::toggleKillFlag().

| void llvm::MachineOperand::setIsUndef | ( | bool | Val = true | ) | [inline] |

Definition at line 383 of file MachineOperand.h.

| void llvm::MachineOperand::setIsUse | ( | bool | Val = true | ) | [inline] |

Definition at line 363 of file MachineOperand.h.

References setIsDef(), and Val.

| void llvm::MachineOperand::setMBB | ( | MachineBasicBlock * | MBB | ) | [inline] |

Definition at line 522 of file MachineOperand.h.

Referenced by CreateMBB(), llvm::TargetInstrInfo::PredicateInstruction(), and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

| void llvm::MachineOperand::setOffset | ( | int64_t | Offset | ) | [inline] |

Definition at line 509 of file MachineOperand.h.

References isBlockAddress(), isCPI(), isGlobal(), isSymbol(), and isTargetIndex().

Referenced by CreateBA(), CreateCPI(), CreateES(), CreateGA(), and CreateTargetIndex().

| void MachineOperand::setReg | ( | unsigned | Reg | ) |

Change the register this operand corresponds to.

Definition at line 49 of file MachineInstr.cpp.

References llvm::MachineRegisterInfo::addRegOperandToUseList(), llvm::MachineBasicBlock::getParent(), getParent(), getReg(), MBB, llvm::AArch64CC::MI, Reg, and llvm::MachineRegisterInfo::removeRegOperandFromUseList().

Referenced by llvm::ARMTargetLowering::AdjustInstrPostInstrSelection(), llvm::AggressiveAntiDepBreaker::BreakAntiDependencies(), llvm::R600InstrInfo::buildSlotOfVectorInstruction(), llvm::PPCInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), llvm::ConnectedVNInfoEqClasses::Distribute(), llvm::SparcRegisterInfo::eliminateFrameIndex(), llvm::PPCInstrInfo::FoldImmediate(), llvm::ARMBaseInstrInfo::FoldImmediate(), INITIALIZE_PASS(), llvm::SIInstrInfo::legalizeOperands(), llvm::MachineRegisterInfo::markUsesInDebugValueAsUndef(), llvm::SIInstrInfo::moveSMRDToVALU(), llvm::ARMBaseInstrInfo::optimizeCompareInstr(), llvm::ARMBaseInstrInfo::PredicateInstruction(), llvm::R600InstrInfo::PredicateInstruction(), llvm::TargetInstrInfo::PredicateInstruction(), llvm::PPCFrameLowering::replaceFPWithRealFP(), llvm::MachineRegisterInfo::replaceRegWith(), llvm::R600InstrInfo::ReverseBranchCondition(), llvm::MachineSSAUpdater::RewriteUse(), substPhysReg(), substVirtReg(), and llvm::AntiDepBreaker::UpdateDbgValue().

| void llvm::MachineOperand::setSubReg | ( | unsigned | subReg | ) | [inline] |

Definition at line 344 of file MachineOperand.h.

References isReg().

Referenced by llvm::SIInstrInfo::commuteInstruction(), llvm::PPCInstrInfo::commuteInstruction(), llvm::TargetInstrInfo::commuteInstruction(), CreateReg(), insertDivByZeroTrap(), substPhysReg(), and substVirtReg().

| void llvm::MachineOperand::setTargetFlags | ( | unsigned | F | ) | [inline] |