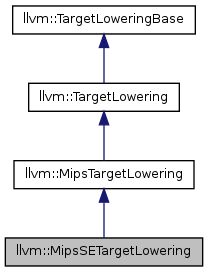

#include <MipsSEISelLowering.h>

Public Member Functions | |

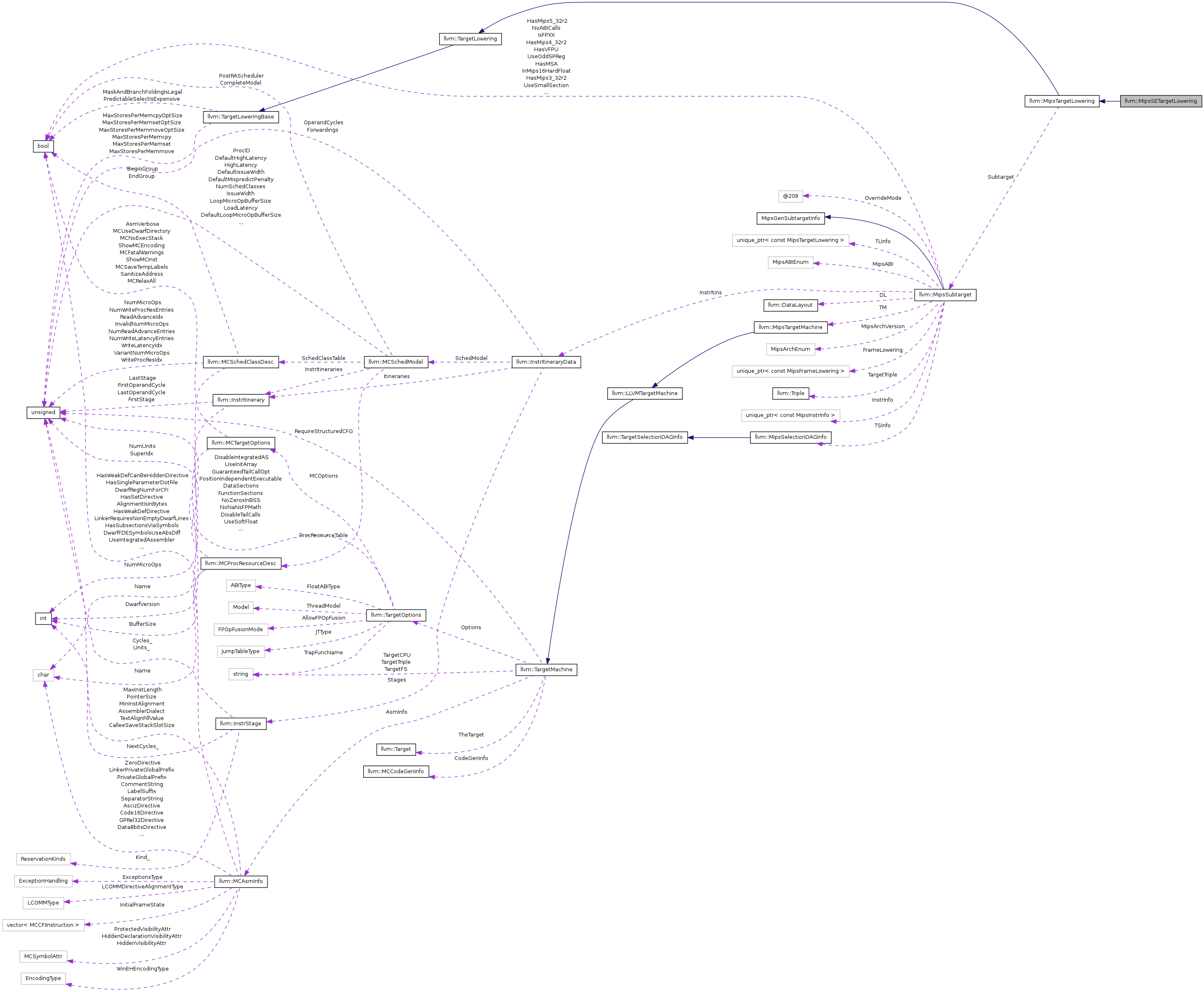

| MipsSETargetLowering (MipsTargetMachine &TM, const MipsSubtarget &STI) | |

| void | addMSAIntType (MVT::SimpleValueType Ty, const TargetRegisterClass *RC) |

| Enable MSA support for the given integer type and Register class. | |

| void | addMSAFloatType (MVT::SimpleValueType Ty, const TargetRegisterClass *RC) |

| Enable MSA support for the given floating-point type and Register class. | |

| bool | allowsMisalignedMemoryAccesses (EVT VT, unsigned AS=0, unsigned Align=1, bool *Fast=nullptr) const override |

| Determine if the target supports unaligned memory accesses. | |

| SDValue | LowerOperation (SDValue Op, SelectionDAG &DAG) const override |

| LowerOperation - Provide custom lowering hooks for some operations. | |

| SDValue | PerformDAGCombine (SDNode *N, DAGCombinerInfo &DCI) const override |

| MachineBasicBlock * | EmitInstrWithCustomInserter (MachineInstr *MI, MachineBasicBlock *MBB) const override |

| bool | isShuffleMaskLegal (const SmallVectorImpl< int > &Mask, EVT VT) const override |

| const TargetRegisterClass * | getRepRegClassFor (MVT VT) const override |

Detailed Description

Definition at line 21 of file MipsSEISelLowering.h.

Constructor & Destructor Documentation

| MipsSETargetLowering::MipsSETargetLowering | ( | MipsTargetMachine & | TM, |

| const MipsSubtarget & | STI | ||

| ) | [explicit] |

Definition at line 38 of file MipsSEISelLowering.cpp.

References llvm::MipsSubtarget::abiUsesSoftFloat(), llvm::ISD::ADD, llvm::ISD::ADDE, addMSAFloatType(), addMSAIntType(), llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::AND, llvm::array_lengthof(), llvm::ISD::ATOMIC_FENCE, llvm::ISD::BITCAST, llvm::ISD::BRCOND, llvm::ISD::BUILTIN_OP_END, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::TargetLoweringBase::Custom, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::MVT::f32, llvm::MVT::f64, llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::MipsSubtarget::hasCnMips(), llvm::MipsSubtarget::hasDSP(), llvm::MipsSubtarget::hasDSPR2(), llvm::MipsSubtarget::hasMips32r6(), llvm::MipsSubtarget::hasMips64r6(), llvm::MipsSubtarget::hasMSA(), llvm::MVT::i32, llvm::MVT::i64, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::MipsSubtarget::isFP64bit(), llvm::MipsSubtarget::isGP64bit(), llvm::MipsSubtarget::isSingleFloat(), llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::TargetLoweringBase::Legal, llvm::ISD::LOAD, llvm::ISD::MUL, llvm::ISD::MULHS, llvm::ISD::MULHU, NoDPLoadStore, llvm::ISD::OR, llvm::MVT::Other, llvm::ISD::SDIV, llvm::ISD::SDIVREM, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::ISD::SETCC, llvm::TargetLoweringBase::setCondCodeAction(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setTargetDAGCombine(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SEXTLOAD, llvm::ISD::SHL, llvm::ISD::SMUL_LOHI, llvm::ISD::SRA, llvm::ISD::SREM, llvm::ISD::SRL, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ISD::SUBE, llvm::MipsTargetLowering::Subtarget, llvm::ISD::UDIV, llvm::ISD::UDIVREM, llvm::ISD::UMUL_LOHI, llvm::ISD::UREM, llvm::MVT::v16i8, llvm::MVT::v2f64, llvm::MVT::v2i16, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v4i8, llvm::MVT::v8f16, llvm::MVT::v8i16, llvm::ISD::VSELECT, llvm::ISD::XOR, and llvm::ISD::ZEXTLOAD.

Member Function Documentation

| void MipsSETargetLowering::addMSAFloatType | ( | MVT::SimpleValueType | Ty, |

| const TargetRegisterClass * | RC | ||

| ) |

Enable MSA support for the given floating-point type and Register class.

Definition at line 295 of file MipsSEISelLowering.cpp.

References llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, llvm::ISD::BUILTIN_OP_END, llvm::TargetLoweringBase::Custom, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FDIV, llvm::ISD::FEXP2, llvm::ISD::FLOG2, llvm::ISD::FMA, llvm::ISD::FMUL, llvm::ISD::FRINT, llvm::ISD::FSQRT, llvm::ISD::FSUB, llvm::ISD::INSERT_VECTOR_ELT, llvm::TargetLoweringBase::Legal, llvm::ISD::LOAD, llvm::ISD::SETCC, llvm::TargetLoweringBase::setCondCodeAction(), llvm::ISD::SETGE, llvm::ISD::SETGT, llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::TargetLoweringBase::setOperationAction(), llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::STORE, llvm::MVT::v8f16, and llvm::ISD::VSELECT.

Referenced by MipsSETargetLowering().

| void MipsSETargetLowering::addMSAIntType | ( | MVT::SimpleValueType | Ty, |

| const TargetRegisterClass * | RC | ||

| ) |

Enable MSA support for the given integer type and Register class.

Definition at line 246 of file MipsSEISelLowering.cpp.

References llvm::ISD::ADD, llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::AND, llvm::ISD::BITCAST, llvm::ISD::BUILD_VECTOR, llvm::ISD::BUILTIN_OP_END, llvm::ISD::CTLZ, llvm::ISD::CTPOP, llvm::TargetLoweringBase::Custom, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::INSERT_VECTOR_ELT, llvm::TargetLoweringBase::Legal, llvm::ISD::LOAD, llvm::ISD::MUL, llvm::ISD::OR, llvm::ISD::SDIV, llvm::ISD::SETCC, llvm::TargetLoweringBase::setCondCodeAction(), llvm::ISD::SETGE, llvm::ISD::SETGT, llvm::ISD::SETNE, llvm::TargetLoweringBase::setOperationAction(), llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SHL, llvm::ISD::SINT_TO_FP, llvm::ISD::SRA, llvm::ISD::SREM, llvm::ISD::SRL, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ISD::UDIV, llvm::ISD::UINT_TO_FP, llvm::ISD::UREM, llvm::MVT::v2i64, llvm::MVT::v4i32, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::VSELECT, and llvm::ISD::XOR.

Referenced by MipsSETargetLowering().

| bool MipsSETargetLowering::allowsMisalignedMemoryAccesses | ( | EVT | , |

| unsigned | AddrSpace = 0, |

||

| unsigned | Align = 1, |

||

| bool * | = nullptr |

||

| ) | const [override, virtual] |

Determine if the target supports unaligned memory accesses.

This function returns true if the target allows unaligned memory accesses of the specified type in the given address space. If true, it also returns whether the unaligned memory access is "fast" in the last argument by reference. This is used, for example, in situations where an array copy/move/set is converted to a sequence of store operations. Its use helps to ensure that such replacements don't generate code that causes an alignment error (trap) on the target machine.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 333 of file MipsSEISelLowering.cpp.

References llvm::EVT::getSimpleVT(), llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::SimpleTy, llvm::MipsTargetLowering::Subtarget, and llvm::MipsSubtarget::systemSupportsUnalignedAccess().

| MachineBasicBlock * MipsSETargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::MipsTargetLowering.

Definition at line 1112 of file MipsSEISelLowering.cpp.

References llvm::MachineInstr::getOpcode().

| const TargetRegisterClass * MipsSETargetLowering::getRepRegClassFor | ( | MVT | VT | ) | const [override, virtual] |

Return the 'representative' register class for the specified value type.

The 'representative' register class is the largest legal super-reg register class for the register class of the value type. For example, on i386 the rep register class for i8, i16, and i32 are GR32; while the rep register class is GR64 on x86_64.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 237 of file MipsSEISelLowering.cpp.

References llvm::MipsSubtarget::hasDSP(), llvm::MipsTargetLowering::Subtarget, and llvm::MVT::Untyped.

| bool llvm::MipsSETargetLowering::isShuffleMaskLegal | ( | const SmallVectorImpl< int > & | , |

| EVT | |||

| ) | const [inline, override, virtual] |

Targets can use this to indicate that they only support *some* VECTOR_SHUFFLE operations, those with specific masks. By default, if a target supports the VECTOR_SHUFFLE node, all mask values are assumed to be legal.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 46 of file MipsSEISelLowering.h.

| SDValue MipsSETargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerOperation - Provide custom lowering hooks for some operations.

Reimplemented from llvm::MipsTargetLowering.

Definition at line 360 of file MipsSEISelLowering.cpp.

References llvm::ISD::BUILD_VECTOR, llvm::MipsISD::DivRem, llvm::MipsISD::DivRemU, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::SDValue::getOpcode(), llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::ISD::LOAD, llvm::ISD::MUL, llvm::ISD::MULHS, llvm::ISD::MULHU, llvm::MipsISD::Mult, llvm::MipsISD::Multu, llvm::ISD::SDIVREM, llvm::ISD::SMUL_LOHI, llvm::ISD::STORE, llvm::ISD::UDIVREM, llvm::ISD::UMUL_LOHI, and llvm::ISD::VECTOR_SHUFFLE.

| SDValue MipsSETargetLowering::PerformDAGCombine | ( | SDNode * | N, |

| DAGCombinerInfo & | DCI | ||

| ) | const [override, virtual] |

This method will be invoked for all target nodes and for any target-independent nodes that the target has registered with invoke it for.

The semantics are as follows: Return Value: SDValue.Val == 0 - No change was made SDValue.Val == N - N was replaced, is dead, and is already handled. otherwise - N should be replaced by the returned Operand.

In addition, methods provided by DAGCombinerInfo may be used to perform more complex transformations.

Reimplemented from llvm::MipsTargetLowering.

Definition at line 1066 of file MipsSEISelLowering.cpp.

References llvm::ISD::ADDE, llvm::ISD::AND, llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::dbgs(), DEBUG, llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm::ISD::MUL, llvm::ISD::OR, performADDECombine(), performANDCombine(), performMULCombine(), performORCombine(), performSETCCCombine(), performSHLCombine(), performSRACombine(), performSRLCombine(), performSUBECombine(), performVSELECTCombine(), performXORCombine(), llvm::SDNode::printrWithDepth(), llvm::ISD::SETCC, llvm::ISD::SHL, llvm::ISD::SRA, llvm::ISD::SRL, llvm::ISD::SUBE, llvm::MipsTargetLowering::Subtarget, llvm::ISD::VSELECT, and llvm::ISD::XOR.

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1