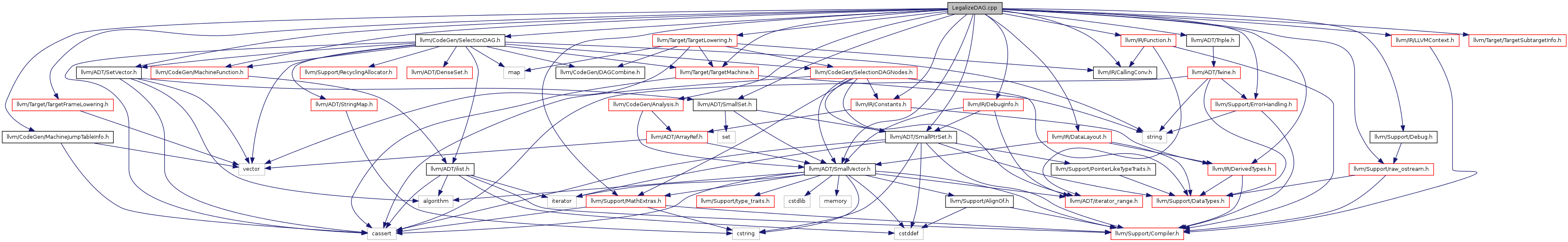

#include "llvm/CodeGen/SelectionDAG.h"#include "llvm/ADT/SetVector.h"#include "llvm/ADT/SmallPtrSet.h"#include "llvm/ADT/SmallSet.h"#include "llvm/ADT/SmallVector.h"#include "llvm/ADT/Triple.h"#include "llvm/CodeGen/Analysis.h"#include "llvm/CodeGen/MachineFunction.h"#include "llvm/CodeGen/MachineJumpTableInfo.h"#include "llvm/IR/CallingConv.h"#include "llvm/IR/Constants.h"#include "llvm/IR/DataLayout.h"#include "llvm/IR/DebugInfo.h"#include "llvm/IR/DerivedTypes.h"#include "llvm/IR/Function.h"#include "llvm/IR/LLVMContext.h"#include "llvm/Support/Debug.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/MathExtras.h"#include "llvm/Support/raw_ostream.h"#include "llvm/Target/TargetFrameLowering.h"#include "llvm/Target/TargetLowering.h"#include "llvm/Target/TargetMachine.h"#include "llvm/Target/TargetSubtargetInfo.h"

Go to the source code of this file.

Defines | |

| #define | DEBUG_TYPE "legalizedag" |

Functions | |

| static void | ExpandUnalignedStore (StoreSDNode *ST, SelectionDAG &DAG, const TargetLowering &TLI, SelectionDAGLegalize *DAGLegalize) |

| ExpandUnalignedStore - Expands an unaligned store to 2 half-size stores. | |

| static void | ExpandUnalignedLoad (LoadSDNode *LD, SelectionDAG &DAG, const TargetLowering &TLI, SDValue &ValResult, SDValue &ChainResult) |

| ExpandUnalignedLoad - Expands an unaligned load to 2 half-size loads. | |

| static bool | ExpandBVWithShuffles (SDNode *Node, SelectionDAG &DAG, const TargetLowering &TLI, SDValue &Res) |

| static bool | isDivRemLibcallAvailable (SDNode *Node, bool isSigned, const TargetLowering &TLI) |

| isDivRemLibcallAvailable - Return true if divmod libcall is available. | |

| static bool | useDivRem (SDNode *Node, bool isSigned, bool isDIV) |

| static bool | isSinCosLibcallAvailable (SDNode *Node, const TargetLowering &TLI) |

| isSinCosLibcallAvailable - Return true if sincos libcall is available. | |

| static bool | canCombineSinCosLibcall (SDNode *Node, const TargetLowering &TLI, const TargetMachine &TM) |

| static bool | useSinCos (SDNode *Node) |

Define Documentation

| #define DEBUG_TYPE "legalizedag" |

Definition at line 40 of file LegalizeDAG.cpp.

Function Documentation

| static bool canCombineSinCosLibcall | ( | SDNode * | Node, |

| const TargetLowering & | TLI, | ||

| const TargetMachine & | TM | ||

| ) | [static] |

canCombineSinCosLibcall - Return true if sincos libcall is available and can be used to combine sin and cos.

Definition at line 2301 of file LegalizeDAG.cpp.

References llvm::TargetMachine::getTargetTriple(), llvm::Triple::GNU, isSinCosLibcallAvailable(), llvm::TargetMachine::Options, and llvm::TargetOptions::UnsafeFPMath.

| static bool ExpandBVWithShuffles | ( | SDNode * | Node, |

| SelectionDAG & | DAG, | ||

| const TargetLowering & | TLI, | ||

| SDValue & | Res | ||

| ) | [static] |

Definition at line 1827 of file LegalizeDAG.cpp.

References llvm::SmallVectorTemplateCommon< T >::back(), llvm::SmallVectorImpl< T >::clear(), llvm::SmallVectorTemplateCommon< T, typename >::data(), llvm::SelectionDAG::getNode(), llvm::SDNode::getNumOperands(), llvm::SDValue::getOpcode(), llvm::SDNode::getOperand(), llvm::SelectionDAG::getUNDEF(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVectorShuffle(), llvm::TargetLoweringBase::isShuffleMaskLegal(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SmallVectorImpl< T >::reserve(), llvm::ISD::SCALAR_TO_VECTOR, llvm::SmallVectorTemplateCommon< T >::size(), llvm::SmallVectorImpl< T >::swap(), and llvm::ISD::UNDEF.

| static void ExpandUnalignedLoad | ( | LoadSDNode * | LD, |

| SelectionDAG & | DAG, | ||

| const TargetLowering & | TLI, | ||

| SDValue & | ValResult, | ||

| SDValue & | ChainResult | ||

| ) | [static] |

ExpandUnalignedLoad - Expands an unaligned load to 2 half-size loads.

Definition at line 414 of file LegalizeDAG.cpp.

References llvm::ISD::ADD, llvm::ISD::ANY_EXTEND, llvm::ISD::BITCAST, llvm::SelectionDAG::CreateStackTemporary(), llvm::ISD::EXTLOAD, llvm::ISD::FP_EXTEND, llvm::MemSDNode::getAAInfo(), llvm::LSBaseSDNode::getAddressingMode(), llvm::MemSDNode::getAlignment(), llvm::LoadSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::LoadSDNode::getExtensionType(), llvm::SelectionDAG::getExtLoad(), llvm::EVT::getIntegerVT(), llvm::SelectionDAG::getLoad(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SelectionDAG::getNode(), llvm::MemSDNode::getPointerInfo(), llvm::TargetLoweringBase::getPointerTy(), llvm::TargetLoweringBase::getRegisterType(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::EVT::getSizeInBits(), llvm::MVT::getSizeInBits(), llvm::SelectionDAG::getStore(), llvm::SelectionDAG::getTruncStore(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::MachinePointerInfo::getWithOffset(), llvm::HexagonISD::Hi, llvm::EVT::isFloatingPoint(), llvm::EVT::isInteger(), llvm::MemSDNode::isInvariant(), llvm::TargetLoweringBase::isLittleEndian(), llvm::MemSDNode::isNonTemporal(), llvm::TargetLoweringBase::isTypeLegal(), llvm::EVT::isVector(), llvm::MemSDNode::isVolatile(), llvm::HexagonISD::Lo, llvm::SPII::Load, llvm::MinAlign(), llvm::ISD::NON_EXTLOAD, llvm::ISD::OR, llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::ISD::SHL, llvm::ISD::TokenFactor, llvm::ISD::UNINDEXED, and llvm::ISD::ZEXTLOAD.

| static void ExpandUnalignedStore | ( | StoreSDNode * | ST, |

| SelectionDAG & | DAG, | ||

| const TargetLowering & | TLI, | ||

| SelectionDAGLegalize * | DAGLegalize | ||

| ) | [static] |

ExpandUnalignedStore - Expands an unaligned store to 2 half-size stores.

Definition at line 290 of file LegalizeDAG.cpp.

References llvm::ISD::ADD, llvm::ISD::BITCAST, llvm::SelectionDAG::CreateStackTemporary(), llvm::ISD::EXTLOAD, llvm::MemSDNode::getAAInfo(), llvm::LSBaseSDNode::getAddressingMode(), llvm::MemSDNode::getAddressSpace(), llvm::MemSDNode::getAlignment(), llvm::StoreSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getExtLoad(), llvm::EVT::getHalfSizedIntegerVT(), llvm::EVT::getIntegerVT(), llvm::SelectionDAG::getLoad(), llvm::MemSDNode::getMemoryVT(), llvm::SelectionDAG::getNode(), llvm::MemSDNode::getPointerInfo(), llvm::TargetLoweringBase::getPointerTy(), llvm::TargetLoweringBase::getRegisterType(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::EVT::getSizeInBits(), llvm::MVT::getSizeInBits(), llvm::SelectionDAG::getStore(), llvm::SelectionDAG::getTruncStore(), llvm::SDValue::getValue(), llvm::StoreSDNode::getValue(), llvm::SDValue::getValueType(), llvm::MachinePointerInfo::getWithOffset(), llvm::HexagonISD::Hi, llvm::EVT::isFloatingPoint(), llvm::EVT::isInteger(), llvm::TargetLoweringBase::isLittleEndian(), llvm::MemSDNode::isNonTemporal(), llvm::TargetLoweringBase::isTypeLegal(), llvm::EVT::isVector(), llvm::MemSDNode::isVolatile(), llvm::HexagonISD::Lo, llvm::SPII::Load, llvm::MinAlign(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::ISD::SRL, llvm::SPII::Store, llvm::ISD::TokenFactor, and llvm::ISD::UNINDEXED.

| static bool isDivRemLibcallAvailable | ( | SDNode * | Node, |

| bool | isSigned, | ||

| const TargetLowering & | TLI | ||

| ) | [static] |

isDivRemLibcallAvailable - Return true if divmod libcall is available.

Definition at line 2181 of file LegalizeDAG.cpp.

References llvm::TargetLoweringBase::getLibcallName(), llvm::SDNode::getSimpleValueType(), llvm::MVT::i128, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm_unreachable, llvm::RTLIB::SDIVREM_I128, llvm::RTLIB::SDIVREM_I16, llvm::RTLIB::SDIVREM_I32, llvm::RTLIB::SDIVREM_I64, llvm::RTLIB::SDIVREM_I8, llvm::MVT::SimpleTy, llvm::RTLIB::UDIVREM_I128, llvm::RTLIB::UDIVREM_I16, llvm::RTLIB::UDIVREM_I32, llvm::RTLIB::UDIVREM_I64, and llvm::RTLIB::UDIVREM_I8.

| static bool isSinCosLibcallAvailable | ( | SDNode * | Node, |

| const TargetLowering & | TLI | ||

| ) | [static] |

isSinCosLibcallAvailable - Return true if sincos libcall is available.

Definition at line 2286 of file LegalizeDAG.cpp.

References llvm::MVT::f128, llvm::MVT::f32, llvm::MVT::f64, llvm::MVT::f80, llvm::TargetLoweringBase::getLibcallName(), llvm::SDNode::getSimpleValueType(), llvm_unreachable, llvm::MVT::ppcf128, llvm::MVT::SimpleTy, llvm::RTLIB::SINCOS_F128, llvm::RTLIB::SINCOS_F32, llvm::RTLIB::SINCOS_F64, llvm::RTLIB::SINCOS_F80, and llvm::RTLIB::SINCOS_PPCF128.

Referenced by canCombineSinCosLibcall().

useDivRem - Only issue divrem libcall if both quotient and remainder are needed.

Definition at line 2198 of file LegalizeDAG.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::ISD::SDIV, llvm::ISD::SDIVREM, llvm::ISD::SREM, llvm::ISD::UDIV, llvm::ISD::UDIVREM, llvm::ISD::UREM, llvm::SDNode::use_begin(), and llvm::SDNode::use_end().

useSinCos - Only issue sincos libcall if both sin and cos are needed.

Definition at line 2315 of file LegalizeDAG.cpp.

References llvm::ISD::FCOS, llvm::ISD::FSIN, llvm::ISD::FSINCOS, llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::SDNode::use_begin(), and llvm::SDNode::use_end().

1.7.6.1

1.7.6.1