#include <TargetLowering.h>

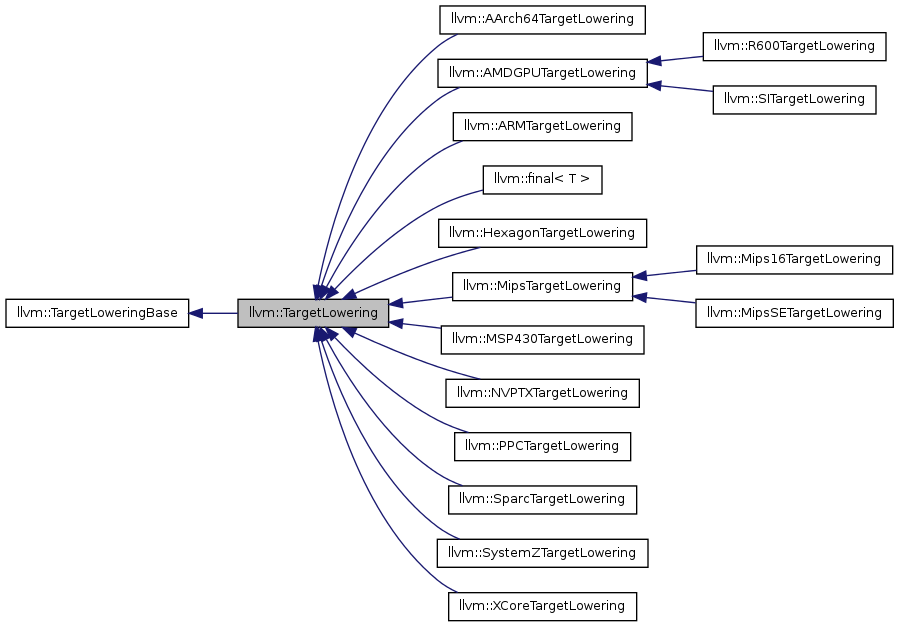

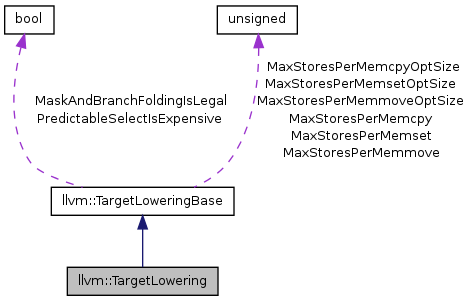

Detailed Description

This class defines information used to lower LLVM code to legal SelectionDAG operators that the target instruction selector can accept natively.

This class also defines callbacks that targets must implement to lower target-specific constructs to SelectionDAG operators.

Definition at line 1903 of file TargetLowering.h.

Member Typedef Documentation

| typedef std::vector<ArgListEntry> llvm::TargetLowering::ArgListTy |

Definition at line 2170 of file TargetLowering.h.

| typedef std::vector<AsmOperandInfo> llvm::TargetLowering::AsmOperandInfoVector |

Definition at line 2528 of file TargetLowering.h.

Member Enumeration Documentation

Definition at line 2469 of file TargetLowering.h.

- Enumerator:

CW_Invalid CW_Okay CW_Good CW_Better CW_Best CW_SpecificReg CW_Register CW_Memory CW_Constant CW_Default

Definition at line 2477 of file TargetLowering.h.

Constructor & Destructor Documentation

| TargetLowering::TargetLowering | ( | const TargetMachine & | TM, |

| const TargetLoweringObjectFile * | TLOF | ||

| ) | [explicit] |

NOTE: The constructor takes ownership of TLOF.

Definition at line 39 of file TargetLowering.cpp.

Member Function Documentation

| void TargetLowering::AdjustInstrPostInstrSelection | ( | MachineInstr * | MI, |

| SDNode * | Node | ||

| ) | const [virtual] |

This method should be implemented by targets that mark instructions with the 'hasPostISelHook' flag. These instructions must be adjusted after instruction selection by target hooks. e.g. To fill in optional defs for ARM 's' setting instructions.

Reimplemented in llvm::ARMTargetLowering, and llvm::SITargetLowering.

Definition at line 325 of file SelectionDAGISel.cpp.

References llvm::MachineInstr::hasPostISelHook().

| SDValue TargetLowering::BuildExactSDIV | ( | SDValue | Op1, |

| SDValue | Op2, | ||

| SDLoc | dl, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Given an exact SDIV by a constant, create a multiplication with the multiplicative inverse of the constant.

Definition at line 2619 of file TargetLowering.cpp.

References llvm::CallingConv::C, llvm::ConstantSDNode::getAPIntValue(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::SDValue::getValueType(), llvm::ISD::MUL, and llvm::ISD::SRA.

| SDValue TargetLowering::BuildSDIV | ( | SDNode * | N, |

| const APInt & | Divisor, | ||

| SelectionDAG & | DAG, | ||

| bool | IsAfterLegalization, | ||

| std::vector< SDNode * > * | Created | ||

| ) | const |

Given an ISD::SDIV node expressing a divide by constant, return a DAG expression to select that will generate the same value by multiplying by a magic number. Ref: "Hacker's Delight" or "The PowerPC Compiler Writer's Guide".

Definition at line 2648 of file TargetLowering.cpp.

References llvm::ISD::ADD, llvm::SelectionDAG::getConstant(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOperand(), llvm::EVT::getScalarSizeInBits(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVTList(), llvm::APInt::isNegative(), llvm::TargetLoweringBase::isOperationLegal(), llvm::TargetLoweringBase::isOperationLegalOrCustom(), llvm::APInt::isStrictlyPositive(), llvm::TargetLoweringBase::isTypeLegal(), llvm::APInt::ms::m, llvm::APInt::magic(), llvm::ISD::MULHS, llvm::APInt::ms::s, llvm::ISD::SMUL_LOHI, llvm::ISD::SRA, llvm::ISD::SRL, and llvm::ISD::SUB.

| virtual SDValue llvm::TargetLowering::BuildSDIVPow2 | ( | SDNode * | N, |

| const APInt & | Divisor, | ||

| SelectionDAG & | DAG, | ||

| std::vector< SDNode * > * | Created | ||

| ) | const [inline, virtual] |

Definition at line 2592 of file TargetLowering.h.

| SDValue TargetLowering::BuildUDIV | ( | SDNode * | N, |

| const APInt & | Divisor, | ||

| SelectionDAG & | DAG, | ||

| bool | IsAfterLegalization, | ||

| std::vector< SDNode * > * | Created | ||

| ) | const |

Given an ISD::UDIV node expressing a divide by constant, return a DAG expression to select that will generate the same value by multiplying by a magic number. Ref: "Hacker's Delight" or "The PowerPC Compiler Writer's Guide".

Definition at line 2705 of file TargetLowering.cpp.

References llvm::APInt::mu::a, llvm::ISD::ADD, llvm::APInt::countTrailingZeros(), llvm::APInt::getBitWidth(), llvm::SelectionDAG::getConstant(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOperand(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVTList(), llvm::TargetLoweringBase::isOperationLegal(), llvm::TargetLoweringBase::isOperationLegalOrCustom(), llvm::TargetLoweringBase::isTypeLegal(), llvm::APInt::lshr(), llvm::APInt::mu::m, llvm::APInt::magicu(), llvm::ISD::MULHU, llvm::APInt::mu::s, llvm::ISD::SRL, llvm::ISD::SUB, and llvm::ISD::UMUL_LOHI.

| virtual bool llvm::TargetLowering::CanLowerReturn | ( | CallingConv::ID | , |

| MachineFunction & | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::OutputArg > & | , | ||

| LLVMContext & | |||

| ) | const [inline, virtual] |

This hook should be implemented to check whether the return values described by the Outs array can fit into the return registers. If false is returned, an sret-demotion is performed.

Definition at line 2315 of file TargetLowering.h.

Referenced by llvm::FastISel::lowerCallTo(), LowerCallTo(), and llvm::FunctionLoweringInfo::set().

| void TargetLowering::ComputeConstraintToUse | ( | AsmOperandInfo & | OpInfo, |

| SDValue | Op, | ||

| SelectionDAG * | DAG = nullptr |

||

| ) | const [virtual] |

Determines the constraint code and constraint type to use for the specific AsmOperandInfo, setting OpInfo.ConstraintCode and OpInfo.ConstraintType. If the actual operand being passed in is available, it can be passed in as Op, otherwise an empty SDValue can be passed.

ComputeConstraintToUse - Determines the constraint code and constraint type to use for the specific AsmOperandInfo, setting OpInfo.ConstraintCode and OpInfo.ConstraintType.

Definition at line 2584 of file TargetLowering.cpp.

References llvm::TargetLowering::AsmOperandInfo::CallOperandVal, ChooseConstraint(), llvm::InlineAsm::ConstraintInfo::Codes, llvm::TargetLowering::AsmOperandInfo::ConstraintCode, llvm::TargetLowering::AsmOperandInfo::ConstraintType, llvm::TargetLowering::AsmOperandInfo::ConstraintVT, getConstraintType(), and LowerXConstraint().

Referenced by llvm::FunctionLoweringInfo::set().

| void TargetLowering::computeKnownBitsForTargetNode | ( | const SDValue | Op, |

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [virtual] |

Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

computeKnownBitsForTargetNode - Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, llvm::AMDGPUTargetLowering, and llvm::SparcTargetLowering.

Definition at line 1088 of file TargetLowering.cpp.

References llvm::ISD::BUILTIN_OP_END, llvm::APInt::getBitWidth(), llvm::SDValue::getOpcode(), llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, and llvm::ISD::INTRINSIC_WO_CHAIN.

Referenced by llvm::SelectionDAG::computeKnownBits().

| unsigned TargetLowering::ComputeNumSignBitsForTargetNode | ( | SDValue | Op, |

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [virtual] |

This method can be implemented by targets that want to expose additional information about sign bits to the DAG Combiner.

ComputeNumSignBitsForTargetNode - This method can be implemented by targets that want to expose additional information about sign bits to the DAG Combiner.

Reimplemented in llvm::final< T >, and llvm::AMDGPUTargetLowering.

Definition at line 1105 of file TargetLowering.cpp.

References llvm::ISD::BUILTIN_OP_END, llvm::SDValue::getOpcode(), llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, and llvm::ISD::INTRINSIC_WO_CHAIN.

Referenced by llvm::SelectionDAG::ComputeNumSignBits().

| virtual FastISel* llvm::TargetLowering::createFastISel | ( | FunctionLoweringInfo & | , |

| const TargetLibraryInfo * | |||

| ) | const [inline, virtual] |

This method returns a target specific FastISel object, or null if the target does not support "fast" ISel.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, and llvm::MipsTargetLowering.

Definition at line 2448 of file TargetLowering.h.

| MachineBasicBlock * TargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::AArch64TargetLowering, llvm::ARMTargetLowering, llvm::MipsTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::MSP430TargetLowering, llvm::XCoreTargetLowering, llvm::SITargetLowering, llvm::SparcTargetLowering, llvm::MipsSETargetLowering, llvm::Mips16TargetLowering, and llvm::R600TargetLowering.

Definition at line 315 of file SelectionDAGISel.cpp.

References llvm::dbgs(), and llvm_unreachable.

Referenced by INITIALIZE_PASS().

| bool TargetLowering::expandFP_TO_SINT | ( | SDNode * | N, |

| SDValue & | Result, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Expand float(f32) to SINT(i64) conversion

- Parameters:

-

N Node to expand Result output after conversion

- Returns:

- True, if the expansion was successful, false otherwise

Definition at line 2887 of file TargetLowering.cpp.

References llvm::ISD::AND, llvm::ISD::BITCAST, llvm::tgtok::Bits, llvm::MVT::f32, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::EVT::getIntegerVT(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOperand(), llvm::SelectionDAG::getSelectCC(), llvm::SelectionDAG::getSExtOrTrunc(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::APInt::getSignBit(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getZExtOrTrunc(), llvm::MVT::i64, llvm::ISD::OR, llvm::MipsISD::Ret, llvm::ISD::SETGT, llvm::ISD::SETLT, llvm::ISD::SHL, llvm::ISD::SRA, llvm::ISD::SRL, llvm::ISD::SUB, and llvm::ISD::XOR.

Referenced by llvm::R600TargetLowering::ReplaceNodeResults().

| virtual bool llvm::TargetLowering::ExpandInlineAsm | ( | CallInst * | ) | const [inline, virtual] |

This hook allows the target to expand an inline asm call to be explicit llvm code if it wants to. This is useful for turning simple inline asms into LLVM intrinsics, which gives the compiler more information about the behavior of the code.

Reimplemented in llvm::final< T >, and llvm::ARMTargetLowering.

Definition at line 2465 of file TargetLowering.h.

| bool TargetLowering::expandMUL | ( | SDNode * | N, |

| SDValue & | Lo, | ||

| SDValue & | Hi, | ||

| EVT | HiLoVT, | ||

| SelectionDAG & | DAG, | ||

| SDValue | LL = SDValue(), |

||

| SDValue | LH = SDValue(), |

||

| SDValue | RL = SDValue(), |

||

| SDValue | RH = SDValue() |

||

| ) | const |

Expand a MUL into two nodes. One that computes the high bits of the result and one that computes the low bits.

- Parameters:

-

HiLoVT The value type to use for the Lo and Hi nodes. LL Low bits of the LHS of the MUL. You can use this parameter if you want to control how low bits are extracted from the LHS. LH High bits of the LHS of the MUL. See LL for meaning. RL Low bits of the RHS of the MUL. See LL for meaning RH High bits of the RHS of the MUL. See LL for meaning.

- Returns:

- true if the node has been expanded. false if it has not

Definition at line 2784 of file TargetLowering.cpp.

References llvm::ISD::ADD, llvm::SelectionDAG::ComputeNumSignBits(), llvm::SelectionDAG::getConstant(), llvm::APInt::getHighBitsSet(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOperand(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValue(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVTList(), llvm::TargetLoweringBase::isOperationLegalOrCustom(), llvm::SelectionDAG::MaskedValueIsZero(), llvm::ISD::MUL, llvm::ISD::MULHS, llvm::ISD::MULHU, llvm::ISD::SMUL_LOHI, llvm::ISD::SRL, llvm::ISD::TRUNCATE, and llvm::ISD::UMUL_LOHI.

| virtual bool llvm::TargetLowering::functionArgumentNeedsConsecutiveRegisters | ( | Type * | Ty, |

| CallingConv::ID | CallConv, | ||

| bool | isVarArg | ||

| ) | const [inline, virtual] |

For some targets, an LLVM struct type must be broken down into multiple simple types, but the calling convention specifies that the entire struct must be passed in a block of consecutive registers.

Reimplemented in llvm::PPCTargetLowering, and llvm::ARMTargetLowering.

Definition at line 2381 of file TargetLowering.h.

Referenced by llvm::FastISel::lowerCallTo(), and LowerCallTo().

| virtual const char* llvm::TargetLowering::getClearCacheBuiltinName | ( | ) | const [inline, virtual] |

Return the builtin name for the __builtin___clear_cache intrinsic Default is to invoke the clear cache library call

Reimplemented in llvm::final< T >.

Definition at line 2354 of file TargetLowering.h.

| TargetLowering::ConstraintType TargetLowering::getConstraintType | ( | const std::string & | Constraint | ) | const [virtual] |

Given a constraint, return the type of constraint it is for this target.

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, llvm::MSP430TargetLowering, and llvm::SparcTargetLowering.

Definition at line 2049 of file TargetLowering.cpp.

References C_Memory, C_Other, C_Register, C_RegisterClass, and C_Unknown.

Referenced by ChooseConstraint(), ComputeConstraintToUse(), and llvm::hasInlineAsmMemConstraint().

| unsigned TargetLowering::getJumpTableEncoding | ( | ) | const [virtual] |

Return the entry encoding for a jump table in the current function. The returned value is a member of the MachineJumpTableInfo::JTEntryKind enum.

getJumpTableEncoding - Return the entry encoding for a jump table in the current function. The returned value is a member of the MachineJumpTableInfo::JTEntryKind enum.

Reimplemented in llvm::final< T >, llvm::ARMTargetLowering, and llvm::XCoreTargetLowering.

Definition at line 223 of file TargetLowering.cpp.

References llvm::MachineJumpTableInfo::EK_BlockAddress, llvm::MachineJumpTableInfo::EK_GPRel32BlockAddress, llvm::MachineJumpTableInfo::EK_LabelDifference32, llvm::TargetLoweringBase::getTargetMachine(), and llvm::Reloc::PIC_.

Referenced by getPICJumpTableRelocBase().

| TargetLowering::ConstraintWeight TargetLowering::getMultipleConstraintMatchWeight | ( | AsmOperandInfo & | info, |

| int | maIndex | ||

| ) | const [virtual] |

Examine constraint type and operand type and determine a weight value. The operand object must already have been set up with the operand type.

Examine constraint type and operand type and determine a weight value. This object must already have been set up with the operand type and the current alternative constraint selected.

Definition at line 2444 of file TargetLowering.cpp.

References llvm::c_str(), llvm::InlineAsm::ConstraintInfo::Codes, CW_Invalid, getSingleConstraintMatchWeight(), and llvm::InlineAsm::ConstraintInfo::multipleAlternatives.

Referenced by ParseConstraints().

| SDValue TargetLowering::getPICJumpTableRelocBase | ( | SDValue | Table, |

| SelectionDAG & | DAG | ||

| ) | const [virtual] |

Returns relocation base for the given PIC jumptable.

Reimplemented in llvm::final< T >.

Definition at line 236 of file TargetLowering.cpp.

References llvm::MachineJumpTableInfo::EK_GPRel32BlockAddress, llvm::MachineJumpTableInfo::EK_GPRel64BlockAddress, llvm::SelectionDAG::getGLOBAL_OFFSET_TABLE(), getJumpTableEncoding(), and llvm::TargetLoweringBase::getPointerTy().

| const MCExpr * TargetLowering::getPICJumpTableRelocBaseExpr | ( | const MachineFunction * | MF, |

| unsigned | JTI, | ||

| MCContext & | Ctx | ||

| ) | const [virtual] |

This returns the relocation base for the given PIC jumptable, the same as getPICJumpTableRelocBase, but as an MCExpr.

getPICJumpTableRelocBaseExpr - This returns the relocation base for the given PIC jumptable, the same as getPICJumpTableRelocBase, but as an MCExpr.

Reimplemented in llvm::final< T >.

Definition at line 252 of file TargetLowering.cpp.

References llvm::MCSymbolRefExpr::Create(), and llvm::MachineFunction::getJTISymbol().

Referenced by llvm::AsmPrinter::EmitJumpTableInfo().

| virtual bool llvm::TargetLowering::getPostIndexedAddressParts | ( | SDNode * | , |

| SDNode * | , | ||

| SDValue & | , | ||

| SDValue & | , | ||

| ISD::MemIndexedMode & | , | ||

| SelectionDAG & | |||

| ) | const [inline, virtual] |

Returns true by value, base pointer and offset pointer and addressing mode by reference if this node can be combined with a load / store to form a post-indexed load / store.

Reimplemented in llvm::ARMTargetLowering, and llvm::HexagonTargetLowering.

Definition at line 1925 of file TargetLowering.h.

| virtual bool llvm::TargetLowering::getPreIndexedAddressParts | ( | SDNode * | , |

| SDValue & | , | ||

| SDValue & | , | ||

| ISD::MemIndexedMode & | , | ||

| SelectionDAG & | |||

| ) | const [inline, virtual] |

Returns true by value, base pointer and offset pointer and addressing mode by reference if the node's address can be legally represented as pre-indexed load / store address.

Reimplemented in llvm::PPCTargetLowering, and llvm::ARMTargetLowering.

Definition at line 1915 of file TargetLowering.h.

| std::pair< unsigned, const TargetRegisterClass * > TargetLowering::getRegForInlineAsmConstraint | ( | const std::string & | Constraint, |

| MVT | VT | ||

| ) | const [virtual] |

Given a physical register constraint (e.g. {edx}), return the register number and the register class for the register.

Given a register class constraint, like 'r', if this corresponds directly to an LLVM register class, return a register of 0 and the register class pointer.

This should only be used for C_Register constraints. On error, this returns a register number of 0 and a null register class pointer..

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::MSP430TargetLowering, and llvm::SparcTargetLowering.

Definition at line 2168 of file TargetLowering.cpp.

References llvm::TargetRegisterClass::begin(), llvm::TargetRegisterClass::end(), llvm::MCRegisterInfo::getName(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::TargetRegisterClass::hasType(), I, llvm::TargetLoweringBase::isLegalRC(), llvm::TargetRegisterInfo::regclass_begin(), and llvm::TargetRegisterInfo::regclass_end().

Referenced by GetRegistersForValue(), ParseConstraints(), and llvm::FunctionLoweringInfo::set().

| virtual unsigned llvm::TargetLowering::getRegisterByName | ( | const char * | RegName, |

| EVT | VT | ||

| ) | const [inline, virtual] |

Return the register ID of the name passed in. Used by named register global variables extension. There is no target-independent behaviour so the default action is to bail.

Reimplemented in llvm::final< T >, and llvm::PPCTargetLowering.

Definition at line 2361 of file TargetLowering.h.

References llvm::report_fatal_error().

| virtual const MCPhysReg* llvm::TargetLowering::getScratchRegisters | ( | CallingConv::ID | CC | ) | const [inline, virtual] |

Returns a 0 terminated array of registers that can be safely used as scratch registers.

Reimplemented in llvm::AArch64TargetLowering.

Definition at line 2388 of file TargetLowering.h.

Referenced by llvm::FastISel::selectPatchpoint(), and llvm::FastISel::selectStackmap().

| TargetLowering::ConstraintWeight TargetLowering::getSingleConstraintMatchWeight | ( | AsmOperandInfo & | info, |

| const char * | constraint | ||

| ) | const [virtual] |

Examine constraint string and operand type and determine a weight value. The operand object must already have been set up with the operand type.

Examine constraint type and operand type and determine a weight value. This object must already have been set up with the operand type and the current alternative constraint selected.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, and llvm::SparcTargetLowering.

Definition at line 2468 of file TargetLowering.cpp.

References llvm::TargetLowering::AsmOperandInfo::CallOperandVal, CW_Constant, CW_Default, CW_Invalid, CW_Memory, CW_Register, llvm::Value::getType(), and llvm::Type::isIntegerTy().

Referenced by getMultipleConstraintMatchWeight().

| const char * TargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [virtual] |

This method returns the name of a target specific DAG node.

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::MipsTargetLowering, llvm::AArch64TargetLowering, llvm::SystemZTargetLowering, llvm::AMDGPUTargetLowering, llvm::XCoreTargetLowering, llvm::HexagonTargetLowering, llvm::MSP430TargetLowering, and llvm::SparcTargetLowering.

Definition at line 43 of file TargetLowering.cpp.

Referenced by llvm::SDNode::getOperationName().

| virtual EVT llvm::TargetLowering::getTypeForExtArgOrReturn | ( | LLVMContext & | Context, |

| EVT | VT, | ||

| ISD::NodeType | |||

| ) | const [inline, virtual] |

Return the type that should be used to zero or sign extend a zeroext/signext integer argument or return value. FIXME: Most C calling convention requires the return type to be promoted, but this is not true all the time, e.g. i1 on x86-64. It is also not necessary for non-C calling conventions. The frontend should handle this and include all of the necessary information.

Definition at line 2371 of file TargetLowering.h.

References llvm::EVT::bitsLT(), llvm::TargetLoweringBase::getRegisterType(), and llvm::MVT::i32.

| virtual void llvm::TargetLowering::HandleByVal | ( | CCState * | , |

| unsigned & | , | ||

| unsigned | |||

| ) | const [inline, virtual] |

Target-specific cleanup for formal ByVal parameters.

Definition at line 2310 of file TargetLowering.h.

Referenced by llvm::CCState::HandleByVal().

| bool TargetLowering::isConstFalseVal | ( | const SDNode * | N | ) | const |

Return if the N is a constant or constant vector equal to the false value from getBooleanContents().

Definition at line 1180 of file TargetLowering.cpp.

References llvm::dyn_cast(), llvm::ConstantSDNode::getAPIntValue(), llvm::TargetLoweringBase::getBooleanContents(), llvm::BuildVectorSDNode::getConstantSplatNode(), llvm::SDNode::getValueType(), llvm::ConstantSDNode::isNullValue(), llvm::BitVector::none(), and llvm::TargetLoweringBase::UndefinedBooleanContent.

| bool TargetLowering::isConstTrueVal | ( | const SDNode * | N | ) | const |

Return if the N is a constant or constant vector equal to the true value from getBooleanContents().

Definition at line 1150 of file TargetLowering.cpp.

References llvm::dyn_cast(), llvm::ConstantSDNode::getAPIntValue(), llvm::TargetLoweringBase::getBooleanContents(), llvm::BuildVectorSDNode::getConstantSplatNode(), llvm::SDNode::getValueType(), llvm::ConstantSDNode::isAllOnesValue(), llvm::ConstantSDNode::isOne(), llvm_unreachable, llvm::BitVector::none(), llvm::TargetLoweringBase::UndefinedBooleanContent, llvm::TargetLoweringBase::ZeroOrNegativeOneBooleanContent, and llvm::TargetLoweringBase::ZeroOrOneBooleanContent.

| virtual bool llvm::TargetLowering::isDesirableToCommuteWithShift | ( | const SDNode * | N | ) | const [inline, virtual] |

Return true if it is profitable to move a following shift through this.

Reimplemented in llvm::AArch64TargetLowering.

Definition at line 2104 of file TargetLowering.h.

| virtual bool llvm::TargetLowering::IsDesirableToPromoteOp | ( | SDValue | , |

| EVT & | |||

| ) | const [inline, virtual] |

This method query the target whether it is beneficial for dag combiner to promote the specified node. If true, it should return the desired promotion type by reference.

Reimplemented in llvm::final< T >.

Definition at line 2128 of file TargetLowering.h.

| virtual bool llvm::TargetLowering::isDesirableToTransformToIntegerOp | ( | unsigned | , |

| EVT | |||

| ) | const [inline, virtual] |

Return true if it is profitable for dag combiner to transform a floating point op of specified opcode to a equivalent op of an integer type. e.g. f32 load -> i32 load can be profitable on ARM.

Reimplemented in llvm::ARMTargetLowering.

Definition at line 2120 of file TargetLowering.h.

| bool TargetLowering::isGAPlusOffset | ( | SDNode * | N, |

| const GlobalValue *& | GA, | ||

| int64_t & | Offset | ||

| ) | const [virtual] |

Returns true (and the GlobalValue and the offset) if the node is a GlobalAddress + offset.

isGAPlusOffset - Returns true (and the GlobalValue and the offset) if the node is a GlobalAddress + offset.

Reimplemented in llvm::final< T >.

Definition at line 2006 of file TargetLowering.cpp.

References ADD, llvm::dyn_cast(), llvm::GlobalAddressSDNode::getGlobal(), llvm::SDValue::getNode(), llvm::GlobalAddressSDNode::getOffset(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), and llvm::ConstantSDNode::getSExtValue().

Referenced by llvm::SelectionDAG::InferPtrAlignment(), llvm::SelectionDAG::isConsecutiveLoad(), and isConsecutiveLSLoc().

| bool TargetLowering::isInTailCallPosition | ( | SelectionDAG & | DAG, |

| SDNode * | Node, | ||

| SDValue & | Chain | ||

| ) | const |

Check whether a given call node is in tail position within its function. If so, it sets Chain to the input chain of the tail call.

Definition at line 49 of file TargetLowering.cpp.

References F(), llvm::Function::getAttributes(), llvm::MachineFunction::getFunction(), llvm::SelectionDAG::getMachineFunction(), llvm::AttributeSet::hasAttribute(), isUsedByReturnOnly(), llvm::Attribute::NoAlias, llvm::AttributeSet::ReturnIndex, llvm::Attribute::SExt, and llvm::Attribute::ZExt.

| bool TargetLowering::isOffsetFoldingLegal | ( | const GlobalAddressSDNode * | GA | ) | const [virtual] |

Return true if folding a constant offset with the given GlobalAddress is legal. It is frequently not legal in PIC relocation models.

Reimplemented in llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, and llvm::SparcTargetLowering.

Definition at line 259 of file TargetLowering.cpp.

References llvm::Reloc::DynamicNoPIC, llvm::GlobalAddressSDNode::getGlobal(), llvm::TargetLoweringBase::getTargetMachine(), llvm::GlobalValue::isDeclaration(), llvm::GlobalValue::isWeakForLinker(), and llvm::Reloc::Static.

| virtual bool llvm::TargetLowering::isTypeDesirableForOp | ( | unsigned | , |

| EVT | VT | ||

| ) | const [inline, virtual] |

Return true if the target has native support for the specified value type and it is 'desirable' to use the type for the given node type. e.g. On x86 i16 is legal, but undesirable since i16 instruction encodings are longer and some i16 instructions are slow.

Reimplemented in llvm::final< T >.

Definition at line 2112 of file TargetLowering.h.

References llvm::TargetLoweringBase::isTypeLegal().

Referenced by SimplifyDemandedBits(), and SimplifySetCC().

| virtual bool llvm::TargetLowering::isUsedByReturnOnly | ( | SDNode * | , |

| SDValue & | |||

| ) | const [inline, virtual] |

Return true if result of the specified node is used by a return node only. It also compute and return the input chain for the tail call.

This is used to determine whether it is possible to codegen a libcall as tail call at legalization time.

Definition at line 2341 of file TargetLowering.h.

Referenced by isInTailCallPosition().

| void TargetLowering::LowerAsmOperandForConstraint | ( | SDValue | Op, |

| std::string & | Constraint, | ||

| std::vector< SDValue > & | Ops, | ||

| SelectionDAG & | DAG | ||

| ) | const [virtual] |

Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops.

LowerAsmOperandForConstraint - Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops.

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::SystemZTargetLowering, and llvm::SparcTargetLowering.

Definition at line 2102 of file TargetLowering.cpp.

References ADD, llvm::ISD::BasicBlock, llvm::CallingConv::C, llvm::dyn_cast(), llvm::ConstantSDNode::getAPIntValue(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::APInt::getSExtValue(), llvm::SelectionDAG::getTargetConstant(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::SDValue::getValueType(), llvm::ConstantSDNode::getZExtValue(), and llvm::MVT::i64.

Referenced by ChooseConstraint().

| virtual SDValue llvm::TargetLowering::LowerCall | ( | CallLoweringInfo & | , |

| SmallVectorImpl< SDValue > & | |||

| ) | const [inline, virtual] |

This hook must be implemented to lower calls into the the specified DAG. The outgoing arguments to the call are described by the Outs array, and the values to be returned by the call are described by the Ins array. The implementation should fill in the InVals array with legal-type return values from the call, and return the resulting token chain value.

Reimplemented in llvm::NVPTXTargetLowering, llvm::SystemZTargetLowering, llvm::AMDGPUTargetLowering, llvm::HexagonTargetLowering, and llvm::SparcTargetLowering.

Definition at line 2304 of file TargetLowering.h.

References llvm_unreachable.

Referenced by LowerCallTo().

| std::pair< SDValue, SDValue > TargetLowering::LowerCallTo | ( | TargetLowering::CallLoweringInfo & | CLI | ) | const |

This function lowers an abstract call to a function into an actual call. This returns a pair of operands. The first element is the return value for the function (if RetTy is not VoidTy). The second element is the outgoing token chain. It calls LowerCall to do the actual lowering.

TargetLowering::LowerCallTo - This is the default LowerCallTo implementation, which just calls LowerCall. FIXME: When all targets are migrated to using LowerCall, this hook should be integrated into SDISel.

Definition at line 7150 of file SelectionDAGBuilder.cpp.

References llvm::ISD::ADD, Align(), llvm::TargetLowering::ArgListEntry::Alignment, llvm::ISD::ANY_EXTEND, llvm::ISD::InputArg::ArgVT, llvm::ISD::AssertSext, llvm::ISD::AssertZext, llvm::TargetLowering::CallLoweringInfo::CallConv, CanLowerReturn(), llvm::TargetLowering::CallLoweringInfo::Chain, llvm::SmallVectorImpl< T >::clear(), llvm::ComputeValueVTs(), llvm::MachineFrameInfo::CreateStackObject(), llvm::TargetLowering::CallLoweringInfo::CS, llvm::TargetLowering::CallLoweringInfo::DAG, DEBUG, llvm::ISD::DELETED_NODE, llvm::TargetLowering::CallLoweringInfo::DL, llvm::SmallVectorBase::empty(), llvm::ISD::InputArg::Flags, llvm::ISD::OutputArg::Flags, functionArgumentNeedsConsecutiveRegisters(), llvm::DataLayout::getABITypeAlignment(), llvm::TargetLowering::CallLoweringInfo::getArgs(), llvm::TargetLoweringBase::getByValTypeAlignment(), llvm::SelectionDAG::getConstant(), llvm::Type::getContext(), getCopyFromParts(), getCopyToParts(), llvm::TargetLoweringBase::getDataLayout(), llvm::SequentialType::getElementType(), llvm::MachinePointerInfo::getFixedStack(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::CallSiteBase< FunTy, ValTy, UserTy, InstrTy, CallTy, InvokeTy, IterTy >::getInstruction(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getNumRegisters(), llvm::TargetLoweringBase::getPointerTy(), llvm::DataLayout::getPrefTypeAlignment(), llvm::TargetLoweringBase::getRegisterType(), getReturnAttrs(), llvm::GetReturnInfo(), llvm::EVT::getSizeInBits(), llvm::MVT::getSizeInBits(), llvm::DataLayout::getTypeAllocSize(), llvm::EVT::getTypeForEVT(), llvm::PointerType::getUnqual(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::TargetLoweringBase::getValueType(), llvm::Type::getVoidTy(), llvm::SelectionDAG::getVTList(), I, llvm::TargetLowering::CallLoweringInfo::Ins, llvm::TargetLowering::ArgListEntry::isByVal, llvm::TargetLowering::ArgListEntry::isInReg, llvm::TargetLowering::CallLoweringInfo::IsInReg, llvm::TargetLowering::ArgListEntry::isNest, llvm::TargetLowering::ArgListEntry::isReturned, llvm::TargetLowering::CallLoweringInfo::IsReturnValueUsed, llvm::TargetLowering::ArgListEntry::isSExt, llvm::TargetLowering::ArgListEntry::isSRet, llvm::TargetLowering::CallLoweringInfo::IsTailCall, llvm::TargetLowering::CallLoweringInfo::IsVarArg, llvm::EVT::isVector(), llvm::TargetLowering::ArgListEntry::isZExt, LowerCall(), llvm::ISD::MERGE_VALUES, llvm::FoldingSetImpl::Node::Node(), llvm::TargetLowering::ArgListEntry::Node, llvm::TargetLowering::CallLoweringInfo::NumFixedArgs, llvm::MVT::Other, llvm::TargetLowering::CallLoweringInfo::Outs, llvm::TargetLowering::CallLoweringInfo::OutVals, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::TargetLowering::CallLoweringInfo::RetSExt, llvm::TargetLowering::CallLoweringInfo::RetTy, llvm::TargetLowering::CallLoweringInfo::RetZExt, llvm::ISD::ArgFlagsTy::setInReg(), llvm::SelectionDAG::setRoot(), llvm::ISD::ArgFlagsTy::setSExt(), llvm::ISD::ArgFlagsTy::setSplit(), llvm::ISD::ArgFlagsTy::setZExt(), llvm::ISD::SIGN_EXTEND, llvm::SmallVectorTemplateCommon< T, typename >::size(), llvm::SmallVectorTemplateCommon< T >::size(), llvm::ISD::TokenFactor, llvm::TargetLowering::ArgListEntry::Ty, llvm::ISD::InputArg::Used, llvm::ISD::InputArg::VT, and llvm::ISD::ZERO_EXTEND.

Referenced by llvm::XCoreSelectionDAGInfo::EmitTargetCodeForMemcpy(), llvm::AArch64SelectionDAGInfo::EmitTargetCodeForMemset(), llvm::X86SelectionDAGInfo::EmitTargetCodeForMemset(), llvm::ARMSelectionDAGInfo::EmitTargetCodeForMemset(), llvm::SelectionDAG::getMemcpy(), llvm::SelectionDAG::getMemmove(), llvm::SelectionDAG::getMemset(), llvm::SelectionDAGBuilder::LowerCallOperands(), llvm::SelectionDAGBuilder::LowerCallTo(), llvm::SparcTargetLowering::LowerF128Compare(), llvm::SparcTargetLowering::LowerF128Op(), LowerFSINCOS(), and makeLibCall().

| virtual const MCExpr* llvm::TargetLowering::LowerCustomJumpTableEntry | ( | const MachineJumpTableInfo * | , |

| const MachineBasicBlock * | , | ||

| unsigned | , | ||

| MCContext & | |||

| ) | const [inline, virtual] |

Reimplemented in llvm::final< T >.

Definition at line 1938 of file TargetLowering.h.

References llvm_unreachable.

| virtual SDValue llvm::TargetLowering::LowerFormalArguments | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::InputArg > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | , | ||

| SmallVectorImpl< SDValue > & | |||

| ) | const [inline, virtual] |

This hook must be implemented to lower the incoming (formal) arguments, described by the Ins array, into the specified DAG. The implementation should fill in the InVals array with legal-type argument values, and return the resulting token chain value.

Reimplemented in llvm::NVPTXTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::SparcTargetLowering, llvm::SITargetLowering, and llvm::R600TargetLowering.

Definition at line 2143 of file TargetLowering.h.

References llvm_unreachable.

| SDValue TargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [virtual] |

This callback is invoked for operations that are unsupported by the target, which are registered to use 'custom' lowering, and whose defined values are all legal. If the target has no operations that require custom lowering, it need not implement this. The default implementation of this aborts.

Reimplemented in llvm::final< T >, llvm::NVPTXTargetLowering, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::AArch64TargetLowering, llvm::MipsTargetLowering, llvm::SystemZTargetLowering, llvm::AMDGPUTargetLowering, llvm::XCoreTargetLowering, llvm::HexagonTargetLowering, llvm::SITargetLowering, llvm::MSP430TargetLowering, llvm::SparcTargetLowering, llvm::MipsSETargetLowering, and llvm::R600TargetLowering.

Definition at line 7417 of file SelectionDAGBuilder.cpp.

References llvm_unreachable.

Referenced by LowerOperationWrapper().

| void TargetLowering::LowerOperationWrapper | ( | SDNode * | N, |

| SmallVectorImpl< SDValue > & | Results, | ||

| SelectionDAG & | DAG | ||

| ) | const [virtual] |

This callback is invoked by the type legalizer to legalize nodes with an illegal operand type but legal result types. It replaces the LowerOperation callback in the type Legalizer. The reason we can not do away with LowerOperation entirely is that LegalizeDAG isn't yet ready to use this callback.

TODO: Consider merging with ReplaceNodeResults.

The target places new result values for the node in Results (their number and types must exactly match those of the original return values of the node), or leaves Results empty, which indicates that the node is not to be custom lowered after all. The default implementation calls LowerOperation.

Reimplemented in llvm::MipsTargetLowering.

Definition at line 7409 of file SelectionDAGBuilder.cpp.

References llvm::SDValue::getNode(), LowerOperation(), and llvm::SmallVectorTemplateBase< T, isPodLike >::push_back().

| virtual SDValue llvm::TargetLowering::LowerReturn | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::OutputArg > & | , | ||

| const SmallVectorImpl< SDValue > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | |||

| ) | const [inline, virtual] |

This hook must be implemented to lower outgoing return values, described by the Outs array, into the specified DAG. The implementation should return the resulting token chain value.

Reimplemented in llvm::NVPTXTargetLowering, llvm::SystemZTargetLowering, llvm::HexagonTargetLowering, llvm::AMDGPUTargetLowering, and llvm::SparcTargetLowering.

Definition at line 2328 of file TargetLowering.h.

References llvm_unreachable.

| const char * TargetLowering::LowerXConstraint | ( | EVT | ConstraintVT | ) | const [virtual] |

Try to replace an X constraint, which matches anything, with another that has more specific requirements based on the type of the corresponding operand. This returns null if there is no replacement to make.

LowerXConstraint - try to replace an X constraint, which matches anything, with another that has more specific requirements based on the type of the corresponding operand.

Reimplemented in llvm::final< T >.

Definition at line 2092 of file TargetLowering.cpp.

References llvm::EVT::isFloatingPoint(), and llvm::EVT::isInteger().

Referenced by ComputeConstraintToUse().

| std::pair< SDValue, SDValue > TargetLowering::makeLibCall | ( | SelectionDAG & | DAG, |

| RTLIB::Libcall | LC, | ||

| EVT | RetVT, | ||

| const SDValue * | Ops, | ||

| unsigned | NumOps, | ||

| bool | isSigned, | ||

| SDLoc | dl, | ||

| bool | doesNotReturn = false, |

||

| bool | isReturnValueUsed = true |

||

| ) | const |

Returns a pair of (return value, chain).

Generate a libcall taking the given operands as arguments and returning a result of type RetVT.

Definition at line 87 of file TargetLowering.cpp.

References llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getEntryNode(), llvm::SelectionDAG::getExternalSymbol(), llvm::TargetLoweringBase::getLibcallCallingConv(), llvm::TargetLoweringBase::getLibcallName(), llvm::TargetLoweringBase::getPointerTy(), llvm::EVT::getTypeForEVT(), llvm::SDValue::getValueType(), llvm::TargetLowering::ArgListEntry::isSExt, llvm::TargetLowering::ArgListEntry::isZExt, LowerCallTo(), llvm::TargetLowering::ArgListEntry::Node, llvm::TargetLowering::CallLoweringInfo::setChain(), llvm::TargetLowering::CallLoweringInfo::setDebugLoc(), llvm::TargetLowering::CallLoweringInfo::setDiscardResult(), llvm::TargetLowering::CallLoweringInfo::setSExtResult(), llvm::TargetLowering::CallLoweringInfo::setZExtResult(), and llvm::TargetLowering::ArgListEntry::Ty.

Referenced by LowerUMULO_SMULO(), softenSetCCOperands(), and llvm::SelectionDAGBuilder::visitSPDescriptorFailure().

| virtual bool llvm::TargetLowering::mayBeEmittedAsTailCall | ( | CallInst * | ) | const [inline, virtual] |

Return true if the target may be able emit the call instruction as a tail call. This is used by optimization passes to determine if it's profitable to duplicate return instructions to enable tailcall optimization.

Reimplemented in llvm::SystemZTargetLowering.

Definition at line 2348 of file TargetLowering.h.

| TargetLowering::AsmOperandInfoVector TargetLowering::ParseConstraints | ( | ImmutableCallSite | CS | ) | const [virtual] |

Split up the constraint string from the inline assembly value into the specific constraints and their prefixes, and also tie in the associated operand values. If this returns an empty vector, and if the constraint string itself isn't empty, there was an error parsing.

ParseConstraints - Split up the constraint string from the inline assembly value into the specific constraints and their prefixes, and also tie in the associated operand values. If this returns an empty vector, and if the constraint string itself isn't empty, there was an error parsing.

ConstraintOperands - Information about all of the constraints.

Definition at line 2235 of file TargetLowering.cpp.

References llvm::TargetLowering::AsmOperandInfo::CallOperandVal, llvm::TargetLowering::AsmOperandInfo::ConstraintCode, llvm::TargetLowering::AsmOperandInfo::ConstraintVT, llvm::dyn_cast(), llvm::IntegerType::get(), llvm::CallSiteBase< FunTy, ValTy, UserTy, InstrTy, CallTy, InvokeTy, IterTy >::getArgument(), llvm::CallSiteBase< FunTy, ValTy, UserTy, InstrTy, CallTy, InvokeTy, IterTy >::getCalledValue(), llvm::Type::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::SequentialType::getElementType(), llvm::MVT::getIntegerVT(), getMultipleConstraintMatchWeight(), llvm::DataLayout::getPointerSizeInBits(), getRegForInlineAsmConstraint(), llvm::TargetLoweringBase::getSimpleValueType(), llvm::MVT::getSizeInBits(), llvm::CallSiteBase< FunTy, ValTy, UserTy, InstrTy, CallTy, InvokeTy, IterTy >::getType(), llvm::Value::getType(), llvm::DataLayout::getTypeSizeInBits(), llvm::MVT::getVT(), llvm::InlineAsm::ConstraintInfo::hasMatchingInput(), llvm::InlineAsm::isClobber, llvm::InlineAsm::ConstraintInfo::isIndirect, llvm::InlineAsm::isInput, llvm::MVT::isInteger(), llvm::InlineAsm::isOutput, llvm::Type::isSingleValueType(), llvm::Type::isSized(), llvm::Type::isVoidTy(), llvm::InlineAsm::ConstraintInfo::MatchingInput, llvm::InlineAsm::ConstraintInfo::multipleAlternatives, llvm::MVT::Other, llvm::InlineAsm::ParseConstraints(), llvm::report_fatal_error(), llvm::InlineAsm::ConstraintInfo::selectAlternative(), and llvm::InlineAsm::ConstraintInfo::Type.

Referenced by llvm::FunctionLoweringInfo::set().

| SDValue TargetLowering::PerformDAGCombine | ( | SDNode * | N, |

| DAGCombinerInfo & | DCI | ||

| ) | const [virtual] |

This method will be invoked for all target nodes and for any target-independent nodes that the target has registered with invoke it for.

The semantics are as follows: Return Value: SDValue.Val == 0 - No change was made SDValue.Val == N - N was replaced, is dead, and is already handled. otherwise - N should be replaced by the returned Operand.

In addition, methods provided by DAGCombinerInfo may be used to perform more complex transformations.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::MipsTargetLowering, llvm::SystemZTargetLowering, llvm::AArch64TargetLowering, llvm::AMDGPUTargetLowering, llvm::SITargetLowering, llvm::MipsSETargetLowering, and llvm::R600TargetLowering.

Definition at line 2038 of file TargetLowering.cpp.

| virtual SDValue llvm::TargetLowering::prepareVolatileOrAtomicLoad | ( | SDValue | Chain, |

| SDLoc | DL, | ||

| SelectionDAG & | DAG | ||

| ) | const [inline, virtual] |

This callback is used to prepare for a volatile or atomic load. It takes a chain node as input and returns the chain for the load itself.

Having a callback like this is necessary for targets like SystemZ, which allows a CPU to reuse the result of a previous load indefinitely, even if a cache-coherent store is performed by another CPU. The default implementation does nothing.

Reimplemented in llvm::SystemZTargetLowering.

Definition at line 2399 of file TargetLowering.h.

| virtual void llvm::TargetLowering::ReplaceNodeResults | ( | SDNode * | , |

| SmallVectorImpl< SDValue > & | , | ||

| SelectionDAG & | |||

| ) | const [inline, virtual] |

This callback is invoked when a node result type is illegal for the target, and the operation was registered to use 'custom' lowering for that result type. The target places new result values for the node in Results (their number and types must exactly match those of the original return values of the node), or leaves Results empty, which indicates that the node is not to be custom lowered after all.

If the target has no operations that require custom lowering, it need not implement this. The default implementation aborts.

Reimplemented in llvm::final< T >, llvm::PPCTargetLowering, llvm::ARMTargetLowering, llvm::MipsTargetLowering, llvm::SparcTargetLowering, llvm::AMDGPUTargetLowering, llvm::XCoreTargetLowering, and llvm::R600TargetLowering.

Definition at line 2437 of file TargetLowering.h.

References llvm_unreachable.

| bool TargetLowering::SimplifyDemandedBits | ( | SDValue | Op, |

| const APInt & | DemandedMask, | ||

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| TargetLoweringOpt & | TLO, | ||

| unsigned | Depth = 0 |

||

| ) | const |

Look at Op. At this point, we know that only the DemandedMask bits of the result of Op are ever used downstream. If we can use this information to simplify Op, create a new simplified DAG node and return true, returning the original and new nodes in Old and New. Otherwise, analyze the expression and return a mask of KnownOne and KnownZero bits for the expression (used to simplify the caller). The KnownZero/One bits may only be accurate for those bits in the DemandedMask.

SimplifyDemandedBits - Look at Op. At this point, we know that only the DemandedMask bits of the result of Op are ever used downstream. If we can use this information to simplify Op, create a new simplified DAG node and return true, returning the original and new nodes in Old and New. Otherwise, analyze the expression and return a mask of KnownOne and KnownZero bits for the expression (used to simplify the caller). The KnownZero/One bits may only be accurate for those bits in the DemandedMask.

Definition at line 373 of file TargetLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::AND, llvm::ISD::ANY_EXTEND, llvm::ISD::AssertZext, llvm::ISD::BITCAST, llvm::ISD::BUILD_PAIR, llvm::CallingConv::C, llvm::TargetLowering::TargetLoweringOpt::CombineTo(), llvm::SelectionDAG::computeKnownBits(), llvm::ISD::Constant, llvm::TargetLowering::TargetLoweringOpt::DAG, llvm::dyn_cast(), llvm::APInt::exactLogBase2(), llvm::ISD::FGETSIGN, llvm::APInt::getAllOnesValue(), llvm::APInt::getBitsSet(), llvm::APInt::getBitWidth(), llvm::SelectionDAG::getConstant(), llvm::APInt::getHiBits(), llvm::APInt::getHighBitsSet(), llvm::APInt::getLoBits(), llvm::APInt::getLowBitsSet(), llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::EVT::getScalarSizeInBits(), llvm::EVT::getScalarType(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::APInt::getSignBit(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::ConstantSDNode::getZExtValue(), llvm::SDValue::hasOneUse(), llvm::SDNode::hasOneUse(), llvm::MVT::i32, llvm::tgtok::In, llvm::APInt::intersects(), llvm::APInt::isAllOnesValue(), llvm::EVT::isFloatingPoint(), llvm::isIntN(), llvm::TargetLoweringBase::isOperationLegalOrCustom(), llvm::EVT::isSimple(), isTypeDesirableForOp(), llvm::EVT::isVector(), llvm::APInt::lshr(), llvm::ISD::MUL, llvm::ISD::OR, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::ISD::SHL, llvm::APInt::shl(), llvm::TargetLowering::TargetLoweringOpt::ShrinkDemandedConstant(), llvm::ISD::SIGN_EXTEND, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SRA, llvm::ISD::SRL, llvm::ISD::SUB, llvm::LibFunc::trunc, llvm::APInt::trunc(), llvm::ISD::TRUNCATE, llvm::ISD::UNDEF, llvm::ISD::XOR, llvm::ISD::ZERO_EXTEND, and llvm::APInt::zext().

Referenced by PerformSELECTCombine(), and simplifyI24().

| SDValue TargetLowering::SimplifySetCC | ( | EVT | VT, |

| SDValue | N0, | ||

| SDValue | N1, | ||

| ISD::CondCode | Cond, | ||

| bool | foldBooleans, | ||

| DAGCombinerInfo & | DCI, | ||

| SDLoc | dl | ||

| ) | const |

Try to simplify a setcc built with the specified operands and cc. If it is unable to simplify it, return a null SDValue.

SimplifySetCC - Try to simplify a setcc built with the specified operands and cc. If it is unable to simplify it, return a null SDValue.

Definition at line 1207 of file TargetLowering.cpp.

References llvm::ISD::ADD, llvm::TargetLowering::DAGCombinerInfo::AddToWorklist(), llvm::ISD::AND, AND, llvm::APIntOps::And(), llvm::ISD::ANY_EXTEND, llvm::ISD::AssertZext, llvm::EVT::bitsGT(), llvm::EVT::bitsLE(), llvm::EVT::bitsLT(), llvm::CallingConv::C, llvm::ISD::Constant, llvm::APInt::countTrailingZeros(), llvm::ISD::CTLZ, llvm::ISD::CTPOP, llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::SelectionDAG::FoldSetCC(), llvm::MemSDNode::getAlignment(), llvm::APInt::getAllOnesValue(), llvm::LoadSDNode::getBasePtr(), llvm::APInt::getBitWidth(), llvm::TargetLoweringBase::getBooleanContents(), llvm::SelectionDAG::getBoolExtOrTrunc(), llvm::MemSDNode::getChain(), llvm::TargetLoweringBase::getCondCodeAction(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::LoadSDNode::getExtensionType(), llvm::APInt::getHighBitsSet(), llvm::EVT::getIntegerVT(), llvm::SelectionDAG::getLoad(), llvm::APInt::getLowBitsSet(), llvm::APInt::getMaxValue(), llvm::MemSDNode::getMemoryVT(), llvm::APInt::getMinValue(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getNOT(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::MemSDNode::getPointerInfo(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getSetCC(), llvm::ISD::getSetCCInverse(), llvm::TargetLoweringBase::getSetCCResultType(), llvm::ISD::getSetCCSwappedOperands(), llvm::APInt::getSExtValue(), llvm::TargetLoweringBase::getShiftAmountTy(), llvm::APInt::getSignedMaxValue(), llvm::APInt::getSignedMinValue(), llvm::SDValue::getSimpleValueType(), llvm::EVT::getSimpleVT(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getUNDEF(), llvm::ISD::getUnorderedFlavor(), llvm::SDValue::getValueSizeInBits(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::MachinePointerInfo::getWithOffset(), llvm::SDValue::hasOneUse(), llvm::SDNode::hasOneUse(), llvm::MVT::i1, llvm::TargetLowering::DAGCombinerInfo::isBeforeLegalize(), llvm::TargetLowering::DAGCombinerInfo::isBeforeLegalizeOps(), llvm::TargetLowering::DAGCombinerInfo::isCalledByLegalizer(), llvm::SelectionDAG::isCommutativeBinOp(), llvm::TargetLoweringBase::isCondCodeLegal(), llvm::EVT::isInteger(), llvm::TargetLoweringBase::isLegalICmpImmediate(), llvm::TargetLoweringBase::isLittleEndian(), llvm::TargetLoweringBase::isOperationLegal(), llvm::EVT::isRound(), llvm::ISD::isSignedIntSetCC(), llvm::ISD::isTrueWhenEqual(), isTypeDesirableForOp(), llvm::TargetLoweringBase::isTypeLegal(), llvm::LSBaseSDNode::isUnindexed(), llvm::MemSDNode::isVolatile(), llvm::TargetLoweringBase::Legal, llvm_unreachable, llvm::Log2_32(), llvm::Log2_32_Ceil(), llvm::APInt::lshr(), llvm::SelectionDAG::MaskedValueIsZero(), llvm::MinAlign(), llvm::ISD::NON_EXTLOAD, llvm::ISD::OR, llvm::ISD::SETCC, llvm::ISD::SETEQ, llvm::ISD::SETFALSE, llvm::ISD::SETFALSE2, llvm::ISD::SETGE, llvm::ISD::SETGT, llvm::ISD::SETLE, llvm::ISD::SETLT, llvm::ISD::SETNE, llvm::ISD::SETO, llvm::ISD::SETOEQ, llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::ISD::SETOLE, llvm::ISD::SETOLT, llvm::ISD::SETONE, llvm::ISD::SETTRUE, llvm::ISD::SETTRUE2, llvm::ISD::SETUEQ, llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SETULE, llvm::ISD::SETULT, llvm::ISD::SETUNE, llvm::ISD::SETUO, llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SRL, llvm::ISD::SUB, llvm::ISD::SUBC, llvm::Trunc, llvm::ISD::TRUNCATE, llvm::TargetLoweringBase::UndefinedBooleanContent, ValueHasExactlyOneBitSet(), llvm::ISD::XOR, XOR, llvm::ISD::ZERO_EXTEND, llvm::TargetLoweringBase::ZeroOrNegativeOneBooleanContent, llvm::TargetLoweringBase::ZeroOrOneBooleanContent, and llvm::ISD::ZEXTLOAD.

Referenced by llvm::SITargetLowering::PerformDAGCombine().

| void TargetLowering::softenSetCCOperands | ( | SelectionDAG & | DAG, |

| EVT | VT, | ||

| SDValue & | NewLHS, | ||

| SDValue & | NewRHS, | ||

| ISD::CondCode & | CCCode, | ||

| SDLoc | dl | ||

| ) | const |

SoftenSetCCOperands - Soften the operands of a comparison. This code is shared among BR_CC, SELECT_CC, and SETCC handlers.

Definition at line 118 of file TargetLowering.cpp.

References llvm::MVT::f128, llvm::MVT::f32, llvm::MVT::f64, llvm::TargetLoweringBase::getCmpLibcallCC(), llvm::TargetLoweringBase::getCmpLibcallReturnType(), llvm::SelectionDAG::getCondCode(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getSetCCResultType(), llvm::SDValue::getValueType(), llvm_unreachable, makeLibCall(), llvm::RTLIB::O_F128, llvm::RTLIB::O_F32, llvm::RTLIB::O_F64, llvm::RTLIB::OEQ_F128, llvm::RTLIB::OEQ_F32, llvm::RTLIB::OEQ_F64, llvm::RTLIB::OGE_F128, llvm::RTLIB::OGE_F32, llvm::RTLIB::OGE_F64, llvm::RTLIB::OGT_F128, llvm::RTLIB::OGT_F32, llvm::RTLIB::OGT_F64, llvm::RTLIB::OLE_F128, llvm::RTLIB::OLE_F32, llvm::RTLIB::OLE_F64, llvm::RTLIB::OLT_F128, llvm::RTLIB::OLT_F32, llvm::RTLIB::OLT_F64, llvm::ISD::OR, llvm::ISD::SETCC, llvm::ISD::SETEQ, llvm::ISD::SETGE, llvm::ISD::SETGT, llvm::ISD::SETLE, llvm::ISD::SETLT, llvm::ISD::SETNE, llvm::ISD::SETO, llvm::ISD::SETOEQ, llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::ISD::SETOLE, llvm::ISD::SETOLT, llvm::ISD::SETONE, llvm::ISD::SETUEQ, llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SETULE, llvm::ISD::SETULT, llvm::ISD::SETUNE, llvm::ISD::SETUO, llvm::RTLIB::UNE_F128, llvm::RTLIB::UNE_F32, llvm::RTLIB::UNE_F64, llvm::RTLIB::UNKNOWN_LIBCALL, llvm::RTLIB::UO_F128, llvm::RTLIB::UO_F32, and llvm::RTLIB::UO_F64.

| virtual bool llvm::TargetLowering::useLoadStackGuardNode | ( | ) | const [inline, virtual] |

If this function returns true, SelectionDAGBuilder emits a LOAD_STACK_GUARD node when it is lowering Intrinsic::stackprotector.

Reimplemented in llvm::final< T >, llvm::ARMTargetLowering, and llvm::AArch64TargetLowering.

Definition at line 2644 of file TargetLowering.h.

Referenced by llvm::SelectionDAGBuilder::visitSPDescriptorParent().

| bool TargetLowering::verifyReturnAddressArgumentIsConstant | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 2770 of file TargetLowering.cpp.

References llvm::LLVMContext::emitError(), llvm::SelectionDAG::getContext(), and llvm::SDValue::getOperand().

Referenced by llvm::MSP430TargetLowering::LowerRETURNADDR(), llvm::HexagonTargetLowering::LowerRETURNADDR(), and LowerRETURNADDR().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1