#include <ScheduleDAGSDNodes.h>

Detailed Description

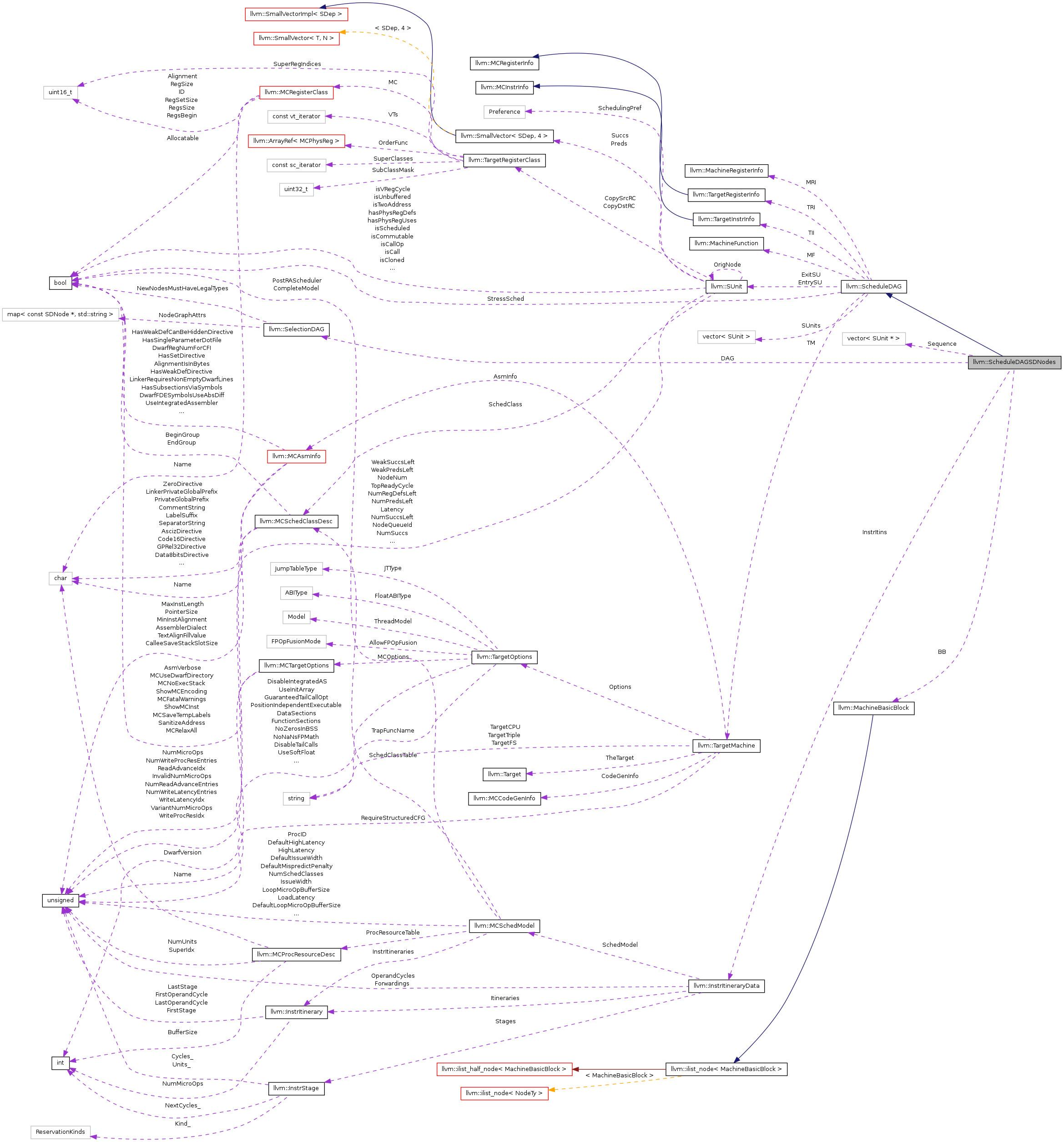

ScheduleDAGSDNodes - A ScheduleDAG for scheduling SDNode-based DAGs.

Edges between SUnits are initially based on edges in the SelectionDAG, and additional edges can be added by the schedulers as heuristics. SDNodes such as Constants, Registers, and a few others that are not interesting to schedulers are not allocated SUnits.

SDNodes with MVT::Glue operands are grouped along with the flagged nodes into a single SUnit so that they are scheduled together.

SDNode-based scheduling graphs do not use SDep::Anti or SDep::Output edges. Physical register dependence information is not carried in the DAG and must be handled explicitly by schedulers.

Definition at line 36 of file ScheduleDAGSDNodes.h.

Constructor & Destructor Documentation

| ScheduleDAGSDNodes::ScheduleDAGSDNodes | ( | MachineFunction & | mf | ) | [explicit] |

Definition at line 49 of file ScheduleDAGSDNodes.cpp.

| virtual llvm::ScheduleDAGSDNodes::~ScheduleDAGSDNodes | ( | ) | [inline, virtual] |

Definition at line 47 of file ScheduleDAGSDNodes.h.

Member Function Documentation

| void ScheduleDAGSDNodes::BuildSchedGraph | ( | AliasAnalysis * | AA | ) |

BuildSchedGraph - Build the SUnit graph from the selection dag that we are input. This SUnit graph is similar to the SelectionDAG, but excludes nodes that aren't interesting to scheduling, and represents flagged together nodes with a single SUnit.

BuildSchedGraph - Build the SUnit graph from the selection dag that we are input. This SUnit graph is similar to the SelectionDAG, but excludes nodes that aren't interesting to scheduling, and represents glued together nodes with a single SUnit.

Definition at line 522 of file ScheduleDAGSDNodes.cpp.

| SUnit * ScheduleDAGSDNodes::Clone | ( | SUnit * | N | ) |

Clone - Creates a clone of the specified SUnit. It does not copy the predecessors / successors info nor the temporary scheduling states.

Definition at line 90 of file ScheduleDAGSDNodes.cpp.

References llvm::SUnit::getNode(), llvm::SUnit::hasPhysRegClobbers, llvm::SUnit::hasPhysRegDefs, llvm::SUnit::isCall, llvm::SUnit::isCallOp, llvm::SUnit::isCloned, llvm::SUnit::isCommutable, llvm::SUnit::isScheduleHigh, llvm::SUnit::isScheduleLow, llvm::SUnit::isTwoAddress, llvm::SUnit::isVRegCycle, llvm::SUnit::Latency, newSUnit(), llvm::SUnit::OrigNode, and llvm::SUnit::SchedulingPref.

| void ScheduleDAGSDNodes::computeLatency | ( | SUnit * | SU | ) | [virtual] |

computeLatency - Compute node latency.

Definition at line 591 of file ScheduleDAGSDNodes.cpp.

References forceUnitLatencies(), llvm::SDNode::getGluedNode(), llvm::TargetInstrInfo::getInstrLatency(), llvm::SDNode::getMachineOpcode(), llvm::SUnit::getNode(), llvm::SDNode::getOpcode(), HighLatencyCycles, InstrItins, llvm::InstrItineraryData::isEmpty(), llvm::TargetInstrInfo::isHighLatencyDef(), llvm::SDNode::isMachineOpcode(), llvm::SUnit::Latency, llvm::ScheduleDAG::TII, and llvm::ISD::TokenFactor.

| void ScheduleDAGSDNodes::computeOperandLatency | ( | SDNode * | Def, |

| SDNode * | Use, | ||

| unsigned | OpIdx, | ||

| SDep & | dep | ||

| ) | const [virtual] |

Definition at line 625 of file ScheduleDAGSDNodes.cpp.

References BB, llvm::ISD::CopyToReg, llvm::SDep::Data, forceUnitLatencies(), llvm::MCInstrInfo::get(), llvm::SDep::getKind(), llvm::SDNode::getMachineOpcode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::TargetInstrInfo::getOperandLatency(), getReg(), llvm::SDValue::getResNo(), InstrItins, llvm::SDNode::isMachineOpcode(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::SDep::setLatency(), llvm::MachineBasicBlock::succ_empty(), and llvm::ScheduleDAG::TII.

| void ScheduleDAGSDNodes::dumpNode | ( | const SUnit * | SU | ) | const [override, virtual] |

Implements llvm::ScheduleDAG.

Definition at line 652 of file ScheduleDAGSDNodes.cpp.

References llvm::SmallVectorTemplateCommon< T >::back(), llvm::dbgs(), llvm::SDNode::dump(), llvm::SmallVectorBase::empty(), llvm::SDNode::getGluedNode(), llvm::SUnit::getNode(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::pop_back(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

| void ScheduleDAGSDNodes::dumpSchedule | ( | ) | const |

Definition at line 674 of file ScheduleDAGSDNodes.cpp.

References llvm::dbgs(), and llvm::SUnit::dump().

| MachineBasicBlock * ScheduleDAGSDNodes::EmitSchedule | ( | MachineBasicBlock::iterator & | InsertPos | ) | [virtual] |

EmitSchedule - Insert MachineInstrs into the MachineBasicBlock according to the order specified in Sequence.

EmitSchedule - Emit the machine code in scheduled order. Return the new InsertPos and MachineBasicBlock that contains this insertion point. ScheduleDAGSDNodes holds a BB pointer for convenience, but this does not necessarily refer to returned BB. The emitter may split blocks.

Definition at line 798 of file ScheduleDAGSDNodes.cpp.

References llvm::SmallVectorTemplateCommon< T >::back(), BB, llvm::SmallVectorTemplateCommon< T >::begin(), llvm::SmallVectorTemplateCommon< T, typename >::begin(), llvm::MachineFunction::begin(), llvm::SelectionDAG::ByvalParmDbgBegin(), llvm::SelectionDAG::ByvalParmDbgEnd(), DAG, llvm::SelectionDAG::DbgBegin(), llvm::SelectionDAG::DbgEnd(), llvm::InstrEmitter::EmitDbgValue(), llvm::InstrEmitter::EmitNode(), llvm::SmallVectorBase::empty(), llvm::SmallVectorTemplateCommon< T, typename >::end(), llvm::SmallVectorTemplateCommon< T >::end(), llvm::InstrEmitter::getBlock(), llvm::MachineBasicBlock::getFirstNonPHI(), llvm::MachineBasicBlock::getFirstTerminator(), llvm::SDNode::getGluedNode(), llvm::InstrEmitter::getInsertPos(), llvm::SUnit::getNode(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::SelectionDAG::hasDebugValues(), llvm::MachineBasicBlock::insert(), llvm::TargetInstrInfo::insertNoop(), llvm::SUnit::isCloned, llvm::AArch64CC::MI, llvm::SUnit::OrigNode, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::pop_back(), ProcessSourceNode(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SmallVectorTemplateCommon< T >::size(), and llvm::ScheduleDAG::TII.

| virtual bool llvm::ScheduleDAGSDNodes::forceUnitLatencies | ( | ) | const [inline, protected, virtual] |

ForceUnitLatencies - Return true if all scheduling edges should be given a latency value of one. The default is to return false; schedulers may override this as needed.

Definition at line 166 of file ScheduleDAGSDNodes.h.

Referenced by computeLatency(), and computeOperandLatency().

| void ScheduleDAGSDNodes::getCustomGraphFeatures | ( | GraphWriter< ScheduleDAG * > & | GW | ) | const [virtual] |

Definition at line 291 of file SelectionDAGPrinter.cpp.

References DAG, llvm::GraphWriter< GraphType >::emitEdge(), llvm::GraphWriter< GraphType >::emitSimpleNode(), llvm::SDValue::getNode(), llvm::SDNode::getNodeId(), llvm::SelectionDAG::getRoot(), and llvm::ScheduleDAG::SUnits.

| std::string ScheduleDAGSDNodes::getDAGName | ( | ) | const [override, virtual] |

Return the basic block label.

Implements llvm::ScheduleDAG.

Definition at line 911 of file ScheduleDAGSDNodes.cpp.

References BB, and llvm::MachineBasicBlock::getFullName().

| std::string ScheduleDAGSDNodes::getGraphNodeLabel | ( | const SUnit * | SU | ) | const [override, virtual] |

getGraphNodeLabel - Return a label for an SUnit node in a visualization of the ScheduleDAG.

Implements llvm::ScheduleDAG.

Definition at line 270 of file SelectionDAGPrinter.cpp.

References llvm::SmallVectorTemplateCommon< T >::back(), DAG, llvm::SmallVectorBase::empty(), llvm::SDNode::getGluedNode(), llvm::SUnit::getNode(), llvm::SUnit::NodeNum, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::pop_back(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), and llvm::raw_string_ostream::str().

| void ScheduleDAGSDNodes::InitNumRegDefsLeft | ( | SUnit * | SU | ) |

InitNumRegDefsLeft - Determine the # of regs defined by this node.

Definition at line 583 of file ScheduleDAGSDNodes.cpp.

References I, and llvm::SUnit::NumRegDefsLeft.

| void llvm::ScheduleDAGSDNodes::InitVRegCycleFlag | ( | SUnit * | SU | ) |

InitVRegCycleFlag - Set isVRegCycle if this node's single use is CopyToReg and its only active data operands are CopyFromReg within a single block loop.

| static bool llvm::ScheduleDAGSDNodes::isPassiveNode | ( | SDNode * | Node | ) | [inline, static] |

isPassiveNode - Return true if the node is a non-scheduled leaf.

Definition at line 55 of file ScheduleDAGSDNodes.h.

References llvm::ISD::EntryToken, llvm::SDNode::getOpcode(), and Node.

| SUnit * ScheduleDAGSDNodes::newSUnit | ( | SDNode * | N | ) |

NewSUnit - Creates a new SUnit and return a ptr to it.

Definition at line 69 of file ScheduleDAGSDNodes.cpp.

References DAG, llvm::SDNode::getMachineOpcode(), llvm::TargetLoweringBase::getSchedulingPreference(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::TargetOpcode::IMPLICIT_DEF, llvm::SDNode::isMachineOpcode(), llvm::None, llvm::SUnit::SchedulingPref, and llvm::ScheduleDAG::SUnits.

Referenced by Clone().

| void ScheduleDAGSDNodes::Run | ( | SelectionDAG * | dag, |

| MachineBasicBlock * | bb | ||

| ) |

Run - perform scheduling.

Definition at line 55 of file ScheduleDAGSDNodes.cpp.

References BB, llvm::ScheduleDAG::clearDAG(), DAG, and Schedule().

| virtual void llvm::ScheduleDAGSDNodes::Schedule | ( | ) | [pure virtual] |

Schedule - Order nodes according to selected style, filling in the Sequence member.

Referenced by Run().

| void ScheduleDAGSDNodes::VerifyScheduledSequence | ( | bool | isBottomUp | ) |

VerifyScheduledSequence - Verify that all SUnits are scheduled and consistent with the Sequence of scheduled instructions.

VerifyScheduledSequence - Verify that all SUnits were scheduled and that their state is consistent with the nodes listed in Sequence.

Definition at line 688 of file ScheduleDAGSDNodes.cpp.

References llvm::ScheduleDAG::VerifyScheduledDAG().

Member Data Documentation

Definition at line 38 of file ScheduleDAGSDNodes.h.

Referenced by computeOperandLatency(), EmitSchedule(), getDAGName(), ProcessSDDbgValues(), ProcessSourceNode(), and Run().

Definition at line 39 of file ScheduleDAGSDNodes.h.

Referenced by EmitSchedule(), getCustomGraphFeatures(), getGraphNodeLabel(), newSUnit(), and Run().

Definition at line 40 of file ScheduleDAGSDNodes.h.

Referenced by computeLatency(), and computeOperandLatency().

| std::vector<SUnit*> llvm::ScheduleDAGSDNodes::Sequence |

The schedule. Null SUnit*'s represent noop instructions.

Definition at line 43 of file ScheduleDAGSDNodes.h.

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1