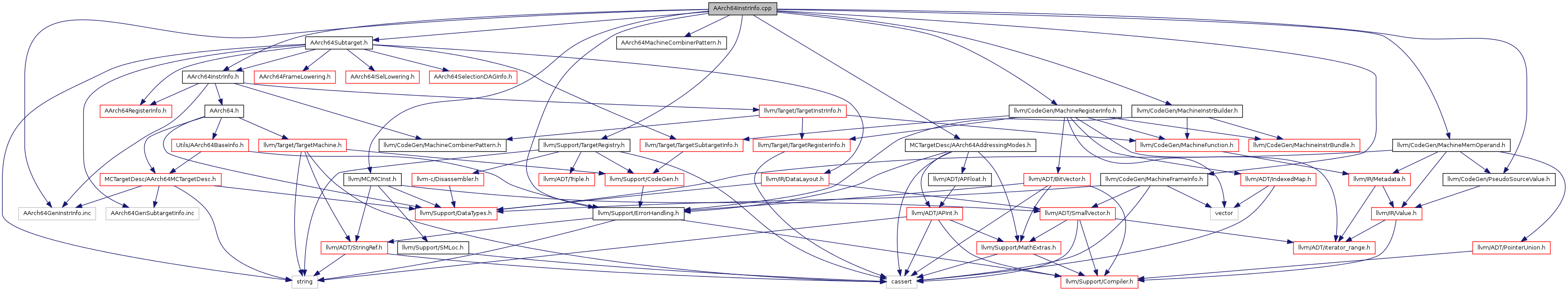

#include "AArch64InstrInfo.h"#include "AArch64Subtarget.h"#include "MCTargetDesc/AArch64AddressingModes.h"#include "AArch64MachineCombinerPattern.h"#include "llvm/CodeGen/MachineFrameInfo.h"#include "llvm/CodeGen/MachineInstrBuilder.h"#include "llvm/CodeGen/MachineMemOperand.h"#include "llvm/CodeGen/MachineRegisterInfo.h"#include "llvm/CodeGen/PseudoSourceValue.h"#include "llvm/MC/MCInst.h"#include "llvm/Support/ErrorHandling.h"#include "llvm/Support/TargetRegistry.h"#include "AArch64GenInstrInfo.inc"

Go to the source code of this file.

Define Documentation

| #define GET_INSTRINFO_CTOR_DTOR |

Definition at line 29 of file AArch64InstrInfo.cpp.

Function Documentation

| static const MachineInstrBuilder& AddSubReg | ( | const MachineInstrBuilder & | MIB, |

| unsigned | Reg, | ||

| unsigned | SubIdx, | ||

| unsigned | State, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | [static] |

Definition at line 1460 of file AArch64InstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::MCRegisterInfo::getSubReg(), and llvm::TargetRegisterInfo::isPhysicalRegister().

Referenced by llvm::AArch64InstrInfo::copyPhysRegTuple().

| static bool canCombineWithMUL | ( | MachineBasicBlock & | MBB, |

| MachineOperand & | MO, | ||

| unsigned | MulOpc, | ||

| unsigned | ZeroReg | ||

| ) | [static] |

Definition at line 2408 of file AArch64InstrInfo.cpp.

References llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::MachineRegisterInfo::getUniqueVRegDef(), llvm::MachineRegisterInfo::hasOneNonDBGUse(), llvm::MachineOperand::isReg(), llvm::TargetRegisterInfo::isVirtualRegister(), and llvm::AArch64CC::MI.

Referenced by llvm::AArch64InstrInfo::hasPattern().

| static unsigned canFoldIntoCSel | ( | const MachineRegisterInfo & | MRI, |

| unsigned | VReg, | ||

| unsigned * | NewVReg = nullptr |

||

| ) | [static] |

Definition at line 306 of file AArch64InstrInfo.cpp.

References llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineRegisterInfo::getVRegDef(), llvm::MachineOperand::isImm(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::AArch64SysReg::NZCV, and removeCopies().

Referenced by llvm::AArch64InstrInfo::canInsertSelect(), and llvm::AArch64InstrInfo::insertSelect().

| static unsigned convertFlagSettingOpcode | ( | MachineInstr * | MI | ) | [static] |

convertFlagSettingOpcode - return opcode that does not set flags when possible. The caller is responsible to do the actual substitution and legality checking.

Definition at line 746 of file AArch64InstrInfo.cpp.

References llvm::MachineInstr::getOpcode().

Referenced by llvm::AArch64InstrInfo::hasPattern(), and llvm::AArch64InstrInfo::optimizeCompareInstr().

| static bool forwardCopyWillClobberTuple | ( | unsigned | DestReg, |

| unsigned | SrcReg, | ||

| unsigned | NumRegs | ||

| ) | [static] |

Definition at line 1472 of file AArch64InstrInfo.cpp.

Referenced by llvm::AArch64InstrInfo::copyPhysRegTuple().

| static MachineInstr* genMadd | ( | MachineFunction & | MF, |

| MachineRegisterInfo & | MRI, | ||

| const TargetInstrInfo * | TII, | ||

| MachineInstr & | Root, | ||

| SmallVectorImpl< MachineInstr * > & | InsInstrs, | ||

| unsigned | IdxMulOpd, | ||

| unsigned | MaddOpc, | ||

| const TargetRegisterClass * | RC | ||

| ) | [static] |

genMadd - Generate madd instruction and combine mul and add. Example: MUL I=A,B,0 ADD R,I,C ==> MADD R,A,B,C

- Parameters:

-

Root is the ADD instruction [out] InsInstrs is a vector of machine instructions and will contain the generated madd instruction IdxMulOpd is index of operand in Root that is the result of the MUL. In the example above IdxMulOpd is 1. MaddOpc the opcode fo the madd instruction

Definition at line 2558 of file AArch64InstrInfo.cpp.

References llvm::BuildMI(), llvm::MachineRegisterInfo::constrainRegClass(), llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::getKillRegState(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getUniqueVRegDef(), llvm::MachineOperand::isKill(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::ISD::MUL, and llvm::SmallVectorTemplateBase< T, isPodLike >::push_back().

Referenced by llvm::AArch64InstrInfo::genAlternativeCodeSequence().

| static MachineInstr* genMaddR | ( | MachineFunction & | MF, |

| MachineRegisterInfo & | MRI, | ||

| const TargetInstrInfo * | TII, | ||

| MachineInstr & | Root, | ||

| SmallVectorImpl< MachineInstr * > & | InsInstrs, | ||

| unsigned | IdxMulOpd, | ||

| unsigned | MaddOpc, | ||

| unsigned | VR, | ||

| const TargetRegisterClass * | RC | ||

| ) | [static] |

genMaddR - Generate madd instruction and combine mul and add using an extra virtual register Example - an ADD intermediate needs to be stored in a register: MUL I=A,B,0 ADD R,I,Imm ==> ORR V, ZR, Imm ==> MADD R,A,B,V

- Parameters:

-

Root is the ADD instruction [out] InsInstrs is a vector of machine instructions and will contain the generated madd instruction IdxMulOpd is index of operand in Root that is the result of the MUL. In the example above IdxMulOpd is 1. MaddOpc the opcode fo the madd instruction VR is a virtual register that holds the value of an ADD operand (V in the example above).

Definition at line 2609 of file AArch64InstrInfo.cpp.

References llvm::BuildMI(), llvm::MachineRegisterInfo::constrainRegClass(), llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::getKillRegState(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getUniqueVRegDef(), llvm::MachineOperand::isKill(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::ISD::MUL, and llvm::SmallVectorTemplateBase< T, isPodLike >::push_back().

Referenced by llvm::AArch64InstrInfo::genAlternativeCodeSequence().

| static bool isCombineInstrCandidate | ( | unsigned | Opc | ) | [static] |

Definition at line 2404 of file AArch64InstrInfo.cpp.

References isCombineInstrCandidate32(), and isCombineInstrCandidate64().

Referenced by llvm::AArch64InstrInfo::hasPattern().

| static bool isCombineInstrCandidate32 | ( | unsigned | Opc | ) | [static] |

Definition at line 2366 of file AArch64InstrInfo.cpp.

Referenced by isCombineInstrCandidate().

| static bool isCombineInstrCandidate64 | ( | unsigned | Opc | ) | [static] |

Definition at line 2385 of file AArch64InstrInfo.cpp.

Referenced by isCombineInstrCandidate().

| static bool isCombineInstrSettingFlag | ( | unsigned | Opc | ) | [static] |

Definition at line 2347 of file AArch64InstrInfo.cpp.

Referenced by llvm::AArch64InstrInfo::hasPattern().

| static void parseCondBranch | ( | MachineInstr * | LastInst, |

| MachineBasicBlock *& | Target, | ||

| SmallVectorImpl< MachineOperand > & | Cond | ||

| ) | [static] |

Definition at line 61 of file AArch64InstrInfo.cpp.

References llvm::MachineOperand::CreateImm(), llvm::MachineOperand::getMBB(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm_unreachable, and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

Referenced by llvm::AArch64InstrInfo::AnalyzeBranch().

| static unsigned removeCopies | ( | const MachineRegisterInfo & | MRI, |

| unsigned | VReg | ||

| ) | [static] |

Definition at line 293 of file AArch64InstrInfo.cpp.

References llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getVRegDef(), llvm::MachineInstr::isFullCopy(), and llvm::TargetRegisterInfo::isVirtualRegister().

Referenced by canFoldIntoCSel().

| static bool UpdateOperandRegClass | ( | MachineInstr * | Instr | ) | [static] |

Definition at line 704 of file AArch64InstrInfo.cpp.

References llvm::MachineRegisterInfo::constrainRegClass(), llvm::TargetRegisterClass::contains(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineInstr::getRegClassConstraint(), llvm::MachineFunction::getRegInfo(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::MachineFunction::getTarget(), llvm::TargetRegisterClass::hasSubClassEq(), llvm::MachineOperand::isFI(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineOperand::isReg(), TII, and llvm::SystemZISD::TM.

Referenced by llvm::AArch64InstrInfo::optimizeCompareInstr().

1.7.6.1

1.7.6.1