#include <AMDGPUInstrInfo.h>

Detailed Description

Definition at line 40 of file AMDGPUInstrInfo.h.

Constructor & Destructor Documentation

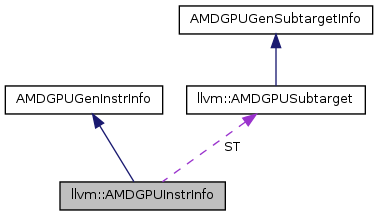

| AMDGPUInstrInfo::AMDGPUInstrInfo | ( | const AMDGPUSubtarget & | st | ) | [explicit] |

Definition at line 33 of file AMDGPUInstrInfo.cpp.

Member Function Documentation

| virtual MachineInstrBuilder llvm::AMDGPUInstrInfo::buildIndirectRead | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | ValueReg, | ||

| unsigned | Address, | ||

| unsigned | OffsetReg | ||

| ) | const [pure virtual] |

Build instruction(s) for an indirect register read.

- Returns:

- The instruction that performs the indirect register read

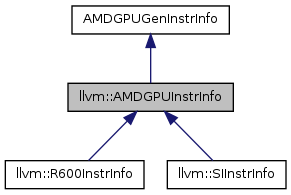

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

| virtual MachineInstrBuilder llvm::AMDGPUInstrInfo::buildIndirectWrite | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | ValueReg, | ||

| unsigned | Address, | ||

| unsigned | OffsetReg | ||

| ) | const [pure virtual] |

Build instruction(s) for an indirect register write.

- Returns:

- The instruction that performs the indirect register write

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

| virtual MachineInstr* llvm::AMDGPUInstrInfo::buildMovInstr | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | DstReg, | ||

| unsigned | SrcReg | ||

| ) | const [pure virtual] |

Build a MOV instruction.

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

| virtual unsigned llvm::AMDGPUInstrInfo::calculateIndirectAddress | ( | unsigned | RegIndex, |

| unsigned | Channel | ||

| ) | const [pure virtual] |

Calculate the "Indirect Address" for the given RegIndex and Channel.

We model indirect addressing using a virtual address space that can be accesed with loads and stores. The "Indirect Address" is the memory address in this virtual address space that maps to the given RegIndex and Channel.

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo().

| bool AMDGPUInstrInfo::canFoldMemoryOperand | ( | const MachineInstr * | MI, |

| const SmallVectorImpl< unsigned > & | Ops | ||

| ) | const [override] |

Definition at line 188 of file AMDGPUInstrInfo.cpp.

| MachineInstr * AMDGPUInstrInfo::convertToThreeAddress | ( | MachineFunction::iterator & | MFI, |

| MachineBasicBlock::iterator & | MBBI, | ||

| LiveVariables * | LV | ||

| ) | const [override] |

Definition at line 83 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::DefinesPredicate | ( | MachineInstr * | MI, |

| std::vector< MachineOperand > & | Pred | ||

| ) | const [override] |

Reimplemented in llvm::R600InstrInfo.

Definition at line 266 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::enableClusterLoads | ( | ) | const [override] |

Definition at line 217 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::expandPostRAPseudo | ( | MachineBasicBlock::iterator | MI | ) | const [override] |

Reimplemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Definition at line 124 of file AMDGPUInstrInfo.cpp.

References buildIndirectRead(), buildIndirectWrite(), buildMovInstr(), calculateIndirectAddress(), llvm::MachineBasicBlock::erase(), getIndirectAddrRegClass(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineBasicBlock::getParent(), llvm::TargetRegisterClass::getRegister(), isRegisterLoad(), and isRegisterStore().

| MachineInstr * AMDGPUInstrInfo::foldMemoryOperandImpl | ( | MachineFunction & | MF, |

| MachineInstr * | MI, | ||

| const SmallVectorImpl< unsigned > & | Ops, | ||

| int | FrameIndex | ||

| ) | const [override, protected] |

Definition at line 172 of file AMDGPUInstrInfo.cpp.

| MachineInstr * AMDGPUInstrInfo::foldMemoryOperandImpl | ( | MachineFunction & | MF, |

| MachineInstr * | MI, | ||

| const SmallVectorImpl< unsigned > & | Ops, | ||

| MachineInstr * | LoadMI | ||

| ) | const [override, protected] |

Definition at line 180 of file AMDGPUInstrInfo.cpp.

| virtual const TargetRegisterClass* llvm::AMDGPUInstrInfo::getIndirectAddrRegClass | ( | ) | const [pure virtual] |

- Returns:

- The register class to be used for loading and storing values from an "Indirect Address" .

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Referenced by expandPostRAPseudo(), and getIndirectIndexBegin().

| int AMDGPUInstrInfo::getIndirectIndexBegin | ( | const MachineFunction & | MF | ) | const |

- Returns:

- the smallest register index that will be accessed by an indirect read or write or -1 if indirect addressing is not used by this program.

Definition at line 291 of file AMDGPUInstrInfo.cpp.

References llvm::TargetRegisterClass::contains(), llvm::MachineFunction::getFrameInfo(), getIndirectAddrRegClass(), llvm::MachineFrameInfo::getNumObjects(), llvm::TargetRegisterClass::getNumRegs(), llvm::MachineFunction::getRegInfo(), llvm::TargetRegisterClass::getRegister(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::AArch64CC::LE, LI, llvm::MachineRegisterInfo::livein_begin(), llvm::MachineRegisterInfo::livein_empty(), and llvm::MachineRegisterInfo::livein_end().

Referenced by llvm::SIInstrInfo::buildIndirectRead(), llvm::SIInstrInfo::buildIndirectWrite(), getIndirectIndexEnd(), llvm::SIInstrInfo::reserveIndirectRegisters(), and llvm::R600InstrInfo::reserveIndirectRegisters().

| int AMDGPUInstrInfo::getIndirectIndexEnd | ( | const MachineFunction & | MF | ) | const |

- Returns:

- the largest register index that will be accessed by an indirect read or write or -1 if indirect addressing is not used by this program.

Definition at line 326 of file AMDGPUInstrInfo.cpp.

References llvm::TargetFrameLowering::getFrameIndexOffset(), llvm::MachineFunction::getFrameInfo(), llvm::TargetSubtargetInfo::getFrameLowering(), getIndirectIndexBegin(), llvm::MachineFrameInfo::getNumObjects(), llvm::TargetMachine::getSubtargetImpl(), llvm::MachineFunction::getTarget(), and llvm::MachineFrameInfo::hasVarSizedObjects().

Referenced by llvm::SIInstrInfo::reserveIndirectRegisters(), and llvm::R600InstrInfo::reserveIndirectRegisters().

| int AMDGPUInstrInfo::getMaskedMIMGOp | ( | uint16_t | Opcode, |

| unsigned | Channels | ||

| ) | const |

Given a MIMG Opcode that writes all 4 channels, return the equivalent opcode that writes Channels Channels.

Definition at line 345 of file AMDGPUInstrInfo.cpp.

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection().

| unsigned AMDGPUInstrInfo::getOpcodeAfterMemoryUnfold | ( | unsigned | Opc, |

| bool | UnfoldLoad, | ||

| bool | UnfoldStore, | ||

| unsigned * | LoadRegIndex = nullptr |

||

| ) | const [override] |

Definition at line 210 of file AMDGPUInstrInfo.cpp.

| const AMDGPURegisterInfo & AMDGPUInstrInfo::getRegisterInfo | ( | ) | const [pure virtual] |

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

Definition at line 36 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::hasLoadFromStackSlot | ( | const MachineInstr * | MI, |

| const MachineMemOperand *& | MMO, | ||

| int & | FrameIndex | ||

| ) | const [override] |

Definition at line 59 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::hasStoreFromStackSlot | ( | const MachineInstr * | MI, |

| const MachineMemOperand *& | MMO, | ||

| int & | FrameIndex | ||

| ) | const |

Definition at line 75 of file AMDGPUInstrInfo.cpp.

| void AMDGPUInstrInfo::insertNoop | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI | ||

| ) | const [override] |

Definition at line 249 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::isCoalescableExtInstr | ( | const MachineInstr & | MI, |

| unsigned & | SrcReg, | ||

| unsigned & | DstReg, | ||

| unsigned & | SubIdx | ||

| ) | const [override] |

Definition at line 40 of file AMDGPUInstrInfo.cpp.

| unsigned AMDGPUInstrInfo::isLoadFromStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

Definition at line 47 of file AMDGPUInstrInfo.cpp.

| unsigned AMDGPUInstrInfo::isLoadFromStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

Definition at line 53 of file AMDGPUInstrInfo.cpp.

| virtual bool llvm::AMDGPUInstrInfo::isMov | ( | unsigned | opcode | ) | const [pure virtual] |

Implemented in llvm::R600InstrInfo, and llvm::SIInstrInfo.

| bool AMDGPUInstrInfo::isPredicable | ( | MachineInstr * | MI | ) | const [override] |

Reimplemented in llvm::R600InstrInfo.

Definition at line 272 of file AMDGPUInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), and llvm::MCInstrDesc::isPredicable().

| bool AMDGPUInstrInfo::isPredicated | ( | const MachineInstr * | MI | ) | const [override] |

Reimplemented in llvm::R600InstrInfo.

Definition at line 254 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::isRegisterLoad | ( | const MachineInstr & | MI | ) | const |

Definition at line 287 of file AMDGPUInstrInfo.cpp.

References AMDGPU_FLAG_REGISTER_LOAD, and llvm::MachineInstr::getOpcode().

Referenced by expandPostRAPseudo().

| bool AMDGPUInstrInfo::isRegisterStore | ( | const MachineInstr & | MI | ) | const |

Definition at line 283 of file AMDGPUInstrInfo.cpp.

References AMDGPU_FLAG_REGISTER_STORE, and llvm::MachineInstr::getOpcode().

Referenced by expandPostRAPseudo().

| bool AMDGPUInstrInfo::isSafeToMoveRegClassDefs | ( | const TargetRegisterClass * | RC | ) | const [override] |

Reimplemented in llvm::SIInstrInfo.

Definition at line 278 of file AMDGPUInstrInfo.cpp.

| unsigned AMDGPUInstrInfo::isStoreFromStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 65 of file AMDGPUInstrInfo.cpp.

| unsigned AMDGPUInstrInfo::isStoreFromStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const |

Definition at line 70 of file AMDGPUInstrInfo.cpp.

| void AMDGPUInstrInfo::loadRegFromStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | DestReg, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Reimplemented in llvm::SIInstrInfo.

Definition at line 116 of file AMDGPUInstrInfo.cpp.

References llvm_unreachable.

| bool AMDGPUInstrInfo::ReverseBranchCondition | ( | SmallVectorImpl< MachineOperand > & | Cond | ) | const [override] |

Reimplemented in llvm::R600InstrInfo.

Definition at line 244 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::shouldScheduleLoadsNear | ( | SDNode * | Load1, |

| SDNode * | Load2, | ||

| int64_t | Offset1, | ||

| int64_t | Offset2, | ||

| unsigned | NumLoads | ||

| ) | const [override] |

Definition at line 231 of file AMDGPUInstrInfo.cpp.

| void AMDGPUInstrInfo::storeRegToStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | SrcReg, | ||

| bool | isKill, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Reimplemented in llvm::SIInstrInfo.

Definition at line 106 of file AMDGPUInstrInfo.cpp.

References llvm_unreachable.

| bool AMDGPUInstrInfo::SubsumesPredicate | ( | const SmallVectorImpl< MachineOperand > & | Pred1, |

| const SmallVectorImpl< MachineOperand > & | Pred2 | ||

| ) | const [override] |

Reimplemented in llvm::R600InstrInfo.

Definition at line 259 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::unfoldMemoryOperand | ( | MachineFunction & | MF, |

| MachineInstr * | MI, | ||

| unsigned | Reg, | ||

| bool | UnfoldLoad, | ||

| bool | UnfoldStore, | ||

| SmallVectorImpl< MachineInstr * > & | NewMIs | ||

| ) | const [override] |

Definition at line 194 of file AMDGPUInstrInfo.cpp.

| bool AMDGPUInstrInfo::unfoldMemoryOperand | ( | SelectionDAG & | DAG, |

| SDNode * | N, | ||

| SmallVectorImpl< SDNode * > & | NewNodes | ||

| ) | const [override] |

Definition at line 203 of file AMDGPUInstrInfo.cpp.

Member Data Documentation

const AMDGPUSubtarget& llvm::AMDGPUInstrInfo::ST [protected] |

Definition at line 47 of file AMDGPUInstrInfo.h.

Referenced by llvm::R600InstrInfo::buildSlotOfVectorInstruction(), llvm::R600InstrInfo::isTransOnly(), llvm::R600InstrInfo::usesTextureCache(), and llvm::R600InstrInfo::usesVertexCache().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1