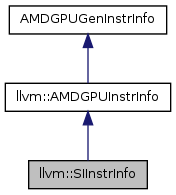

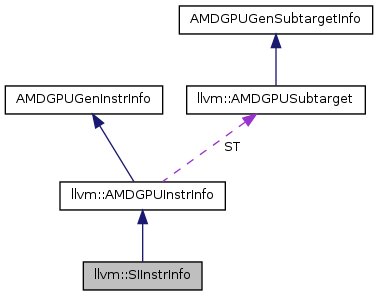

#include <SIInstrInfo.h>

Public Member Functions | |

| SIInstrInfo (const AMDGPUSubtarget &st) | |

| const SIRegisterInfo & | getRegisterInfo () const override |

| bool | areLoadsFromSameBasePtr (SDNode *Load1, SDNode *Load2, int64_t &Offset1, int64_t &Offset2) const override |

| bool | getLdStBaseRegImmOfs (MachineInstr *LdSt, unsigned &BaseReg, unsigned &Offset, const TargetRegisterInfo *TRI) const final |

| bool | shouldClusterLoads (MachineInstr *FirstLdSt, MachineInstr *SecondLdSt, unsigned NumLoads) const final |

| void | copyPhysReg (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, DebugLoc DL, unsigned DestReg, unsigned SrcReg, bool KillSrc) const override |

| void | storeRegToStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned SrcReg, bool isKill, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const override |

| void | loadRegFromStackSlot (MachineBasicBlock &MBB, MachineBasicBlock::iterator MI, unsigned DestReg, int FrameIndex, const TargetRegisterClass *RC, const TargetRegisterInfo *TRI) const override |

| bool | expandPostRAPseudo (MachineBasicBlock::iterator MI) const override |

| unsigned | commuteOpcode (unsigned Opcode) const |

| MachineInstr * | commuteInstruction (MachineInstr *MI, bool NewMI=false) const override |

| bool | isTriviallyReMaterializable (const MachineInstr *MI, AliasAnalysis *AA=nullptr) const |

| MachineInstr * | buildMovInstr (MachineBasicBlock *MBB, MachineBasicBlock::iterator I, unsigned DstReg, unsigned SrcReg) const override |

| Build a MOV instruction. | |

| bool | isMov (unsigned Opcode) const override |

| bool | isSafeToMoveRegClassDefs (const TargetRegisterClass *RC) const override |

| bool | isDS (uint16_t Opcode) const |

| bool | isMIMG (uint16_t Opcode) const |

| bool | isSMRD (uint16_t Opcode) const |

| bool | isMUBUF (uint16_t Opcode) const |

| bool | isMTBUF (uint16_t Opcode) const |

| bool | isFLAT (uint16_t Opcode) const |

| bool | isVOP1 (uint16_t Opcode) const |

| bool | isVOP2 (uint16_t Opcode) const |

| bool | isVOP3 (uint16_t Opcode) const |

| bool | isVOPC (uint16_t Opcode) const |

| bool | isInlineConstant (const APInt &Imm) const |

| bool | isInlineConstant (const MachineOperand &MO) const |

| bool | isLiteralConstant (const MachineOperand &MO) const |

| bool | isImmOperandLegal (const MachineInstr *MI, unsigned OpNo, const MachineOperand &MO) const |

| bool | hasVALU32BitEncoding (unsigned Opcode) const |

| Return true if this 64-bit VALU instruction has a 32-bit encoding. This function will return false if you pass it a 32-bit instruction. | |

| bool | hasModifiers (unsigned Opcode) const |

| Return true if this instruction has any modifiers. e.g. src[012]_mod, omod, clamp. | |

| bool | verifyInstruction (const MachineInstr *MI, StringRef &ErrInfo) const override |

| bool | isSALUInstr (const MachineInstr &MI) const |

| bool | isSALUOpSupportedOnVALU (const MachineInstr &MI) const |

| const TargetRegisterClass * | getOpRegClass (const MachineInstr &MI, unsigned OpNo) const |

Return the correct register class for OpNo. For target-specific instructions, this will return the register class that has been defined in tablegen. For generic instructions, like REG_SEQUENCE it will return the register class of its machine operand. to infer the correct register class base on the other operands. | |

| bool | canReadVGPR (const MachineInstr &MI, unsigned OpNo) const |

| void | legalizeOpWithMove (MachineInstr *MI, unsigned OpIdx) const |

Legalize the OpIndex operand of this instruction by inserting a MOV. For example: ADD_I32_e32 VGPR0, 15 to MOV VGPR1, 15 ADD_I32_e32 VGPR0, VGPR1. | |

| bool | isOperandLegal (const MachineInstr *MI, unsigned OpIdx, const MachineOperand *MO=nullptr) const |

Check if MO is a legal operand if it was the OpIdx Operand for MI. | |

| void | legalizeOperands (MachineInstr *MI) const |

Legalize all operands in this instruction. This function may create new instruction and insert them before MI. | |

| void | splitSMRD (MachineInstr *MI, const TargetRegisterClass *HalfRC, unsigned HalfImmOp, unsigned HalfSGPROp, MachineInstr *&Lo, MachineInstr *&Hi) const |

| Split an SMRD instruction into two smaller loads of half the. | |

| void | moveSMRDToVALU (MachineInstr *MI, MachineRegisterInfo &MRI) const |

| void | moveToVALU (MachineInstr &MI) const |

Replace this instruction's opcode with the equivalent VALU opcode. This function will also move the users of MI to the VALU if necessary. | |

| unsigned | calculateIndirectAddress (unsigned RegIndex, unsigned Channel) const override |

Calculate the "Indirect Address" for the given RegIndex and Channel. | |

| const TargetRegisterClass * | getIndirectAddrRegClass () const override |

| MachineInstrBuilder | buildIndirectWrite (MachineBasicBlock *MBB, MachineBasicBlock::iterator I, unsigned ValueReg, unsigned Address, unsigned OffsetReg) const override |

| Build instruction(s) for an indirect register write. | |

| MachineInstrBuilder | buildIndirectRead (MachineBasicBlock *MBB, MachineBasicBlock::iterator I, unsigned ValueReg, unsigned Address, unsigned OffsetReg) const override |

| Build instruction(s) for an indirect register read. | |

| void | reserveIndirectRegisters (BitVector &Reserved, const MachineFunction &MF) const |

| void | LoadM0 (MachineInstr *MoveRel, MachineBasicBlock::iterator I, unsigned SavReg, unsigned IndexReg) const |

| void | insertNOPs (MachineBasicBlock::iterator MI, int Count) const |

| MachineOperand * | getNamedOperand (MachineInstr &MI, unsigned OperandName) const |

Returns the operand named Op. If MI does not have an operand named Op, this function returns nullptr. | |

Static Public Member Functions | |

| static bool | canFoldOffset (unsigned OffsetSize, unsigned AS) LLVM_READNONE |

| Return true if the given offset Size in bytes can be folded into the immediate offsets of a memory instruction for the given address space. | |

| static unsigned | getVALUOp (const MachineInstr &MI) |

Detailed Description

Definition at line 24 of file SIInstrInfo.h.

Constructor & Destructor Documentation

| SIInstrInfo::SIInstrInfo | ( | const AMDGPUSubtarget & | st | ) | [explicit] |

Definition at line 28 of file SIInstrInfo.cpp.

Member Function Documentation

| bool SIInstrInfo::areLoadsFromSameBasePtr | ( | SDNode * | Load1, |

| SDNode * | Load2, | ||

| int64_t & | Offset1, | ||

| int64_t & | Offset2 | ||

| ) | const [override] |

Definition at line 76 of file SIInstrInfo.cpp.

References findChainOperand(), llvm::SDNode::getMachineOpcode(), llvm::AMDGPU::getNamedOperandIdx(), getNumOperandsNoGlue(), llvm::SDNode::getOperand(), isDS(), llvm::SDNode::isMachineOpcode(), isMTBUF(), isMUBUF(), isSMRD(), and nodesHaveSameOperandValue().

| MachineInstrBuilder SIInstrInfo::buildIndirectRead | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | ValueReg, | ||

| unsigned | Address, | ||

| unsigned | OffsetReg | ||

| ) | const [override, virtual] |

Build instruction(s) for an indirect register read.

- Returns:

- The instruction that performs the indirect register read

Implements llvm::AMDGPUInstrInfo.

Definition at line 1972 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineBasicBlock::findDebugLoc(), llvm::AMDGPUInstrInfo::getIndirectIndexBegin(), and llvm::MachineBasicBlock::getParent().

| MachineInstrBuilder SIInstrInfo::buildIndirectWrite | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | ValueReg, | ||

| unsigned | Address, | ||

| unsigned | OffsetReg | ||

| ) | const [override, virtual] |

Build instruction(s) for an indirect register write.

- Returns:

- The instruction that performs the indirect register write

Implements llvm::AMDGPUInstrInfo.

Definition at line 1954 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::RegState::Define, llvm::MachineBasicBlock::findDebugLoc(), llvm::AMDGPUInstrInfo::getIndirectIndexBegin(), and llvm::MachineBasicBlock::getParent().

| MachineInstr * SIInstrInfo::buildMovInstr | ( | MachineBasicBlock * | MBB, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | DstReg, | ||

| unsigned | SrcReg | ||

| ) | const [override, virtual] |

Build a MOV instruction.

Implements llvm::AMDGPUInstrInfo.

Definition at line 600 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), and llvm::MachineBasicBlock::findDebugLoc().

| unsigned SIInstrInfo::calculateIndirectAddress | ( | unsigned | RegIndex, |

| unsigned | Channel | ||

| ) | const [override, virtual] |

Calculate the "Indirect Address" for the given RegIndex and Channel.

We model indirect addressing using a virtual address space that can be accesed with loads and stores. The "Indirect Address" is the memory address in this virtual address space that maps to the given RegIndex and Channel.

Implements llvm::AMDGPUInstrInfo.

Definition at line 1770 of file SIInstrInfo.cpp.

| bool SIInstrInfo::canFoldOffset | ( | unsigned | OffsetSize, |

| unsigned | AS | ||

| ) | [static] |

Return true if the given offset Size in bytes can be folded into the immediate offsets of a memory instruction for the given address space.

Definition at line 761 of file SIInstrInfo.cpp.

References AMDGPUAS::CONSTANT_ADDRESS, AMDGPUAS::GLOBAL_ADDRESS, llvm::isUInt< 16 >(), llvm::isUInt< 8 >(), AMDGPUAS::LOCAL_ADDRESS, AMDGPUAS::PRIVATE_ADDRESS, and AMDGPUAS::REGION_ADDRESS.

| bool SIInstrInfo::canReadVGPR | ( | const MachineInstr & | MI, |

| unsigned | OpNo | ||

| ) | const |

- Returns:

- true if it is legal for the operand at index

OpNoto read a VGPR.

Definition at line 1014 of file SIInstrInfo.cpp.

References llvm::TargetOpcode::COPY, llvm::MachineInstr::getOpcode(), getOpRegClass(), llvm::SIRegisterInfo::hasVGPRs(), llvm::TargetOpcode::INSERT_SUBREG, llvm::TargetOpcode::PHI, and llvm::TargetOpcode::REG_SEQUENCE.

Referenced by moveToVALU().

| MachineInstr * SIInstrInfo::commuteInstruction | ( | MachineInstr * | MI, |

| bool | NewMI = false |

||

| ) | const [override] |

Definition at line 551 of file SIInstrInfo.cpp.

References llvm::LibFunc::abs, llvm::MachineOperand::ChangeToImmediate(), llvm::MachineOperand::ChangeToRegister(), commuteOpcode(), llvm::MachineOperand::getImm(), getNamedOperand(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineOperand::isFPImm(), isOperandLegal(), llvm::MachineOperand::isReg(), isVOP2(), isVOP3(), llvm::AArch64CC::MI, llvm::MachineInstr::setDesc(), and llvm::MachineOperand::setSubReg().

Referenced by foldImmediates(), and legalizeOperands().

| unsigned SIInstrInfo::commuteOpcode | ( | unsigned | Opcode | ) | const |

Definition at line 422 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getCommuteOrig(), and llvm::AMDGPU::getCommuteRev().

Referenced by commuteInstruction().

| void SIInstrInfo::copyPhysReg | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| DebugLoc | DL, | ||

| unsigned | DestReg, | ||

| unsigned | SrcReg, | ||

| bool | KillSrc | ||

| ) | const [override] |

Definition at line 287 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), contains(), llvm::TargetOpcode::COPY, llvm::RegState::Define, llvm::getKillRegState(), I, llvm::RegState::Implicit, llvm_unreachable, and llvm::MachineBasicBlock::rend().

| bool SIInstrInfo::expandPostRAPseudo | ( | MachineBasicBlock::iterator | MI | ) | const [override] |

Reimplemented from llvm::AMDGPUInstrInfo.

Definition at line 521 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::MachineInstrBuilder::addTargetIndex(), llvm::BuildMI(), llvm::RegState::Define, llvm::MachineInstr::eraseFromParent(), llvm::MachineBasicBlock::findDebugLoc(), llvm::MachineBasicBlock::getParent(), llvm::RegState::Implicit, and llvm::AMDGPU::TI_CONSTDATA_START.

| const TargetRegisterClass * SIInstrInfo::getIndirectAddrRegClass | ( | ) | const [override, virtual] |

- Returns:

- The register class to be used for loading and storing values from an "Indirect Address" .

Implements llvm::AMDGPUInstrInfo.

Definition at line 1776 of file SIInstrInfo.cpp.

| bool SIInstrInfo::getLdStBaseRegImmOfs | ( | MachineInstr * | LdSt, |

| unsigned & | BaseReg, | ||

| unsigned & | Offset, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Definition at line 177 of file SIInstrInfo.cpp.

References llvm::MachineOperand::getImm(), getNamedOperand(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getOpcode(), getOpRegClass(), llvm::MachineOperand::getReg(), llvm::TargetRegisterClass::getSize(), isDS(), isMTBUF(), isMUBUF(), isSMRD(), isStride64(), llvm::MachineInstr::mayLoad(), and llvm::MachineInstr::mayStore().

| MachineOperand * SIInstrInfo::getNamedOperand | ( | MachineInstr & | MI, |

| unsigned | OperandName | ||

| ) | const |

Returns the operand named Op. If MI does not have an operand named Op, this function returns nullptr.

Definition at line 2018 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getOpcode(), and llvm::MachineInstr::getOperand().

Referenced by canShrink(), commuteInstruction(), foldImmediates(), getLdStBaseRegImmOfs(), legalizeOperands(), and splitSMRD().

| const TargetRegisterClass * SIInstrInfo::getOpRegClass | ( | const MachineInstr & | MI, |

| unsigned | OpNo | ||

| ) | const |

Return the correct register class for OpNo. For target-specific instructions, this will return the register class that has been defined in tablegen. For generic instructions, like REG_SEQUENCE it will return the register class of its machine operand. to infer the correct register class base on the other operands.

Definition at line 1002 of file SIInstrInfo.cpp.

References llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineInstr::isVariadic(), llvm::MCInstrDesc::OpInfo, and llvm::MCOperandInfo::RegClass.

Referenced by canReadVGPR(), getLdStBaseRegImmOfs(), legalizeOperands(), and moveToVALU().

| const SIRegisterInfo& llvm::SIInstrInfo::getRegisterInfo | ( | ) | const [inline, override, virtual] |

Implements llvm::AMDGPUInstrInfo.

Definition at line 61 of file SIInstrInfo.h.

Referenced by foldImmediates().

| unsigned SIInstrInfo::getVALUOp | ( | const MachineInstr & | MI | ) | [static] |

Definition at line 943 of file SIInstrInfo.cpp.

References llvm::TargetOpcode::COPY, llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::TargetOpcode::INSERT_SUBREG, llvm::MachineOperand::isReg(), llvm::TargetOpcode::PHI, and llvm::TargetOpcode::REG_SEQUENCE.

Referenced by isSALUOpSupportedOnVALU(), moveSMRDToVALU(), and moveToVALU().

| bool SIInstrInfo::hasModifiers | ( | unsigned | Opcode | ) | const |

Return true if this instruction has any modifiers. e.g. src[012]_mod, omod, clamp.

Definition at line 787 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getNamedOperandIdx().

| bool SIInstrInfo::hasVALU32BitEncoding | ( | unsigned | Opcode | ) | const |

Return true if this 64-bit VALU instruction has a 32-bit encoding. This function will return false if you pass it a 32-bit instruction.

Definition at line 783 of file SIInstrInfo.cpp.

References llvm::AMDGPU::getVOPe32().

| void SIInstrInfo::insertNOPs | ( | MachineBasicBlock::iterator | MI, |

| int | Count | ||

| ) | const |

Definition at line 507 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::BuildMI(), and llvm::AArch64CC::MI.

Referenced by llvm::SIRegisterInfo::eliminateFrameIndex().

| bool SIInstrInfo::isDS | ( | uint16_t | Opcode | ) | const |

Definition at line 644 of file SIInstrInfo.cpp.

Referenced by areLoadsFromSameBasePtr(), getLdStBaseRegImmOfs(), and shouldClusterLoads().

| bool SIInstrInfo::isFLAT | ( | uint16_t | Opcode | ) | const |

Definition at line 664 of file SIInstrInfo.cpp.

References SIInstrFlags::FLAT.

| bool SIInstrInfo::isImmOperandLegal | ( | const MachineInstr * | MI, |

| unsigned | OpNo, | ||

| const MachineOperand & | MO | ||

| ) | const |

Definition at line 746 of file SIInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), llvm::MCOI::OPERAND_IMMEDIATE, llvm::MCOperandInfo::OperandType, llvm::MCOperandInfo::RegClass, and llvm::SIRegisterInfo::regClassCanUseImmediate().

Referenced by llvm::SIRegisterInfo::eliminateFrameIndex().

| bool SIInstrInfo::isInlineConstant | ( | const APInt & | Imm | ) | const |

Definition at line 688 of file SIInstrInfo.cpp.

References llvm::APInt::floatToBits(), and llvm::APInt::getSExtValue().

Referenced by isInlineConstant(), isLiteralConstant(), and llvm::SITargetLowering::shouldConvertConstantLoadToIntImm().

| bool SIInstrInfo::isInlineConstant | ( | const MachineOperand & | MO | ) | const |

Definition at line 713 of file SIInstrInfo.cpp.

References llvm::APFloat::bitcastToAPInt(), llvm::MachineOperand::getFPImm(), llvm::MachineOperand::getImm(), llvm::ConstantFP::getValueAPF(), llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), and isInlineConstant().

| bool SIInstrInfo::isLiteralConstant | ( | const MachineOperand & | MO | ) | const |

Definition at line 725 of file SIInstrInfo.cpp.

References llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), and isInlineConstant().

Referenced by foldImmediates(), legalizeOperands(), and verifyInstruction().

| bool SIInstrInfo::isMIMG | ( | uint16_t | Opcode | ) | const |

Definition at line 648 of file SIInstrInfo.cpp.

References SIInstrFlags::MIMG.

Referenced by llvm::SITargetLowering::AdjustInstrPostInstrSelection(), and llvm::SITargetLowering::PostISelFolding().

| bool SIInstrInfo::isMov | ( | unsigned | Opcode | ) | const [override, virtual] |

Implements llvm::AMDGPUInstrInfo.

Definition at line 608 of file SIInstrInfo.cpp.

| bool SIInstrInfo::isMTBUF | ( | uint16_t | Opcode | ) | const |

Definition at line 660 of file SIInstrInfo.cpp.

References SIInstrFlags::MTBUF.

Referenced by areLoadsFromSameBasePtr(), getLdStBaseRegImmOfs(), and shouldClusterLoads().

| bool SIInstrInfo::isMUBUF | ( | uint16_t | Opcode | ) | const |

Definition at line 656 of file SIInstrInfo.cpp.

References SIInstrFlags::MUBUF.

Referenced by areLoadsFromSameBasePtr(), getLdStBaseRegImmOfs(), and shouldClusterLoads().

| bool SIInstrInfo::isOperandLegal | ( | const MachineInstr * | MI, |

| unsigned | OpIdx, | ||

| const MachineOperand * | MO = nullptr |

||

| ) | const |

Check if MO is a legal operand if it was the OpIdx Operand for MI.

Definition at line 1129 of file SIInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isTargetIndex(), llvm::MCInstrDesc::OpInfo, llvm::MCOperandInfo::RegClass, and llvm::SIRegisterInfo::regClassCanUseImmediate().

Referenced by commuteInstruction(), and legalizeOperands().

| bool SIInstrInfo::isSafeToMoveRegClassDefs | ( | const TargetRegisterClass * | RC | ) | const [override] |

Reimplemented from llvm::AMDGPUInstrInfo.

Definition at line 620 of file SIInstrInfo.cpp.

| bool SIInstrInfo::isSALUInstr | ( | const MachineInstr & | MI | ) | const |

Definition at line 684 of file SIInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), and SIInstrFlags::SALU.

| bool SIInstrInfo::isSALUOpSupportedOnVALU | ( | const MachineInstr & | MI | ) | const |

Definition at line 998 of file SIInstrInfo.cpp.

References getVALUOp().

| bool SIInstrInfo::isSMRD | ( | uint16_t | Opcode | ) | const |

Definition at line 652 of file SIInstrInfo.cpp.

References SIInstrFlags::SMRD.

Referenced by areLoadsFromSameBasePtr(), getLdStBaseRegImmOfs(), moveToVALU(), and shouldClusterLoads().

| bool SIInstrInfo::isTriviallyReMaterializable | ( | const MachineInstr * | MI, |

| AliasAnalysis * | AA = nullptr |

||

| ) | const |

Definition at line 625 of file SIInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::isImm().

| bool SIInstrInfo::isVOP1 | ( | uint16_t | Opcode | ) | const |

Definition at line 668 of file SIInstrInfo.cpp.

References SIInstrFlags::VOP1.

Referenced by foldImmediates(), and verifyInstruction().

| bool SIInstrInfo::isVOP2 | ( | uint16_t | Opcode | ) | const |

Definition at line 672 of file SIInstrInfo.cpp.

References SIInstrFlags::VOP2.

Referenced by commuteInstruction(), foldImmediates(), legalizeOperands(), and verifyInstruction().

| bool SIInstrInfo::isVOP3 | ( | uint16_t | Opcode | ) | const |

Definition at line 676 of file SIInstrInfo.cpp.

References SIInstrFlags::VOP3.

Referenced by commuteInstruction(), legalizeOperands(), and verifyInstruction().

| bool SIInstrInfo::isVOPC | ( | uint16_t | Opcode | ) | const |

Definition at line 680 of file SIInstrInfo.cpp.

References SIInstrFlags::VOPC.

Referenced by foldImmediates(), and verifyInstruction().

| void SIInstrInfo::legalizeOperands | ( | MachineInstr * | MI | ) | const |

Legalize all operands in this instruction. This function may create new instruction and insert them before MI.

Definition at line 1156 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), commuteInstruction(), llvm::TargetOpcode::COPY, llvm::MachineRegisterInfo::createVirtualRegister(), llvm::AMDGPU::getAddr64Inst(), llvm::MachineInstr::getDebugLoc(), llvm::SIRegisterInfo::getEquivalentVGPRClass(), llvm::MachineBasicBlock::getFirstTerminator(), llvm::MachineOperand::getImm(), llvm::MachineOperand::getMBB(), getNamedOperand(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOpRegClass(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::SIRegisterInfo::hasVGPRs(), llvm::RegState::Implicit, llvm::RegState::ImplicitDefine, llvm::TargetOpcode::INSERT_SUBREG, llvm::MachineInstr::isCommutable(), llvm::MachineOperand::isImm(), isLiteralConstant(), isOperandLegal(), llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRClass(), llvm::TargetRegisterInfo::isVirtualRegister(), isVOP2(), isVOP3(), legalizeOpWithMove(), llvm::AArch64CC::MI, llvm::TargetOpcode::PHI, llvm::TargetOpcode::REG_SEQUENCE, llvm::MachineInstr::removeFromParent(), llvm::AMDGPU::RSRC_DATA_FORMAT, and llvm::MachineOperand::setReg().

Referenced by moveToVALU().

| void SIInstrInfo::legalizeOpWithMove | ( | MachineInstr * | MI, |

| unsigned | OpIdx | ||

| ) | const |

Legalize the OpIndex operand of this instruction by inserting a MOV. For example: ADD_I32_e32 VGPR0, 15 to MOV VGPR1, 15 ADD_I32_e32 VGPR0, VGPR1.

If the operand being legalized is a register, then a COPY will be used instead of MOV.

Definition at line 1026 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addOperand(), llvm::BuildMI(), llvm::MachineOperand::ChangeToRegister(), llvm::TargetOpcode::COPY, llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineBasicBlock::findDebugLoc(), llvm::SIRegisterInfo::getEquivalentVGPRClass(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), I, llvm::MachineOperand::isReg(), llvm::SIRegisterInfo::isSGPRClass(), and llvm::AArch64CC::MI.

Referenced by legalizeOperands().

| void llvm::SIInstrInfo::LoadM0 | ( | MachineInstr * | MoveRel, |

| MachineBasicBlock::iterator | I, | ||

| unsigned | SavReg, | ||

| unsigned | IndexReg | ||

| ) | const |

| void SIInstrInfo::loadRegFromStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | DestReg, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Reimplemented from llvm::AMDGPUInstrInfo.

Definition at line 474 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::BuildMI(), llvm::LLVMContext::emitError(), llvm::MachineBasicBlock::findDebugLoc(), llvm::Function::getContext(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getFunction(), llvm::MachineBasicBlock::getParent(), llvm::TargetRegisterClass::getSize(), llvm::SIRegisterInfo::hasVGPRs(), llvm::SIRegisterInfo::isSGPRClass(), llvm_unreachable, and llvm::MachineFrameInfo::setObjectAlignment().

| void SIInstrInfo::moveSMRDToVALU | ( | MachineInstr * | MI, |

| MachineRegisterInfo & | MRI | ||

| ) | const |

Definition at line 1506 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstr::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineOperand::ChangeToRegister(), llvm::MachineOperand::CreateImm(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), getVALUOp(), llvm::HexagonISD::Hi, llvm::MachineOperand::isImm(), llvm::MachineOperand::isReg(), llvm::HexagonISD::Lo, llvm::TargetOpcode::REG_SEQUENCE, llvm::MachineRegisterInfo::replaceRegWith(), llvm::AMDGPU::RSRC_DATA_FORMAT, llvm::MachineInstr::setDesc(), llvm::MachineOperand::setReg(), and splitSMRD().

Referenced by moveToVALU().

| void SIInstrInfo::moveToVALU | ( | MachineInstr & | MI | ) | const |

Replace this instruction's opcode with the equivalent VALU opcode. This function will also move the users of MI to the VALU if necessary.

Definition at line 1602 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstr::addOperand(), llvm::BuildMI(), canReadVGPR(), llvm::TargetOpcode::COPY, llvm::MachineOperand::CreateImm(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::SmallVectorBase::empty(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::getDebugLoc(), llvm::SIRegisterInfo::getEquivalentVGPRClass(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), getOpRegClass(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), getVALUOp(), llvm::SIRegisterInfo::hasVGPRs(), I, llvm::TargetOpcode::INSERT_SUBREG, llvm::MachineOperand::isImm(), llvm::MachineOperand::isReg(), isSMRD(), legalizeOperands(), llvm_unreachable, moveSMRDToVALU(), llvm::TargetOpcode::PHI, llvm::SmallVectorImpl< T >::pop_back_val(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::TargetOpcode::REG_SEQUENCE, llvm::MachineInstr::RemoveOperand(), llvm::MachineRegisterInfo::replaceRegWith(), llvm::MachineInstr::setDesc(), llvm::MachineRegisterInfo::use_begin(), and llvm::MachineRegisterInfo::use_end().

| void SIInstrInfo::reserveIndirectRegisters | ( | BitVector & | Reserved, |

| const MachineFunction & | MF | ||

| ) | const |

Definition at line 1990 of file SIInstrInfo.cpp.

References llvm::AMDGPUInstrInfo::getIndirectIndexBegin(), llvm::AMDGPUInstrInfo::getIndirectIndexEnd(), and llvm::BitVector::set().

| bool SIInstrInfo::shouldClusterLoads | ( | MachineInstr * | FirstLdSt, |

| MachineInstr * | SecondLdSt, | ||

| unsigned | NumLoads | ||

| ) | const |

Definition at line 264 of file SIInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), isDS(), isMTBUF(), isMUBUF(), and isSMRD().

| void SIInstrInfo::splitSMRD | ( | MachineInstr * | MI, |

| const TargetRegisterClass * | HalfRC, | ||

| unsigned | HalfImmOp, | ||

| unsigned | HalfSGPROp, | ||

| MachineInstr *& | Lo, | ||

| MachineInstr *& | Hi | ||

| ) | const |

Split an SMRD instruction into two smaller loads of half the.

Definition at line 1424 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getImm(), getNamedOperand(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineFunction::getRegInfo(), llvm::TargetRegisterClass::getSize(), llvm::isUInt< 8 >(), llvm_unreachable, and llvm::TargetOpcode::REG_SEQUENCE.

Referenced by moveSMRDToVALU().

| void SIInstrInfo::storeRegToStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | SrcReg, | ||

| bool | isKill, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Reimplemented from llvm::AMDGPUInstrInfo.

Definition at line 436 of file SIInstrInfo.cpp.

References llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::LLVMContext::emitError(), llvm::MachineBasicBlock::findDebugLoc(), llvm::Function::getContext(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getFunction(), llvm::MachineBasicBlock::getParent(), llvm::TargetRegisterClass::getSize(), llvm::SIRegisterInfo::hasVGPRs(), llvm::SIRegisterInfo::isSGPRClass(), llvm_unreachable, and llvm::MachineFrameInfo::setObjectAlignment().

| bool SIInstrInfo::verifyInstruction | ( | const MachineInstr * | MI, |

| StringRef & | ErrInfo | ||

| ) | const [override] |

Definition at line 795 of file SIInstrInfo.cpp.

References compareMachineOp(), llvm::TargetRegisterClass::contains(), contains(), llvm::MachineInstr::dump(), llvm::AMDGPU::getNamedOperandIdx(), llvm::MachineInstr::getNumExplicitOperands(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MCInstrDesc::getOpcode(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isFPImm(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isImplicit(), isLiteralConstant(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), llvm::MCInstrDesc::isVariadic(), llvm::TargetRegisterInfo::isVirtualRegister(), isVOP1(), isVOP2(), isVOP3(), isVOPC(), llvm::MCOI::OPERAND_IMMEDIATE, llvm::MCOI::OPERAND_REGISTER, llvm::MCOperandInfo::OperandType, llvm::MCInstrDesc::OpInfo, llvm::MCOperandInfo::RegClass, and llvm::SIRegisterInfo::regClassCanUseImmediate().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1