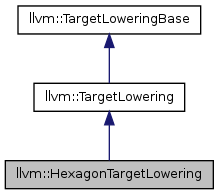

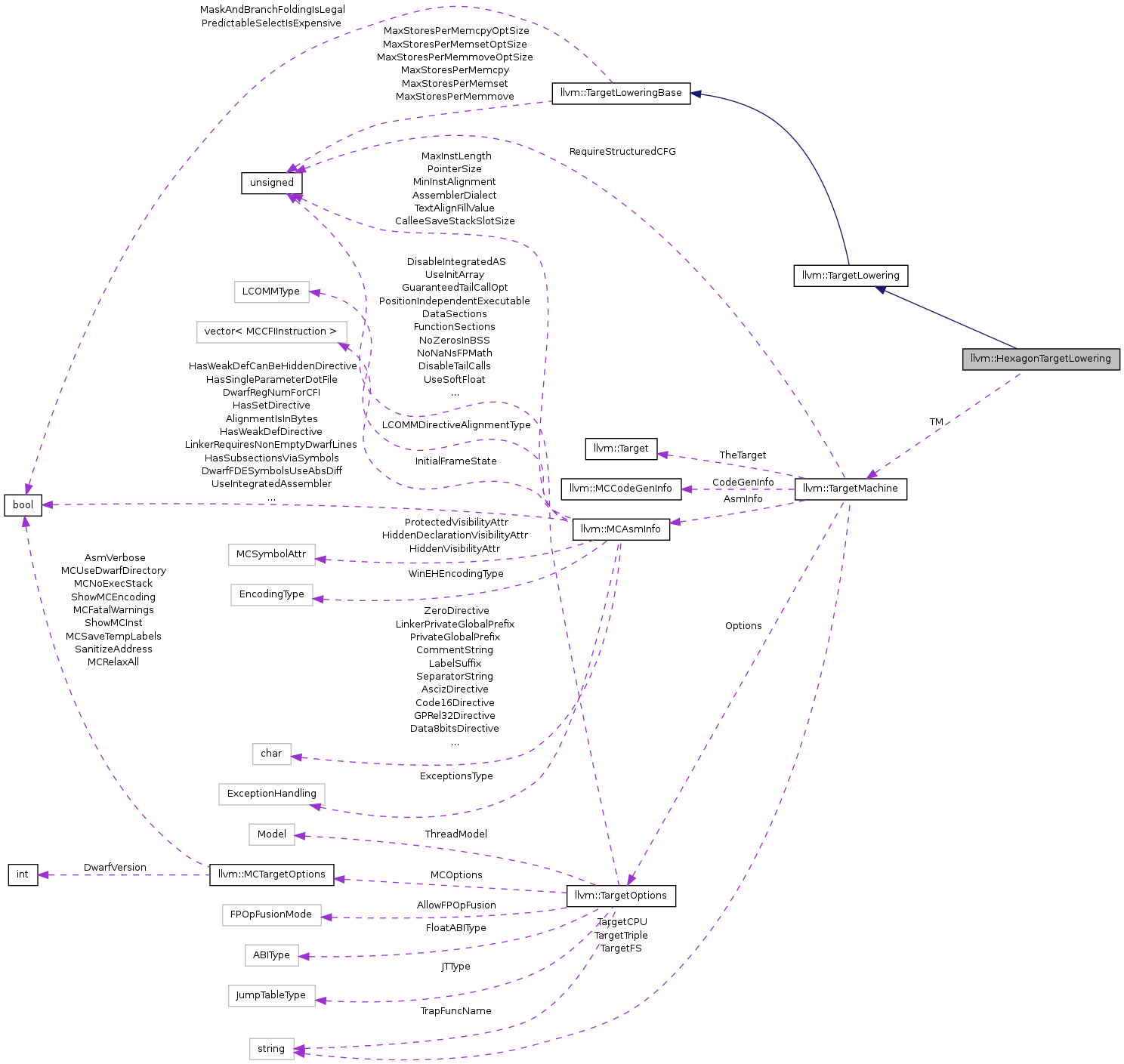

#include <HexagonISelLowering.h>

Detailed Description

Definition at line 70 of file HexagonISelLowering.h.

Constructor & Destructor Documentation

| HexagonTargetLowering::HexagonTargetLowering | ( | const TargetMachine & | targetmachine | ) | [explicit] |

Definition at line 1045 of file HexagonISelLowering.cpp.

References llvm::RTLIB::ADD_F32, llvm::RTLIB::ADD_F64, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::ATOMIC_FENCE, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BSWAP, llvm::ISD::BUILD_PAIR, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::ISD::ConstantFP, llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::TargetLoweringBase::Custom, llvm::RTLIB::DIV_F32, llvm::RTLIB::DIV_F64, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::EH_RETURN, EmitJumpTables, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::MVT::f32, llvm::MVT::f64, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FCOPYSIGN, llvm::ISD::FCOS, llvm::ISD::FDIV, llvm::ISD::FMUL, llvm::ISD::FNEG, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::RTLIB::FPEXT_F32_F64, llvm::ISD::FPOW, llvm::RTLIB::FPROUND_F64_F32, llvm::RTLIB::FPTOSINT_F32_I128, llvm::RTLIB::FPTOSINT_F32_I32, llvm::RTLIB::FPTOSINT_F32_I64, llvm::RTLIB::FPTOSINT_F64_I128, llvm::RTLIB::FPTOSINT_F64_I32, llvm::RTLIB::FPTOSINT_F64_I64, llvm::RTLIB::FPTOUINT_F32_I128, llvm::RTLIB::FPTOUINT_F32_I32, llvm::RTLIB::FPTOUINT_F32_I64, llvm::RTLIB::FPTOUINT_F64_I128, llvm::RTLIB::FPTOUINT_F64_I32, llvm::RTLIB::FPTOUINT_F64_I64, llvm::ISD::FREM, llvm::ISD::FSIN, llvm::ISD::FSINCOS, llvm::ISD::FSQRT, llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::HexagonRegisterInfo::getStackRegister(), llvm::TargetMachine::getSubtarget(), llvm::TargetMachine::getSubtargetImpl(), llvm::ISD::GlobalAddress, llvm::HexagonSubtarget::hasV5TOps(), llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::INLINEASM, llvm::HexagonSubtarget::isSubtargetV2(), llvm::TargetLoweringBase::Legal, llvm::TargetLoweringBase::MaxStoresPerMemcpy, llvm::TargetLoweringBase::MaxStoresPerMemmove, llvm::ISD::MUL, llvm::RTLIB::MUL_F32, llvm::RTLIB::MUL_F64, llvm::RTLIB::O_F32, llvm::RTLIB::O_F64, llvm::RTLIB::OEQ_F32, llvm::RTLIB::OEQ_F64, llvm::RTLIB::OGE_F32, llvm::RTLIB::OGE_F64, llvm::RTLIB::OGT_F32, llvm::RTLIB::OGT_F64, llvm::RTLIB::OLE_F32, llvm::RTLIB::OLE_F64, llvm::RTLIB::OLT_F32, llvm::RTLIB::OLT_F64, llvm::MVT::Other, llvm::ISD::POST_INC, llvm::TargetLoweringBase::Promote, llvm::ISD::ROTL, llvm::ISD::ROTR, llvm::ISD::SDIV, llvm::RTLIB::SDIV_I32, llvm::RTLIB::SDIV_I64, llvm::ISD::SDIVREM, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::TargetLoweringBase::setCondCodeAction(), llvm::TargetLoweringBase::setExceptionPointerRegister(), llvm::TargetLoweringBase::setExceptionSelectorRegister(), llvm::TargetLoweringBase::setIndexedLoadAction(), llvm::TargetLoweringBase::setIndexedStoreAction(), llvm::TargetLoweringBase::setLibcallName(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setMinFunctionAlignment(), llvm::TargetLoweringBase::setMinimumJumpTableEntries(), llvm::ISD::SETO, llvm::ISD::SETOEQ, llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::ISD::SETOLE, llvm::ISD::SETOLT, llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setPrefLoopAlignment(), llvm::TargetLoweringBase::setSchedulingPreference(), llvm::TargetLoweringBase::setStackPointerRegisterToSaveRestore(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SETUEQ, llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SETUNE, llvm::ISD::SETUO, llvm::ISD::SEXTLOAD, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SINT_TO_FP, llvm::RTLIB::SINTTOFP_I128_F32, llvm::RTLIB::SINTTOFP_I128_F64, llvm::RTLIB::SINTTOFP_I32_F32, llvm::RTLIB::SINTTOFP_I32_F64, llvm::RTLIB::SINTTOFP_I64_F32, llvm::RTLIB::SINTTOFP_I64_F64, llvm::ISD::SMUL_LOHI, llvm::ISD::SRA_PARTS, llvm::ISD::SREM, llvm::RTLIB::SREM_I32, llvm::RTLIB::SREM_I64, llvm::ISD::SRL_PARTS, llvm::ISD::STACKRESTORE, llvm::ISD::STACKSAVE, llvm::ISD::SUB, llvm::RTLIB::SUB_F32, llvm::RTLIB::SUB_F64, llvm::ISD::SUBC, llvm::ISD::SUBE, TM, llvm::ISD::TRUNCATE, llvm::ISD::UDIV, llvm::RTLIB::UDIV_I32, llvm::RTLIB::UDIV_I64, llvm::ISD::UDIVREM, llvm::ISD::UINT_TO_FP, llvm::RTLIB::UINTTOFP_I32_F32, llvm::RTLIB::UINTTOFP_I32_F64, llvm::RTLIB::UINTTOFP_I64_F32, llvm::RTLIB::UINTTOFP_I64_F64, llvm::ISD::UMUL_LOHI, llvm::RTLIB::UNE_F32, llvm::RTLIB::UNE_F64, llvm::RTLIB::UO_F32, llvm::RTLIB::UO_F64, llvm::ISD::UREM, llvm::RTLIB::UREM_I32, llvm::RTLIB::UREM_I64, llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VAEND, llvm::ISD::VASTART, and llvm::Sched::VLIW.

Member Function Documentation

| bool HexagonTargetLowering::allowTruncateForTailCall | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if a truncation from Ty1 to Ty2 is permitted when deciding whether a call is in tail position. Typically this means that both results would be assigned to the same register or stack slot, but it could mean the target performs adequate checks of its own before proceeding with the tail call.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1505 of file HexagonISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), and llvm::Type::isIntegerTy().

| MachineBasicBlock * HexagonTargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::TargetLowering.

Definition at line 1575 of file HexagonISelLowering.cpp.

References llvm::HexagonMachineFunctionInfo::addAllocaAdjustInst(), llvm::HexagonISD::ADJDYNALLOC, llvm::MachineFunction::getInfo(), llvm::MachineInstr::getOpcode(), llvm::MachineBasicBlock::getParent(), and llvm_unreachable.

| bool HexagonTargetLowering::getPostIndexedAddressParts | ( | SDNode * | N, |

| SDNode * | Op, | ||

| SDValue & | Base, | ||

| SDValue & | Offset, | ||

| ISD::MemIndexedMode & | AM, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

getPostIndexedAddressParts - returns true by value, base pointer and offset pointer and addressing mode by reference if this node can be combined with a load / store to form a post-indexed load / store.

Reimplemented from llvm::TargetLowering.

Definition at line 652 of file HexagonISelLowering.cpp.

References getIndexedAddressParts(), llvm::SDValue::getNode(), llvm::EVT::getSizeInBits(), llvm::MVT::i64, Is_PostInc_S4_Offset(), llvm::ISD::isSEXTLoad(), llvm::AArch64DB::LD, llvm::ISD::POST_DEC, llvm::ISD::POST_INC, llvm::ISD::SEXTLOAD, and llvm::AArch64DB::ST.

| std::pair< unsigned, const TargetRegisterClass * > HexagonTargetLowering::getRegForInlineAsmConstraint | ( | const std::string & | Constraint, |

| MVT | VT | ||

| ) | const [override, virtual] |

Given a physical register constraint (e.g. {edx}), return the register number and the register class for the register.

Given a register class constraint, like 'r', if this corresponds directly to an LLVM register class, return a register of 0 and the register class pointer.

This should only be used for C_Register constraints. On error, this returns a register number of 0 and a null register class pointer..

Reimplemented from llvm::TargetLowering.

Definition at line 1595 of file HexagonISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm_unreachable, and llvm::MVT::SimpleTy.

| EVT llvm::HexagonTargetLowering::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline, override, virtual] |

Return the ValueType of the result of SETCC operations. Also used to obtain the target's preferred type for the condition operand of SELECT and BRCOND nodes. In the case of BRCOND the argument passed is MVT::Other since there are no other operands to get a type hint from.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 143 of file HexagonISelLowering.h.

References llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::MVT::i1, and llvm::EVT::isVector().

| const char * HexagonTargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

Definition at line 1462 of file HexagonISelLowering.cpp.

References llvm::HexagonISD::ADJDYNALLOC, llvm::HexagonISD::BR_JT, llvm::HexagonISD::BRFCC, llvm::HexagonISD::BRICC, llvm::HexagonISD::CALL, llvm::HexagonISD::CMPFCC, llvm::HexagonISD::CMPICC, llvm::HexagonISD::CONST32, llvm::HexagonISD::CONST32_GP, llvm::HexagonISD::CONST32_Int_Real, llvm::HexagonISD::EH_RETURN, llvm::HexagonISD::FTOI, llvm::HexagonISD::Hi, llvm::HexagonISD::ITOF, llvm::HexagonISD::Lo, llvm::HexagonISD::RET_FLAG, llvm::HexagonISD::SELECT_FCC, llvm::HexagonISD::SELECT_ICC, and llvm::HexagonISD::TC_RETURN.

| bool HexagonTargetLowering::IsEligibleForTailCallOptimization | ( | SDValue | Callee, |

| CallingConv::ID | CalleeCC, | ||

| bool | isVarArg, | ||

| bool | isCalleeStructRet, | ||

| bool | isCallerStructRet, | ||

| const SmallVectorImpl< ISD::OutputArg > & | Outs, | ||

| const SmallVectorImpl< SDValue > & | OutVals, | ||

| const SmallVectorImpl< ISD::InputArg > & | Ins, | ||

| SelectionDAG & | DAG | ||

| ) | const |

IsEligibleForTailCallOptimization - Check whether the call is eligible for tail call optimization. Targets which want to do tail call optimization should implement this function.

Definition at line 1664 of file HexagonISelLowering.cpp.

References llvm::Function::getCallingConv(), llvm::MachineFunction::getFunction(), and llvm::SelectionDAG::getMachineFunction().

Referenced by LowerCall().

| bool HexagonTargetLowering::isFPImmLegal | ( | const APFloat & | Imm, |

| EVT | VT | ||

| ) | const [override, virtual] |

isFPImmLegal - Returns true if the target can instruction select the specified FP immediate natively. If false, the legalizer will materialize the FP immediate as a load from a constant pool.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1624 of file HexagonISelLowering.cpp.

References llvm::TargetMachine::getSubtarget(), and TM.

| bool HexagonTargetLowering::isLegalAddressingMode | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type. The type may be VoidTy, in which case only return true if the addressing mode is legal for a load/store of any legal type. TODO: Handle pre/postinc as well.

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1630 of file HexagonISelLowering.cpp.

References llvm::TargetLoweringBase::AddrMode::BaseGV, llvm::TargetLoweringBase::AddrMode::BaseOffs, and llvm::TargetLoweringBase::AddrMode::Scale.

| bool HexagonTargetLowering::isLegalICmpImmediate | ( | int64_t | Imm | ) | const [override, virtual] |

isLegalICmpImmediate - Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1657 of file HexagonISelLowering.cpp.

| bool HexagonTargetLowering::isTruncateFree | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if it's free to truncate a value of type Ty1 to type Ty2. e.g. On x86 it's free to truncate a i32 value in register EAX to i16 by referencing its sub-register AX.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1488 of file HexagonISelLowering.cpp.

References llvm::EVT::getEVT(), llvm::EVT::getSimpleVT(), llvm::MVT::i32, llvm::MVT::i64, and llvm::EVT::isSimple().

| bool HexagonTargetLowering::isTruncateFree | ( | EVT | VT1, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1497 of file HexagonISelLowering.cpp.

References llvm::EVT::getSimpleVT(), llvm::MVT::i32, llvm::MVT::i64, and llvm::EVT::isSimple().

| SDValue HexagonTargetLowering::LowerATOMIC_FENCE | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1009 of file HexagonISelLowering.cpp.

References llvm::HexagonISD::BARRIER, llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), and llvm::MVT::Other.

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerBlockAddress | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1034 of file HexagonISelLowering.cpp.

References llvm::HexagonISD::CONST32_GP, llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getTargetBlockAddress(), and llvm::MVT::i32.

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerBR_JT | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 745 of file HexagonISelLowering.cpp.

References llvm::ISD::ADD, llvm::HexagonISD::BR_JT, llvm::BlockAddress::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::SelectionDAG::getConstant(), llvm::JumpTableSDNode::getIndex(), llvm::MachineFunction::getJumpTableInfo(), llvm::MachineJumpTableInfo::getJumpTables(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getTargetJumpTable(), llvm::MVT::i32, llvm::MVT::Other, llvm::MachineBasicBlock::setHasAddressTaken(), llvm::ISD::SHL, and llvm::HexagonISD::WrapperJT.

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerCall | ( | TargetLowering::CallLoweringInfo & | CLI, |

| SmallVectorImpl< SDValue > & | InVals | ||

| ) | const [override, virtual] |

LowerCall - Functions arguments are copied from virtual regs to (physical regs)/(stack frame), CALLSEQ_START and CALLSEQ_END are emitted.

Reimplemented from llvm::TargetLowering.

Definition at line 395 of file HexagonISelLowering.cpp.

References llvm::ISD::ADD, llvm::CCValAssign::AExt, llvm::ISD::ANY_EXTEND, llvm::HexagonISD::CALL, llvm::TargetLowering::CallLoweringInfo::CallConv, llvm::TargetLowering::CallLoweringInfo::Callee, CC_Hexagon(), CC_Hexagon_VarArg(), llvm::TargetLowering::CallLoweringInfo::Chain, CreateCopyOfByValArgument(), llvm::TargetLowering::CallLoweringInfo::DAG, llvm::dbgs(), DEBUG, llvm::TargetLowering::CallLoweringInfo::DL, llvm::SmallVectorBase::empty(), llvm::flag_aligned_memcpy, llvm::CCValAssign::Full, G, llvm::SelectionDAG::getCALLSEQ_END(), llvm::SelectionDAG::getCALLSEQ_START(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::MachineFunction::getFunction(), llvm::Function::getFunctionType(), llvm::SelectionDAG::getIntPtrConstant(), llvm::CCValAssign::getLocInfo(), llvm::CCValAssign::getLocMemOffset(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::FunctionType::getNumParams(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::HexagonRegisterInfo::getStackRegister(), llvm::SelectionDAG::getStore(), llvm::SelectionDAG::getSubtarget(), llvm::SelectionDAG::getTargetExternalSymbol(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, llvm::Function::hasStructRetAttr(), llvm::MVT::i32, llvm::MipsISD::Ins, llvm::TargetLowering::CallLoweringInfo::Ins, llvm::ISD::ArgFlagsTy::isByVal(), IsEligibleForTailCallOptimization(), llvm::CCValAssign::isMemLoc(), llvm::CCValAssign::isRegLoc(), llvm::TargetLowering::CallLoweringInfo::IsTailCall, llvm::Function::isVarArg(), llvm::TargetLowering::CallLoweringInfo::IsVarArg, llvm_unreachable, LowerCallResult(), llvm::MVT::Other, llvm::TargetLowering::CallLoweringInfo::Outs, llvm::TargetLowering::CallLoweringInfo::OutVals, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::CCValAssign::SExt, llvm::ISD::SIGN_EXTEND, llvm::SmallVectorTemplateCommon< T >::size(), llvm::HexagonISD::TC_RETURN, llvm::ISD::TokenFactor, llvm::ISD::ZERO_EXTEND, and llvm::CCValAssign::ZExt.

| SDValue HexagonTargetLowering::LowerCallResult | ( | SDValue | Chain, |

| SDValue | InFlag, | ||

| CallingConv::ID | CallConv, | ||

| bool | isVarArg, | ||

| const SmallVectorImpl< ISD::InputArg > & | Ins, | ||

| SDLoc | dl, | ||

| SelectionDAG & | DAG, | ||

| SmallVectorImpl< SDValue > & | InVals, | ||

| const SmallVectorImpl< SDValue > & | OutVals, | ||

| SDValue | Callee | ||

| ) | const |

LowerCallResult - Lower the result values of an ISD::CALL into the appropriate copies out of appropriate physical registers. This assumes that Chain/InFlag are the input chain/flag to use, and that TheCall is the call being lowered. Returns a SDNode with the same number of values as the ISD::CALL.

Definition at line 363 of file HexagonISelLowering.cpp.

References llvm::CCState::AnalyzeCallResult(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getValue(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), RetCC_Hexagon(), and llvm::SmallVectorTemplateCommon< T >::size().

Referenced by LowerCall().

| SDValue HexagonTargetLowering::LowerConstantPool | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 950 of file HexagonISelLowering.cpp.

References llvm::HexagonISD::CONST32, llvm::ConstantPoolSDNode::getAlignment(), llvm::ConstantPoolSDNode::getConstVal(), llvm::ConstantPoolSDNode::getMachineCPVal(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getTargetConstantPool(), llvm::SDValue::getValueType(), and llvm::ConstantPoolSDNode::isMachineConstantPoolEntry().

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerDYNAMIC_STACKALLOC | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 782 of file HexagonISelLowering.cpp.

References llvm::HexagonISD::ADJDYNALLOC, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getMergeValues(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::TargetLoweringBase::getStackPointerRegisterToSaveRestore(), llvm::HexagonRegisterInfo::getStackRegister(), llvm::SelectionDAG::getSubtarget(), llvm::MVT::i32, and llvm::ISD::SUB.

Referenced by LowerOperation().

| SDValue llvm::HexagonTargetLowering::LowerEH_LABEL | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

| SDValue HexagonTargetLowering::LowerEH_RETURN | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1518 of file HexagonISelLowering.cpp.

References llvm::ISD::ADD, llvm::HexagonISD::EH_RETURN, llvm::SelectionDAG::getCopyToReg(), llvm::MachineFunction::getInfo(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getStore(), llvm::MVT::Other, and llvm::HexagonMachineFunctionInfo::setHasEHReturn().

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerFormalArguments | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::InputArg > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | , | ||

| SmallVectorImpl< SDValue > & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower the incoming (formal) arguments, described by the Ins array, into the specified DAG. The implementation should fill in the InVals array with legal-type argument values, and return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 827 of file HexagonISelLowering.cpp.

References llvm::MachineRegisterInfo::addLiveIn(), llvm::CCState::AnalyzeFormalArguments(), CC_Hexagon(), llvm::MachineFrameInfo::CreateFixedObject(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::SmallVectorBase::empty(), llvm::MVT::f32, llvm::ISD::FrameIndex, llvm::ISD::ArgFlagsTy::getByValSize(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getInfo(), llvm::SelectionDAG::getLoad(), llvm::CCValAssign::getLocMemOffset(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::MachineFunction::getRegInfo(), llvm::MVT::getStoreSizeInBits(), HEXAGON_LRFP_SIZE, Hexagon_PointerSize, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::ArgFlagsTy::isByVal(), llvm::CCValAssign::isMemLoc(), llvm::CCValAssign::isRegLoc(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::HexagonMachineFunctionInfo::setVarArgsFrameIndex(), and llvm::ISD::TokenFactor.

| SDValue HexagonTargetLowering::LowerFRAMEADDR | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 991 of file HexagonISelLowering.cpp.

References llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getEntryNode(), llvm::MachineFunction::getFrameInfo(), llvm::HexagonRegisterInfo::getFrameRegister(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getOperand(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::SelectionDAG::getSubtarget(), llvm::SDValue::getValueType(), and llvm::MachineFrameInfo::setFrameAddressIsTaken().

Referenced by LowerOperation(), and LowerRETURNADDR().

| SDValue HexagonTargetLowering::LowerGLOBALADDRESS | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1016 of file HexagonISelLowering.cpp.

References llvm::HexagonISD::CONST32, llvm::HexagonISD::CONST32_GP, llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getObjFileLowering(), llvm::getOffset(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::TargetLoweringBase::getTargetMachine(), and llvm::HexagonTargetObjectFile::IsGlobalInSmallSection().

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerINLINEASM | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 687 of file HexagonISelLowering.cpp.

References llvm::MachineFunction::getInfo(), llvm::InlineAsm::getKind(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::InlineAsm::getNumOperandRegisters(), llvm::SDNode::getNumOperands(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::HexagonRegisterInfo::getRARegister(), getReg(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::SelectionDAG::getSubtarget(), llvm::SDValue::getValueType(), llvm::MVT::Glue, llvm::HexagonMachineFunctionInfo::hasClobberLR(), llvm::ISD::INLINEASM, llvm::InlineAsm::Kind_Clobber, llvm::InlineAsm::Kind_Imm, llvm::InlineAsm::Kind_Mem, llvm::InlineAsm::Kind_RegDef, llvm::InlineAsm::Kind_RegDefEarlyClobber, llvm::InlineAsm::Kind_RegUse, llvm_unreachable, Node, llvm::InlineAsm::Op_FirstOperand, and llvm::HexagonMachineFunctionInfo::setHasClobberLR().

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerINTRINSIC_WO_CHAIN | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 289 of file HexagonISelLowering.cpp.

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

This callback is invoked for operations that are unsupported by the target, which are registered to use 'custom' lowering, and whose defined values are all legal. If the target has no operations that require custom lowering, it need not implement this. The default implementation of this aborts.

Reimplemented from llvm::TargetLowering.

Definition at line 1545 of file HexagonISelLowering.cpp.

References llvm::ISD::ATOMIC_FENCE, llvm::ISD::BlockAddress, llvm::ISD::BR_JT, llvm::ISD::ConstantPool, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::EH_RETURN, llvm::ISD::FRAMEADDR, llvm::SDValue::getOpcode(), llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::ISD::INLINEASM, llvm::ISD::INTRINSIC_WO_CHAIN, llvm_unreachable, LowerATOMIC_FENCE(), LowerBlockAddress(), LowerBR_JT(), LowerConstantPool(), LowerDYNAMIC_STACKALLOC(), LowerEH_RETURN(), LowerFRAMEADDR(), LowerGLOBALADDRESS(), LowerINLINEASM(), LowerINTRINSIC_WO_CHAIN(), LowerRETURNADDR(), LowerVASTART(), llvm::ISD::RETURNADDR, llvm::ISD::SELECT, and llvm::ISD::VASTART.

| SDValue HexagonTargetLowering::LowerReturn | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::OutputArg > & | , | ||

| const SmallVectorImpl< SDValue > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower outgoing return values, described by the Outs array, into the specified DAG. The implementation should return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 315 of file HexagonISelLowering.cpp.

References llvm::CCState::AnalyzeReturn(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyToReg(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getRegister(), llvm::SDValue::getValue(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::HexagonISD::RET_FLAG, RetCC_Hexagon(), and llvm::SmallVectorTemplateCommon< T >::size().

| SDValue HexagonTargetLowering::LowerRETURNADDR | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 965 of file HexagonISelLowering.cpp.

References llvm::ISD::ADD, llvm::MachineFunction::addLiveIn(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getEntryNode(), llvm::MachineFunction::getFrameInfo(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::MCRegisterInfo::getRARegister(), llvm::TargetLoweringBase::getRegClassFor(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::SelectionDAG::getSubtarget(), llvm::SDValue::getValueType(), llvm::MVT::i32, LowerFRAMEADDR(), llvm::MachineFrameInfo::setReturnAddressIsTaken(), and llvm::TargetLowering::verifyReturnAddressArgumentIsConstant().

Referenced by LowerOperation().

| SDValue HexagonTargetLowering::LowerVASTART | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 937 of file HexagonISelLowering.cpp.

References llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getInfo(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getOperand(), llvm::SelectionDAG::getStore(), llvm::HexagonMachineFunctionInfo::getVarArgsFrameIndex(), and llvm::MVT::i32.

Referenced by LowerOperation().

Member Data Documentation

Reimplemented from llvm::TargetLoweringBase.

Definition at line 77 of file HexagonISelLowering.h.

Referenced by HexagonTargetLowering(), and isFPImmLegal().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1