#include <NVPTXISelLowering.h>

Detailed Description

Definition at line 437 of file NVPTXISelLowering.h.

Constructor & Destructor Documentation

| NVPTXTargetLowering::NVPTXTargetLowering | ( | const NVPTXTargetMachine & | TM | ) | [explicit] |

Definition at line 109 of file NVPTXISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::AND, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BRIND, llvm::ISD::BSWAP, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::ISD::ConstantFP, llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::TargetLoweringBase::Custom, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::ISD::FADD, llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::ISD::GlobalAddress, llvm::NVPTXSubtarget::hasROT32(), llvm::NVPTXSubtarget::hasROT64(), llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::INTRINSIC_W_CHAIN, IsPTXVectorType(), llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::TargetLoweringBase::Legal, llvm::ISD::LOAD, llvm::TargetLoweringBase::MaxStoresPerMemcpy, llvm::TargetLoweringBase::MaxStoresPerMemmove, llvm::TargetLoweringBase::MaxStoresPerMemset, llvm::ISD::MUL, llvm::MVT::Other, llvm::TargetLoweringBase::Promote, llvm::Sched::RegPressure, llvm::ISD::ROTL, llvm::ISD::ROTR, sched4reg, llvm::ISD::SELECT_CC, llvm::TargetLoweringBase::setBooleanContents(), llvm::TargetLoweringBase::setBooleanVectorContents(), llvm::TargetLoweringBase::setJumpIsExpensive(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setSchedulingPreference(), llvm::TargetLoweringBase::setTargetDAGCombine(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SEXTLOAD, llvm::ISD::SHL, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND_INREG, llvm::Sched::Source, llvm::ISD::SRA_PARTS, llvm::ISD::SRL_PARTS, llvm::ISD::STORE, llvm::ISD::TRAP, llvm::TargetLoweringBase::ZeroOrNegativeOneBooleanContent, and llvm::ISD::ZEXTLOAD.

Member Function Documentation

| bool NVPTXTargetLowering::allowFMA | ( | MachineFunction & | MF, |

| CodeGenOpt::Level | OptLevel | ||

| ) | const |

Definition at line 3794 of file NVPTXISelLowering.cpp.

References llvm::TargetOptions::AllowFPOpFusion, F(), llvm::FPOpFusion::Fast, FMAContractLevelOpt, llvm::Function::getFnAttribute(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getTarget(), llvm::Attribute::getValueAsString(), llvm::Function::hasFnAttribute(), llvm::TargetMachine::Options, and llvm::TargetOptions::UnsafeFPMath.

| NVPTXTargetLowering::ConstraintType NVPTXTargetLowering::getConstraintType | ( | const std::string & | Constraint | ) | const [override, virtual] |

getConstraintType - Given a constraint letter, return the type of constraint it is for this target.

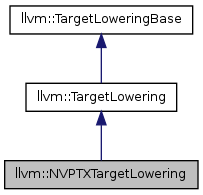

Reimplemented from llvm::TargetLowering.

Definition at line 3740 of file NVPTXISelLowering.cpp.

References llvm::TargetLowering::C_RegisterClass.

| unsigned NVPTXTargetLowering::getFunctionAlignment | ( | const Function * | F | ) | const |

getFunctionAlignment - Return the Log2 alignment of this function.

Definition at line 3786 of file NVPTXISelLowering.cpp.

| TargetLoweringBase::LegalizeTypeAction NVPTXTargetLowering::getPreferredVectorAction | ( | EVT | VT | ) | const [override, virtual] |

Return the preferred vector type legalization action.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 860 of file NVPTXISelLowering.cpp.

References llvm::EVT::getScalarType(), llvm::EVT::getVectorNumElements(), llvm::MVT::i1, and llvm::TargetLoweringBase::TypeSplitVector.

| std::string NVPTXTargetLowering::getPrototype | ( | Type * | retTy, |

| const ArgListTy & | Args, | ||

| const SmallVectorImpl< ISD::OutputArg > & | Outs, | ||

| unsigned | retAlignment, | ||

| const ImmutableCallSite * | CS | ||

| ) | const |

Definition at line 876 of file NVPTXISelLowering.cpp.

References llvm::ComputeValueVTs(), llvm::dyn_cast(), llvm::getAlign(), getBitWidth(), llvm::TargetLoweringBase::getDataLayout(), llvm::SequentialType::getElementType(), llvm::CallSiteBase< FunTy, ValTy, UserTy, InstrTy, CallTy, InvokeTy, IterTy >::getInstruction(), llvm::TargetLoweringBase::getPointerTy(), llvm::Type::getPrimitiveSizeInBits(), llvm::MVT::getSizeInBits(), llvm::NVPTXSubtarget::getSmVersion(), llvm::DataLayout::getTypeAllocSize(), llvm::Type::getTypeID(), llvm::TargetLoweringBase::getValueType(), llvm::MVT::i16, llvm::MVT::i8, llvm::Type::isAggregateType(), llvm::Type::isFloatingPointTy(), llvm::Type::isIntegerTy(), llvm::Type::isVectorTy(), llvm::SmallVectorTemplateCommon< T >::size(), llvm::Type::StructTyID, uniqueCallSite, and llvm::Type::VoidTyID.

Referenced by LowerCall().

| std::pair< unsigned, const TargetRegisterClass * > NVPTXTargetLowering::getRegForInlineAsmConstraint | ( | const std::string & | Constraint, |

| MVT | VT | ||

| ) | const [override, virtual] |

Given a physical register constraint (e.g. {edx}), return the register number and the register class for the register.

Given a register class constraint, like 'r', if this corresponds directly to an LLVM register class, return a register of 0 and the register class pointer.

This should only be used for C_Register constraints. On error, this returns a register number of 0 and a null register class pointer..

Reimplemented from llvm::TargetLowering.

Definition at line 3761 of file NVPTXISelLowering.cpp.

| MVT llvm::NVPTXTargetLowering::getScalarShiftAmountTy | ( | EVT | LHSTy | ) | const [inline, override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 501 of file NVPTXISelLowering.h.

References llvm::MVT::i32.

| EVT llvm::NVPTXTargetLowering::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [inline, override, virtual] |

Return the ValueType of the result of SETCC operations. Also used to obtain the target's preferred type for the condition operand of SELECT and BRCOND nodes. In the case of BRCOND the argument passed is MVT::Other since there are no other operands to get a type hint from.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 463 of file NVPTXISelLowering.h.

References llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::MVT::i1, and llvm::EVT::isVector().

| const char * NVPTXTargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

Definition at line 276 of file NVPTXISelLowering.cpp.

References llvm::NVPTXISD::CALL, llvm::NVPTXISD::CallArg, llvm::NVPTXISD::CallArgBegin, llvm::NVPTXISD::CallArgEnd, llvm::NVPTXISD::CallPrototype, llvm::NVPTXISD::CallSeqBegin, llvm::NVPTXISD::CallSeqEnd, llvm::NVPTXISD::CallSymbol, llvm::NVPTXISD::CallVal, llvm::NVPTXISD::CallVoid, llvm::NVPTXISD::DeclareParam, llvm::NVPTXISD::DeclareRet, llvm::NVPTXISD::DeclareRetParam, llvm::NVPTXISD::DeclareScalarParam, llvm::NVPTXISD::FUN_SHFL_CLAMP, llvm::NVPTXISD::FUN_SHFR_CLAMP, llvm::NVPTXISD::IMAD, llvm::NVPTXISD::LastCallArg, llvm::NVPTXISD::LDGV2, llvm::NVPTXISD::LDGV4, llvm::NVPTXISD::LDUV2, llvm::NVPTXISD::LDUV4, llvm::NVPTXISD::LoadParam, llvm::NVPTXISD::LoadParamV2, llvm::NVPTXISD::LoadParamV4, llvm::NVPTXISD::LoadV2, llvm::NVPTXISD::LoadV4, llvm::NVPTXISD::MoveParam, llvm::NVPTXISD::MUL_WIDE_SIGNED, llvm::NVPTXISD::MUL_WIDE_UNSIGNED, llvm::NVPTXISD::PrintCall, llvm::NVPTXISD::Prototype, llvm::NVPTXISD::PseudoUseParam, llvm::NVPTXISD::RET_FLAG, llvm::NVPTXISD::RETURN, llvm::NVPTXISD::StoreParam, llvm::NVPTXISD::StoreParamS32, llvm::NVPTXISD::StoreParamU32, llvm::NVPTXISD::StoreParamV2, llvm::NVPTXISD::StoreParamV4, llvm::NVPTXISD::StoreRetval, llvm::NVPTXISD::StoreRetvalV2, llvm::NVPTXISD::StoreRetvalV4, llvm::NVPTXISD::StoreV2, llvm::NVPTXISD::StoreV4, llvm::NVPTXISD::Suld1DArrayI16Clamp, llvm::NVPTXISD::Suld1DArrayI16Trap, llvm::NVPTXISD::Suld1DArrayI16Zero, llvm::NVPTXISD::Suld1DArrayI32Clamp, llvm::NVPTXISD::Suld1DArrayI32Trap, llvm::NVPTXISD::Suld1DArrayI32Zero, llvm::NVPTXISD::Suld1DArrayI64Clamp, llvm::NVPTXISD::Suld1DArrayI64Trap, llvm::NVPTXISD::Suld1DArrayI64Zero, llvm::NVPTXISD::Suld1DArrayI8Clamp, llvm::NVPTXISD::Suld1DArrayI8Trap, llvm::NVPTXISD::Suld1DArrayI8Zero, llvm::NVPTXISD::Suld1DArrayV2I16Clamp, llvm::NVPTXISD::Suld1DArrayV2I16Trap, llvm::NVPTXISD::Suld1DArrayV2I16Zero, llvm::NVPTXISD::Suld1DArrayV2I32Clamp, llvm::NVPTXISD::Suld1DArrayV2I32Trap, llvm::NVPTXISD::Suld1DArrayV2I32Zero, llvm::NVPTXISD::Suld1DArrayV2I64Clamp, llvm::NVPTXISD::Suld1DArrayV2I64Trap, llvm::NVPTXISD::Suld1DArrayV2I64Zero, llvm::NVPTXISD::Suld1DArrayV2I8Clamp, llvm::NVPTXISD::Suld1DArrayV2I8Trap, llvm::NVPTXISD::Suld1DArrayV2I8Zero, llvm::NVPTXISD::Suld1DArrayV4I16Clamp, llvm::NVPTXISD::Suld1DArrayV4I16Trap, llvm::NVPTXISD::Suld1DArrayV4I16Zero, llvm::NVPTXISD::Suld1DArrayV4I32Clamp, llvm::NVPTXISD::Suld1DArrayV4I32Trap, llvm::NVPTXISD::Suld1DArrayV4I32Zero, llvm::NVPTXISD::Suld1DArrayV4I8Clamp, llvm::NVPTXISD::Suld1DArrayV4I8Trap, llvm::NVPTXISD::Suld1DArrayV4I8Zero, llvm::NVPTXISD::Suld1DI16Clamp, llvm::NVPTXISD::Suld1DI16Trap, llvm::NVPTXISD::Suld1DI16Zero, llvm::NVPTXISD::Suld1DI32Clamp, llvm::NVPTXISD::Suld1DI32Trap, llvm::NVPTXISD::Suld1DI32Zero, llvm::NVPTXISD::Suld1DI64Clamp, llvm::NVPTXISD::Suld1DI64Trap, llvm::NVPTXISD::Suld1DI64Zero, llvm::NVPTXISD::Suld1DI8Clamp, llvm::NVPTXISD::Suld1DI8Trap, llvm::NVPTXISD::Suld1DI8Zero, llvm::NVPTXISD::Suld1DV2I16Clamp, llvm::NVPTXISD::Suld1DV2I16Trap, llvm::NVPTXISD::Suld1DV2I16Zero, llvm::NVPTXISD::Suld1DV2I32Clamp, llvm::NVPTXISD::Suld1DV2I32Trap, llvm::NVPTXISD::Suld1DV2I32Zero, llvm::NVPTXISD::Suld1DV2I64Clamp, llvm::NVPTXISD::Suld1DV2I64Trap, llvm::NVPTXISD::Suld1DV2I64Zero, llvm::NVPTXISD::Suld1DV2I8Clamp, llvm::NVPTXISD::Suld1DV2I8Trap, llvm::NVPTXISD::Suld1DV2I8Zero, llvm::NVPTXISD::Suld1DV4I16Clamp, llvm::NVPTXISD::Suld1DV4I16Trap, llvm::NVPTXISD::Suld1DV4I16Zero, llvm::NVPTXISD::Suld1DV4I32Clamp, llvm::NVPTXISD::Suld1DV4I32Trap, llvm::NVPTXISD::Suld1DV4I32Zero, llvm::NVPTXISD::Suld1DV4I8Clamp, llvm::NVPTXISD::Suld1DV4I8Trap, llvm::NVPTXISD::Suld1DV4I8Zero, llvm::NVPTXISD::Suld2DArrayI16Clamp, llvm::NVPTXISD::Suld2DArrayI16Trap, llvm::NVPTXISD::Suld2DArrayI16Zero, llvm::NVPTXISD::Suld2DArrayI32Clamp, llvm::NVPTXISD::Suld2DArrayI32Trap, llvm::NVPTXISD::Suld2DArrayI32Zero, llvm::NVPTXISD::Suld2DArrayI64Clamp, llvm::NVPTXISD::Suld2DArrayI64Trap, llvm::NVPTXISD::Suld2DArrayI64Zero, llvm::NVPTXISD::Suld2DArrayI8Clamp, llvm::NVPTXISD::Suld2DArrayI8Trap, llvm::NVPTXISD::Suld2DArrayI8Zero, llvm::NVPTXISD::Suld2DArrayV2I16Clamp, llvm::NVPTXISD::Suld2DArrayV2I16Trap, llvm::NVPTXISD::Suld2DArrayV2I16Zero, llvm::NVPTXISD::Suld2DArrayV2I32Clamp, llvm::NVPTXISD::Suld2DArrayV2I32Trap, llvm::NVPTXISD::Suld2DArrayV2I32Zero, llvm::NVPTXISD::Suld2DArrayV2I64Clamp, llvm::NVPTXISD::Suld2DArrayV2I64Trap, llvm::NVPTXISD::Suld2DArrayV2I64Zero, llvm::NVPTXISD::Suld2DArrayV2I8Clamp, llvm::NVPTXISD::Suld2DArrayV2I8Trap, llvm::NVPTXISD::Suld2DArrayV2I8Zero, llvm::NVPTXISD::Suld2DArrayV4I16Clamp, llvm::NVPTXISD::Suld2DArrayV4I16Trap, llvm::NVPTXISD::Suld2DArrayV4I16Zero, llvm::NVPTXISD::Suld2DArrayV4I32Clamp, llvm::NVPTXISD::Suld2DArrayV4I32Trap, llvm::NVPTXISD::Suld2DArrayV4I32Zero, llvm::NVPTXISD::Suld2DArrayV4I8Clamp, llvm::NVPTXISD::Suld2DArrayV4I8Trap, llvm::NVPTXISD::Suld2DArrayV4I8Zero, llvm::NVPTXISD::Suld2DI16Clamp, llvm::NVPTXISD::Suld2DI16Trap, llvm::NVPTXISD::Suld2DI16Zero, llvm::NVPTXISD::Suld2DI32Clamp, llvm::NVPTXISD::Suld2DI32Trap, llvm::NVPTXISD::Suld2DI32Zero, llvm::NVPTXISD::Suld2DI64Clamp, llvm::NVPTXISD::Suld2DI64Trap, llvm::NVPTXISD::Suld2DI64Zero, llvm::NVPTXISD::Suld2DI8Clamp, llvm::NVPTXISD::Suld2DI8Trap, llvm::NVPTXISD::Suld2DI8Zero, llvm::NVPTXISD::Suld2DV2I16Clamp, llvm::NVPTXISD::Suld2DV2I16Trap, llvm::NVPTXISD::Suld2DV2I16Zero, llvm::NVPTXISD::Suld2DV2I32Clamp, llvm::NVPTXISD::Suld2DV2I32Trap, llvm::NVPTXISD::Suld2DV2I32Zero, llvm::NVPTXISD::Suld2DV2I64Clamp, llvm::NVPTXISD::Suld2DV2I64Trap, llvm::NVPTXISD::Suld2DV2I64Zero, llvm::NVPTXISD::Suld2DV2I8Clamp, llvm::NVPTXISD::Suld2DV2I8Trap, llvm::NVPTXISD::Suld2DV2I8Zero, llvm::NVPTXISD::Suld2DV4I16Clamp, llvm::NVPTXISD::Suld2DV4I16Trap, llvm::NVPTXISD::Suld2DV4I16Zero, llvm::NVPTXISD::Suld2DV4I32Clamp, llvm::NVPTXISD::Suld2DV4I32Trap, llvm::NVPTXISD::Suld2DV4I32Zero, llvm::NVPTXISD::Suld2DV4I8Clamp, llvm::NVPTXISD::Suld2DV4I8Trap, llvm::NVPTXISD::Suld2DV4I8Zero, llvm::NVPTXISD::Suld3DI16Clamp, llvm::NVPTXISD::Suld3DI16Trap, llvm::NVPTXISD::Suld3DI16Zero, llvm::NVPTXISD::Suld3DI32Clamp, llvm::NVPTXISD::Suld3DI32Trap, llvm::NVPTXISD::Suld3DI32Zero, llvm::NVPTXISD::Suld3DI64Clamp, llvm::NVPTXISD::Suld3DI64Trap, llvm::NVPTXISD::Suld3DI64Zero, llvm::NVPTXISD::Suld3DI8Clamp, llvm::NVPTXISD::Suld3DI8Trap, llvm::NVPTXISD::Suld3DI8Zero, llvm::NVPTXISD::Suld3DV2I16Clamp, llvm::NVPTXISD::Suld3DV2I16Trap, llvm::NVPTXISD::Suld3DV2I16Zero, llvm::NVPTXISD::Suld3DV2I32Clamp, llvm::NVPTXISD::Suld3DV2I32Trap, llvm::NVPTXISD::Suld3DV2I32Zero, llvm::NVPTXISD::Suld3DV2I64Clamp, llvm::NVPTXISD::Suld3DV2I64Trap, llvm::NVPTXISD::Suld3DV2I64Zero, llvm::NVPTXISD::Suld3DV2I8Clamp, llvm::NVPTXISD::Suld3DV2I8Trap, llvm::NVPTXISD::Suld3DV2I8Zero, llvm::NVPTXISD::Suld3DV4I16Clamp, llvm::NVPTXISD::Suld3DV4I16Trap, llvm::NVPTXISD::Suld3DV4I16Zero, llvm::NVPTXISD::Suld3DV4I32Clamp, llvm::NVPTXISD::Suld3DV4I32Trap, llvm::NVPTXISD::Suld3DV4I32Zero, llvm::NVPTXISD::Suld3DV4I8Clamp, llvm::NVPTXISD::Suld3DV4I8Trap, llvm::NVPTXISD::Suld3DV4I8Zero, llvm::NVPTXISD::Tex1DArrayFloatFloat, llvm::NVPTXISD::Tex1DArrayFloatFloatGrad, llvm::NVPTXISD::Tex1DArrayFloatFloatLevel, llvm::NVPTXISD::Tex1DArrayFloatS32, llvm::NVPTXISD::Tex1DArrayS32Float, llvm::NVPTXISD::Tex1DArrayS32FloatGrad, llvm::NVPTXISD::Tex1DArrayS32FloatLevel, llvm::NVPTXISD::Tex1DArrayS32S32, llvm::NVPTXISD::Tex1DArrayU32Float, llvm::NVPTXISD::Tex1DArrayU32FloatGrad, llvm::NVPTXISD::Tex1DArrayU32FloatLevel, llvm::NVPTXISD::Tex1DArrayU32S32, llvm::NVPTXISD::Tex1DFloatFloat, llvm::NVPTXISD::Tex1DFloatFloatGrad, llvm::NVPTXISD::Tex1DFloatFloatLevel, llvm::NVPTXISD::Tex1DFloatS32, llvm::NVPTXISD::Tex1DS32Float, llvm::NVPTXISD::Tex1DS32FloatGrad, llvm::NVPTXISD::Tex1DS32FloatLevel, llvm::NVPTXISD::Tex1DS32S32, llvm::NVPTXISD::Tex1DU32Float, llvm::NVPTXISD::Tex1DU32FloatGrad, llvm::NVPTXISD::Tex1DU32FloatLevel, llvm::NVPTXISD::Tex1DU32S32, llvm::NVPTXISD::Tex2DArrayFloatFloat, llvm::NVPTXISD::Tex2DArrayFloatFloatGrad, llvm::NVPTXISD::Tex2DArrayFloatFloatLevel, llvm::NVPTXISD::Tex2DArrayFloatS32, llvm::NVPTXISD::Tex2DArrayS32Float, llvm::NVPTXISD::Tex2DArrayS32FloatGrad, llvm::NVPTXISD::Tex2DArrayS32FloatLevel, llvm::NVPTXISD::Tex2DArrayS32S32, llvm::NVPTXISD::Tex2DArrayU32Float, llvm::NVPTXISD::Tex2DArrayU32FloatGrad, llvm::NVPTXISD::Tex2DArrayU32FloatLevel, llvm::NVPTXISD::Tex2DArrayU32S32, llvm::NVPTXISD::Tex2DFloatFloat, llvm::NVPTXISD::Tex2DFloatFloatGrad, llvm::NVPTXISD::Tex2DFloatFloatLevel, llvm::NVPTXISD::Tex2DFloatS32, llvm::NVPTXISD::Tex2DS32Float, llvm::NVPTXISD::Tex2DS32FloatGrad, llvm::NVPTXISD::Tex2DS32FloatLevel, llvm::NVPTXISD::Tex2DS32S32, llvm::NVPTXISD::Tex2DU32Float, llvm::NVPTXISD::Tex2DU32FloatGrad, llvm::NVPTXISD::Tex2DU32FloatLevel, llvm::NVPTXISD::Tex2DU32S32, llvm::NVPTXISD::Tex3DFloatFloat, llvm::NVPTXISD::Tex3DFloatFloatGrad, llvm::NVPTXISD::Tex3DFloatFloatLevel, llvm::NVPTXISD::Tex3DFloatS32, llvm::NVPTXISD::Tex3DS32Float, llvm::NVPTXISD::Tex3DS32FloatGrad, llvm::NVPTXISD::Tex3DS32FloatLevel, llvm::NVPTXISD::Tex3DS32S32, llvm::NVPTXISD::Tex3DU32Float, llvm::NVPTXISD::Tex3DU32FloatGrad, llvm::NVPTXISD::Tex3DU32FloatLevel, llvm::NVPTXISD::Tex3DU32S32, llvm::NVPTXISD::TexCubeArrayFloatFloat, llvm::NVPTXISD::TexCubeArrayFloatFloatLevel, llvm::NVPTXISD::TexCubeArrayS32Float, llvm::NVPTXISD::TexCubeArrayS32FloatLevel, llvm::NVPTXISD::TexCubeArrayU32Float, llvm::NVPTXISD::TexCubeArrayU32FloatLevel, llvm::NVPTXISD::TexCubeFloatFloat, llvm::NVPTXISD::TexCubeFloatFloatLevel, llvm::NVPTXISD::TexCubeS32Float, llvm::NVPTXISD::TexCubeS32FloatLevel, llvm::NVPTXISD::TexCubeU32Float, llvm::NVPTXISD::TexCubeU32FloatLevel, llvm::NVPTXISD::TexUnified1DArrayFloatFloat, llvm::NVPTXISD::TexUnified1DArrayFloatFloatGrad, llvm::NVPTXISD::TexUnified1DArrayFloatFloatLevel, llvm::NVPTXISD::TexUnified1DArrayFloatS32, llvm::NVPTXISD::TexUnified1DArrayS32Float, llvm::NVPTXISD::TexUnified1DArrayS32FloatGrad, llvm::NVPTXISD::TexUnified1DArrayS32FloatLevel, llvm::NVPTXISD::TexUnified1DArrayS32S32, llvm::NVPTXISD::TexUnified1DArrayU32Float, llvm::NVPTXISD::TexUnified1DArrayU32FloatGrad, llvm::NVPTXISD::TexUnified1DArrayU32FloatLevel, llvm::NVPTXISD::TexUnified1DArrayU32S32, llvm::NVPTXISD::TexUnified1DFloatFloat, llvm::NVPTXISD::TexUnified1DFloatFloatGrad, llvm::NVPTXISD::TexUnified1DFloatFloatLevel, llvm::NVPTXISD::TexUnified1DFloatS32, llvm::NVPTXISD::TexUnified1DS32Float, llvm::NVPTXISD::TexUnified1DS32FloatGrad, llvm::NVPTXISD::TexUnified1DS32FloatLevel, llvm::NVPTXISD::TexUnified1DS32S32, llvm::NVPTXISD::TexUnified1DU32Float, llvm::NVPTXISD::TexUnified1DU32FloatGrad, llvm::NVPTXISD::TexUnified1DU32FloatLevel, llvm::NVPTXISD::TexUnified1DU32S32, llvm::NVPTXISD::TexUnified2DArrayFloatFloat, llvm::NVPTXISD::TexUnified2DArrayFloatFloatGrad, llvm::NVPTXISD::TexUnified2DArrayFloatFloatLevel, llvm::NVPTXISD::TexUnified2DArrayFloatS32, llvm::NVPTXISD::TexUnified2DArrayS32Float, llvm::NVPTXISD::TexUnified2DArrayS32FloatGrad, llvm::NVPTXISD::TexUnified2DArrayS32FloatLevel, llvm::NVPTXISD::TexUnified2DArrayS32S32, llvm::NVPTXISD::TexUnified2DArrayU32Float, llvm::NVPTXISD::TexUnified2DArrayU32FloatGrad, llvm::NVPTXISD::TexUnified2DArrayU32FloatLevel, llvm::NVPTXISD::TexUnified2DArrayU32S32, llvm::NVPTXISD::TexUnified2DFloatFloat, llvm::NVPTXISD::TexUnified2DFloatFloatGrad, llvm::NVPTXISD::TexUnified2DFloatFloatLevel, llvm::NVPTXISD::TexUnified2DFloatS32, llvm::NVPTXISD::TexUnified2DS32Float, llvm::NVPTXISD::TexUnified2DS32FloatGrad, llvm::NVPTXISD::TexUnified2DS32FloatLevel, llvm::NVPTXISD::TexUnified2DS32S32, llvm::NVPTXISD::TexUnified2DU32Float, llvm::NVPTXISD::TexUnified2DU32FloatGrad, llvm::NVPTXISD::TexUnified2DU32FloatLevel, llvm::NVPTXISD::TexUnified2DU32S32, llvm::NVPTXISD::TexUnified3DFloatFloat, llvm::NVPTXISD::TexUnified3DFloatFloatGrad, llvm::NVPTXISD::TexUnified3DFloatFloatLevel, llvm::NVPTXISD::TexUnified3DFloatS32, llvm::NVPTXISD::TexUnified3DS32Float, llvm::NVPTXISD::TexUnified3DS32FloatGrad, llvm::NVPTXISD::TexUnified3DS32FloatLevel, llvm::NVPTXISD::TexUnified3DS32S32, llvm::NVPTXISD::TexUnified3DU32Float, llvm::NVPTXISD::TexUnified3DU32FloatGrad, llvm::NVPTXISD::TexUnified3DU32FloatLevel, llvm::NVPTXISD::TexUnified3DU32S32, llvm::NVPTXISD::TexUnifiedCubeArrayFloatFloat, llvm::NVPTXISD::TexUnifiedCubeArrayFloatFloatLevel, llvm::NVPTXISD::TexUnifiedCubeArrayS32Float, llvm::NVPTXISD::TexUnifiedCubeArrayS32FloatLevel, llvm::NVPTXISD::TexUnifiedCubeArrayU32Float, llvm::NVPTXISD::TexUnifiedCubeArrayU32FloatLevel, llvm::NVPTXISD::TexUnifiedCubeFloatFloat, llvm::NVPTXISD::TexUnifiedCubeFloatFloatLevel, llvm::NVPTXISD::TexUnifiedCubeS32Float, llvm::NVPTXISD::TexUnifiedCubeS32FloatLevel, llvm::NVPTXISD::TexUnifiedCubeU32Float, llvm::NVPTXISD::TexUnifiedCubeU32FloatLevel, llvm::NVPTXISD::Tld4A2DFloatFloat, llvm::NVPTXISD::Tld4A2DS64Float, llvm::NVPTXISD::Tld4A2DU64Float, llvm::NVPTXISD::Tld4B2DFloatFloat, llvm::NVPTXISD::Tld4B2DS64Float, llvm::NVPTXISD::Tld4B2DU64Float, llvm::NVPTXISD::Tld4G2DFloatFloat, llvm::NVPTXISD::Tld4G2DS64Float, llvm::NVPTXISD::Tld4G2DU64Float, llvm::NVPTXISD::Tld4R2DFloatFloat, llvm::NVPTXISD::Tld4R2DS64Float, llvm::NVPTXISD::Tld4R2DU64Float, llvm::NVPTXISD::Tld4UnifiedA2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedA2DS64Float, llvm::NVPTXISD::Tld4UnifiedA2DU64Float, llvm::NVPTXISD::Tld4UnifiedB2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedB2DS64Float, llvm::NVPTXISD::Tld4UnifiedB2DU64Float, llvm::NVPTXISD::Tld4UnifiedG2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedG2DS64Float, llvm::NVPTXISD::Tld4UnifiedG2DU64Float, llvm::NVPTXISD::Tld4UnifiedR2DFloatFloat, llvm::NVPTXISD::Tld4UnifiedR2DS64Float, llvm::NVPTXISD::Tld4UnifiedR2DU64Float, and llvm::NVPTXISD::Wrapper.

| bool NVPTXTargetLowering::getTgtMemIntrinsic | ( | IntrinsicInfo & | , |

| const CallInst & | , | ||

| unsigned | |||

| ) | const [override, virtual] |

Given an intrinsic, checks if on the target the intrinsic will need to map to a MemIntrinsicNode (touches memory). If this is the case, it returns true and store the intrinsic information into the IntrinsicInfo that was passed to the function.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 3228 of file NVPTXISelLowering.cpp.

References llvm::TargetLoweringBase::IntrinsicInfo::align, llvm::MVT::f32, llvm::CallInst::getArgOperand(), getOpcForSurfaceInstr(), getOpcForTextureInstr(), llvm::TargetLoweringBase::getPointerTy(), llvm::Value::getType(), llvm::TargetLoweringBase::getValueType(), llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::INTRINSIC_W_CHAIN, llvm::TargetLoweringBase::IntrinsicInfo::memVT, llvm::TargetLoweringBase::IntrinsicInfo::offset, llvm::TargetLoweringBase::IntrinsicInfo::opc, llvm::TargetLoweringBase::IntrinsicInfo::ptrVal, llvm::TargetLoweringBase::IntrinsicInfo::readMem, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::TargetLoweringBase::IntrinsicInfo::vol, and llvm::TargetLoweringBase::IntrinsicInfo::writeMem.

| bool llvm::NVPTXTargetLowering::isFMAFasterThanFMulAndFAdd | ( | EVT | ) | const [inline, override, virtual] |

Return true if an FMA operation is faster than a pair of fmul and fadd instructions. fmuladd intrinsics will be expanded to FMAs when this method returns true, otherwise fmuladd is expanded to fmul + fadd.

NOTE: This may be called before legalization on types for which FMAs are not legal, but should return true if those types will eventually legalize to types that support FMAs. After legalization, it will only be called on types that support FMAs (via Legal or Custom actions)

Reimplemented from llvm::TargetLoweringBase.

Definition at line 508 of file NVPTXISelLowering.h.

| bool NVPTXTargetLowering::isLegalAddressingMode | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type Used to guide target specific optimizations, like loop strength reduction (LoopStrengthReduce.cpp) and memory optimization for address mode (CodeGenPrepare.cpp)

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type. Used to guide target specific optimizations, like loop strength reduction (LoopStrengthReduce.cpp) and memory optimization for address mode (CodeGenPrepare.cpp)

Reimplemented from llvm::TargetLoweringBase.

Definition at line 3700 of file NVPTXISelLowering.cpp.

References llvm::TargetLoweringBase::AddrMode::BaseGV, llvm::TargetLoweringBase::AddrMode::BaseOffs, llvm::TargetLoweringBase::AddrMode::HasBaseReg, and llvm::TargetLoweringBase::AddrMode::Scale.

| bool NVPTXTargetLowering::isTypeSupportedInIntrinsic | ( | MVT | VT | ) | const |

Definition at line 2516 of file NVPTXISelLowering.cpp.

References llvm::MVT::getVectorElementType(), llvm::TargetLoweringBase::isTypeLegal(), and llvm::MVT::isVector().

| void NVPTXTargetLowering::LowerAsmOperandForConstraint | ( | SDValue | Op, |

| std::string & | Constraint, | ||

| std::vector< SDValue > & | Ops, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops.

LowerAsmOperandForConstraint - Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops.

Reimplemented from llvm::TargetLowering.

Definition at line 2504 of file NVPTXISelLowering.cpp.

| SDValue NVPTXTargetLowering::LowerCall | ( | TargetLowering::CallLoweringInfo & | , |

| SmallVectorImpl< SDValue > & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower calls into the the specified DAG. The outgoing arguments to the call are described by the Outs array, and the values to be returned by the call are described by the Ins array. The implementation should fill in the InVals array with legal-type return values from the call, and return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 1034 of file NVPTXISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::ANY_EXTEND, llvm::c_str(), llvm::NVPTXISD::CallArg, llvm::NVPTXISD::CallArgBegin, llvm::NVPTXISD::CallArgEnd, llvm::TargetLowering::CallLoweringInfo::Callee, llvm::NVPTXISD::CallPrototype, llvm::NVPTXISD::CallVoid, llvm::TargetLowering::CallLoweringInfo::Chain, ComputePTXValueVTs(), llvm::ComputeValueVTs(), llvm::TargetLowering::CallLoweringInfo::CS, llvm::TargetLowering::CallLoweringInfo::DAG, llvm::NVPTXISD::DeclareParam, llvm::NVPTXISD::DeclareRet, llvm::NVPTXISD::DeclareRetParam, llvm::NVPTXISD::DeclareScalarParam, llvm::TargetLowering::CallLoweringInfo::DL, llvm::dyn_cast(), F(), llvm::TargetLowering::CallLoweringInfo::getArgs(), llvm::SelectionDAG::getCALLSEQ_END(), llvm::SelectionDAG::getCALLSEQ_START(), llvm::SelectionDAG::getConstant(), llvm::Function::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::SequentialType::getElementType(), llvm::MachineFunction::getFunction(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::ManagedStringPool::getManagedString(), llvm::NVPTXTargetMachine::getManagedStrPool(), llvm::SelectionDAG::getMemIntrinsicNode(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getNumRegisters(), llvm::TargetLoweringBase::getPointerTy(), getPrototype(), llvm::EVT::getSizeInBits(), llvm::NVPTXSubtarget::getSmVersion(), llvm::EVT::getStoreSizeInBits(), llvm::NVPTXTargetMachine::getSubtargetImpl(), llvm::SelectionDAG::getTargetExternalSymbol(), llvm::NVPTXSubtarget::getTargetLowering(), llvm::DataLayout::getTypeAllocSize(), llvm::DataLayout::getTypeAllocSizeInBits(), llvm::EVT::getTypeForEVT(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValue(), llvm::TargetLoweringBase::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, llvm::GreatestCommonDivisor64(), llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i8, llvm::MipsISD::Ins, llvm::TargetLowering::CallLoweringInfo::Ins, llvm::Type::isAggregateType(), llvm::EVT::isInteger(), llvm::Type::isIntegerTy(), llvm::Type::isSingleValueType(), llvm::TargetLowering::CallLoweringInfo::IsTailCall, llvm::Type::isVectorTy(), llvm::NVPTXISD::LastCallArg, llvm::NVPTXISD::LoadParam, llvm::NVPTXISD::LoadParamV2, llvm::NVPTXISD::LoadParamV4, nvTM, llvm::MVT::Other, llvm::TargetLowering::CallLoweringInfo::Outs, llvm::TargetLowering::CallLoweringInfo::OutVals, llvm::NVPTXISD::PrintCall, llvm::NVPTXISD::PrintCallUni, llvm::NVPTXISD::Prototype, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::TargetLowering::CallLoweringInfo::RetTy, llvm::ISD::SIGN_EXTEND, llvm::SmallVectorTemplateCommon< T >::size(), llvm::SmallVectorTemplateCommon< T, typename >::size(), llvm::NVPTXISD::StoreParam, llvm::NVPTXISD::StoreParamS32, llvm::NVPTXISD::StoreParamU32, llvm::NVPTXISD::StoreParamV2, llvm::NVPTXISD::StoreParamV4, llvm::ISD::TRUNCATE, uniqueCallSite, and llvm::ISD::ZERO_EXTEND.

| SDValue NVPTXTargetLowering::LowerFormalArguments | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::InputArg > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | , | ||

| SmallVectorImpl< SDValue > & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower the incoming (formal) arguments, described by the Ins array, into the specified DAG. The implementation should fill in the InVals array with legal-type argument values, and return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 2022 of file NVPTXISelLowering.cpp.

References llvm::ISD::ADD, llvm::ADDRESS_SPACE_PARAM, llvm::ISD::ANY_EXTEND, llvm::Function::arg_begin(), llvm::Function::arg_end(), llvm::Attribute::ByVal, ComputePTXValueVTs(), llvm::ISD::EXTRACT_VECTOR_ELT, F(), llvm::PointerType::get(), llvm::DataLayout::getABITypeAlignment(), llvm::Function::getAttributes(), llvm::SelectionDAG::getConstant(), llvm::Function::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::SelectionDAG::getExtLoad(), llvm::MachineFunction::getFunction(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::Constant::getNullValue(), llvm::TargetLoweringBase::getNumRegisters(), getParent(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRoot(), llvm::EVT::getSizeInBits(), llvm::NVPTXSubtarget::getSmVersion(), llvm::SelectionDAG::getSubtarget(), llvm::TargetSubtargetInfo::getTargetLowering(), llvm::DataLayout::getTypeAllocSize(), llvm::EVT::getTypeForEVT(), llvm::TargetLoweringBase::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::AttributeSet::hasAttribute(), I, llvm::MVT::i32, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::Type::isAggregateType(), llvm::isImageOrSamplerVal(), llvm::isKernelFunction(), llvm::Type::isVectorTy(), llvm::NVPTXISD::MoveParam, llvm::MVT::Other, P, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SDNode::setIROrder(), llvm::SelectionDAG::setRoot(), llvm::ISD::SEXTLOAD, llvm::SmallVectorTemplateCommon< T >::size(), llvm::ISD::TokenFactor, llvm::ISD::UNDEF, and llvm::ISD::ZEXTLOAD.

| SDValue NVPTXTargetLowering::LowerGlobalAddress | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 868 of file NVPTXISelLowering.cpp.

References llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getTargetGlobalAddress(), and llvm::NVPTXISD::Wrapper.

Referenced by LowerOperation().

| SDValue llvm::NVPTXTargetLowering::LowerGlobalAddress | ( | const GlobalValue * | GV, |

| int64_t | Offset, | ||

| SelectionDAG & | DAG | ||

| ) | const |

| SDValue NVPTXTargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

This callback is invoked for operations that are unsupported by the target, which are registered to use 'custom' lowering, and whose defined values are all legal. If the target has no operations that require custom lowering, it need not implement this. The default implementation of this aborts.

Reimplemented from llvm::TargetLowering.

Definition at line 1781 of file NVPTXISelLowering.cpp.

References llvm::ISD::BUILD_VECTOR, llvm::ISD::CONCAT_VECTORS, llvm::ISD::EXTRACT_SUBVECTOR, llvm::ISD::FRAMEADDR, llvm::SDValue::getOpcode(), llvm::ISD::GlobalAddress, llvm::ISD::INTRINSIC_W_CHAIN, llvm_unreachable, llvm::ISD::LOAD, LowerGlobalAddress(), llvm::ISD::RETURNADDR, llvm::ISD::SHL_PARTS, llvm::ISD::SRA_PARTS, llvm::ISD::SRL_PARTS, and llvm::ISD::STORE.

| SDValue NVPTXTargetLowering::LowerReturn | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::OutputArg > & | , | ||

| const SmallVectorImpl< SDValue > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower outgoing return values, described by the Outs array, into the specified DAG. The implementation should return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 2331 of file NVPTXISelLowering.cpp.

References llvm::ISD::ANY_EXTEND, ComputePTXValueVTs(), llvm::ISD::EXTRACT_VECTOR_ELT, F(), llvm::SelectionDAG::getConstant(), llvm::Function::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::MachineFunction::getFunction(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getMemIntrinsicNode(), llvm::SelectionDAG::getNode(), llvm::Function::getReturnType(), llvm::EVT::getSizeInBits(), llvm::NVPTXSubtarget::getSmVersion(), llvm::DataLayout::getTypeAllocSize(), llvm::DataLayout::getTypeAllocSizeInBits(), llvm::EVT::getTypeForEVT(), llvm::SelectionDAG::getUNDEF(), llvm::SDValue::getValueType(), llvm::TargetLoweringBase::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::getVectorVT(), llvm::SelectionDAG::getVTList(), llvm::MVT::i16, llvm::MVT::i32, llvm::Type::isIntegerTy(), llvm::EVT::isVector(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::NVPTXISD::RET_FLAG, llvm::SmallVectorTemplateCommon< T >::size(), llvm::SmallVectorTemplateCommon< T, typename >::size(), llvm::NVPTXISD::StoreRetval, llvm::NVPTXISD::StoreRetvalV2, llvm::NVPTXISD::StoreRetvalV4, and llvm::ISD::ZERO_EXTEND.

Member Data Documentation

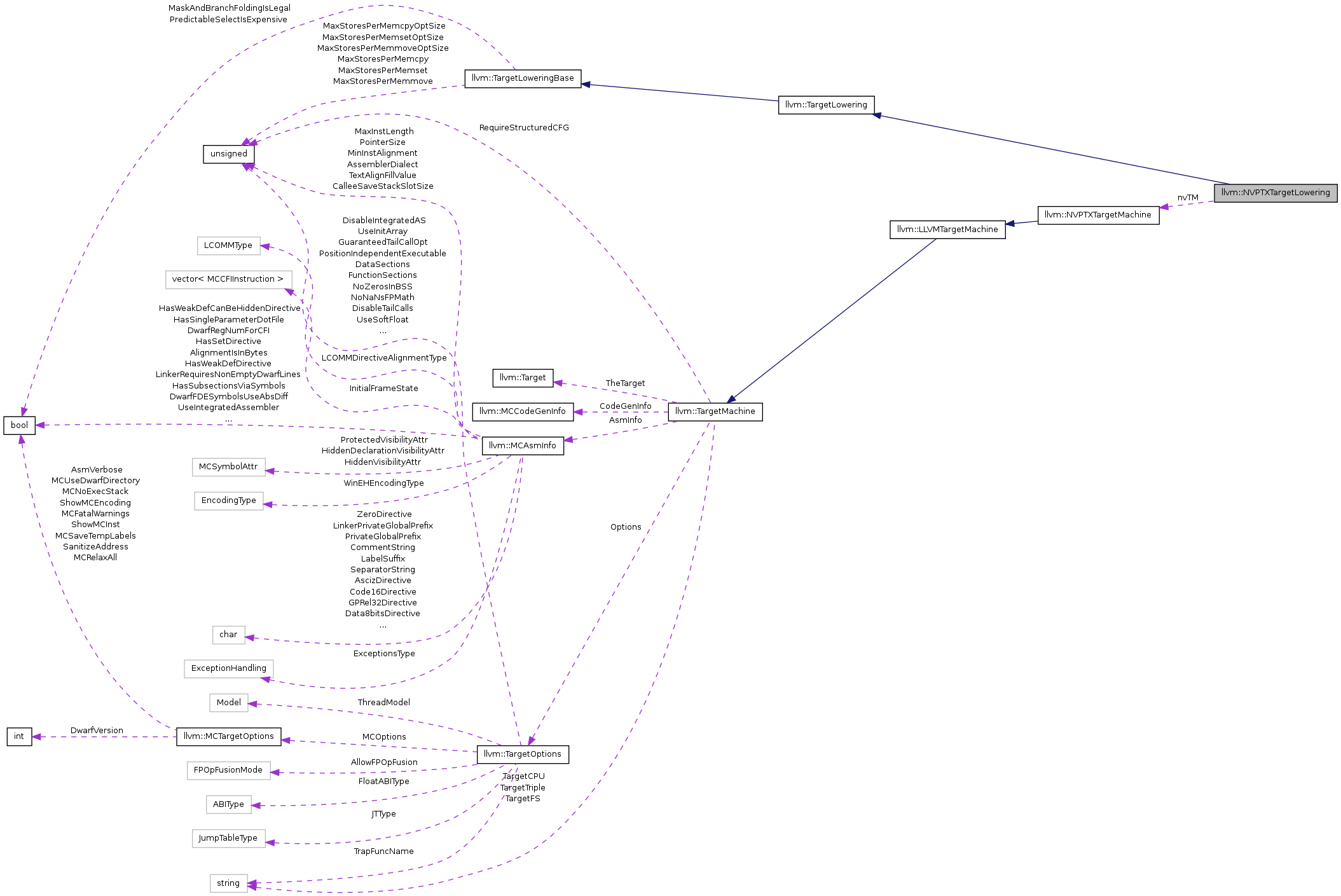

Definition at line 498 of file NVPTXISelLowering.h.

Referenced by LowerCall().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1