#include <SelectionDAGISel.h>

Detailed Description

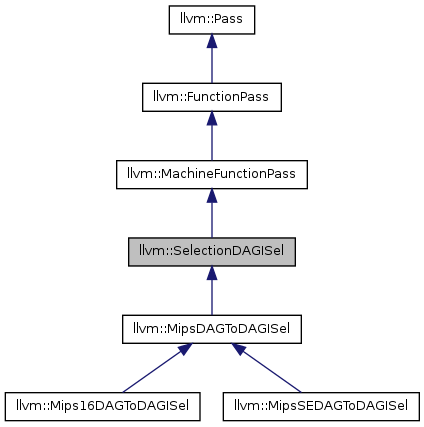

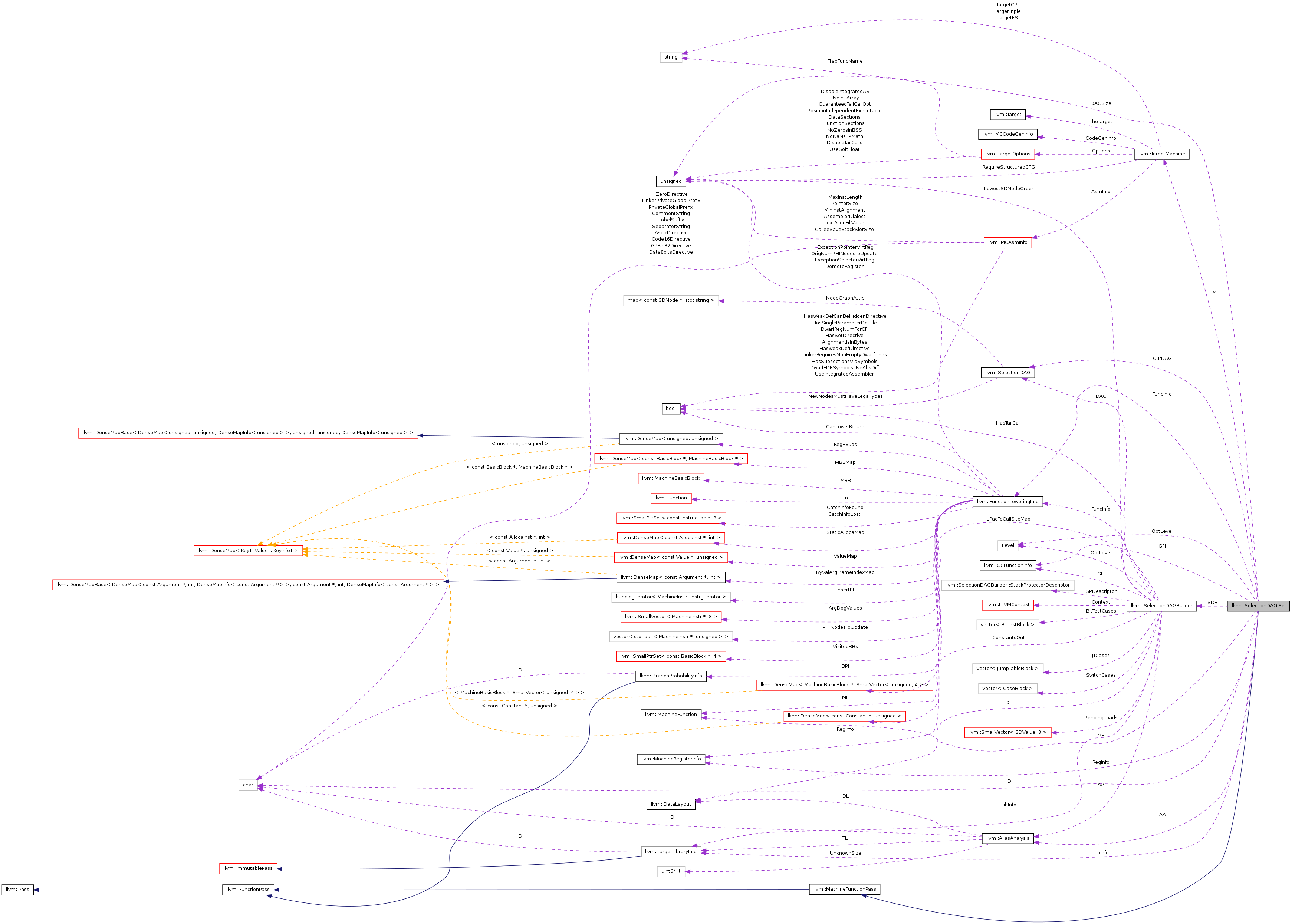

SelectionDAGISel - This is the common base class used for SelectionDAG-based pattern-matching instruction selectors.

Definition at line 42 of file SelectionDAGISel.h.

Member Enumeration Documentation

| anonymous enum |

- Enumerator:

OPFL_None OPFL_Chain OPFL_GlueInput OPFL_GlueOutput OPFL_MemRefs OPFL_Variadic0 OPFL_Variadic1 OPFL_Variadic2 OPFL_Variadic3 OPFL_Variadic4 OPFL_Variadic5 OPFL_Variadic6 OPFL_VariadicInfo

Definition at line 150 of file SelectionDAGISel.h.

- Enumerator:

Definition at line 105 of file SelectionDAGISel.h.

Constructor & Destructor Documentation

| SelectionDAGISel::SelectionDAGISel | ( | TargetMachine & | tm, |

| CodeGenOpt::Level | OL = CodeGenOpt::Default |

||

| ) | [explicit] |

| SelectionDAGISel::~SelectionDAGISel | ( | ) | [virtual] |

Definition at line 351 of file SelectionDAGISel.cpp.

Member Function Documentation

| bool SelectionDAGISel::CheckAndMask | ( | SDValue | LHS, |

| ConstantSDNode * | RHS, | ||

| int64_t | DesiredMaskS | ||

| ) | const |

CheckAndMask - The isel is trying to match something like (and X, 255). If the dag combiner simplified the 255, we still want to match. RHS is the actual value in the DAG on the RHS of an AND, and DesiredMaskS is the value specified in the .td file (e.g. 255).

Definition at line 1608 of file SelectionDAGISel.cpp.

References CurDAG, llvm::ConstantSDNode::getAPIntValue(), llvm::SDValue::getValueSizeInBits(), llvm::APInt::intersects(), and llvm::SelectionDAG::MaskedValueIsZero().

Referenced by CheckAndImm().

| virtual bool llvm::SelectionDAGISel::CheckComplexPattern | ( | SDNode * | Root, |

| SDNode * | Parent, | ||

| SDValue | N, | ||

| unsigned | PatternNo, | ||

| SmallVectorImpl< std::pair< SDValue, SDNode * > > & | Result | ||

| ) | [inline, virtual] |

Definition at line 228 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by SelectCodeCommon().

| virtual bool llvm::SelectionDAGISel::CheckNodePredicate | ( | SDNode * | N, |

| unsigned | PredNo | ||

| ) | const [inline, virtual] |

CheckNodePredicate - This function is generated by tblgen in the target. It runs node predicate number PredNo and returns true if it succeeds or false if it fails. The number is a private implementation detail to the code tblgen produces.

Definition at line 224 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by CheckNodePredicate(), and SelectCodeCommon().

| bool SelectionDAGISel::CheckOrMask | ( | SDValue | LHS, |

| ConstantSDNode * | RHS, | ||

| int64_t | DesiredMaskS | ||

| ) | const |

CheckOrMask - The isel is trying to match something like (or X, 255). If the dag combiner simplified the 255, we still want to match. RHS is the actual value in the DAG on the RHS of an OR, and DesiredMaskS is the value specified in the .td file (e.g. 255).

Definition at line 1637 of file SelectionDAGISel.cpp.

References llvm::SelectionDAG::computeKnownBits(), CurDAG, llvm::ConstantSDNode::getAPIntValue(), llvm::SDValue::getValueSizeInBits(), and llvm::APInt::intersects().

Referenced by CheckOrImm().

| virtual bool llvm::SelectionDAGISel::CheckPatternPredicate | ( | unsigned | PredNo | ) | const [inline, virtual] |

CheckPatternPredicate - This function is generated by tblgen in the target. It runs the specified pattern predicate and returns true if it succeeds or false if it fails. The number is a private implementation detail to the code tblgen produces.

Definition at line 216 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by CheckPatternPredicate(), and SelectCodeCommon().

| virtual void llvm::SelectionDAGISel::EmitFunctionEntryCode | ( | ) | [inline, virtual] |

Definition at line 68 of file SelectionDAGISel.h.

| void SelectionDAGISel::getAnalysisUsage | ( | AnalysisUsage & | AU | ) | const [override, virtual] |

getAnalysisUsage - Subclasses that override getAnalysisUsage must call this.

For MachineFunctionPasses, calling AU.preservesCFG() indicates that the pass does not modify the MachineBasicBlock CFG.

Reimplemented from llvm::MachineFunctionPass.

Definition at line 357 of file SelectionDAGISel.cpp.

References llvm::AnalysisUsage::addPreserved(), llvm::AnalysisUsage::addRequired(), llvm::CodeGenOpt::None, OptLevel, and UseMBPI.

| static int llvm::SelectionDAGISel::getNumFixedFromVariadicInfo | ( | unsigned | Flags | ) | [inline, static] |

getNumFixedFromVariadicInfo - Transform an EmitNode flags word into the number of fixed arity values that should be skipped when copying from the root.

Definition at line 170 of file SelectionDAGISel.h.

References OPFL_VariadicInfo.

Referenced by SelectCodeCommon().

| const TargetLowering* llvm::SelectionDAGISel::getTargetLowering | ( | ) | const [inline] |

Definition at line 60 of file SelectionDAGISel.h.

References llvm::TargetMachine::getSubtargetImpl(), llvm::TargetSubtargetInfo::getTargetLowering(), and TM.

Referenced by llvm::createDefaultScheduler(), llvm::createHybridListDAGScheduler(), llvm::createILPListDAGScheduler(), llvm::MipsDAGToDAGISel::getGlobalBaseReg(), IsPredicateKnownToFail(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), and SelectCodeCommon().

| bool SelectionDAGISel::IsLegalToFold | ( | SDValue | N, |

| SDNode * | U, | ||

| SDNode * | Root, | ||

| CodeGenOpt::Level | OptLevel, | ||

| bool | IgnoreChains = false |

||

| ) | [static] |

IsLegalToFold - Returns true if the specific operand node N of U can be folded during instruction selection that starts at Root. FIXME: This is a static member function because the MSP430/X86 targets, which uses it during isel. This could become a proper member.

IsLegalToFold - Returns true if the specific operand node N of U can be folded during instruction selection that starts at Root.

Definition at line 1779 of file SelectionDAGISel.cpp.

References findGlueUse(), findNonImmUse(), llvm::SDValue::getNode(), llvm::SDNode::getNumValues(), llvm::SDNode::getValueType(), llvm::MVT::Glue, and llvm::CodeGenOpt::None.

Referenced by SelectCodeCommon().

| bool SelectionDAGISel::IsProfitableToFold | ( | SDValue | N, |

| SDNode * | U, | ||

| SDNode * | Root | ||

| ) | const [virtual] |

IsProfitableToFold - Returns true if it's profitable to fold the specific operand node N of U during instruction selection that starts at Root.

Definition at line 1771 of file SelectionDAGISel.cpp.

References llvm::SDValue::hasOneUse(), llvm::CodeGenOpt::None, and OptLevel.

Referenced by SelectCodeCommon().

| virtual void llvm::SelectionDAGISel::PostprocessISelDAG | ( | ) | [inline, virtual] |

PostprocessISelDAG() - This hook allows the target to hack on the graph right after selection.

Definition at line 76 of file SelectionDAGISel.h.

| virtual void llvm::SelectionDAGISel::PreprocessISelDAG | ( | ) | [inline, virtual] |

PreprocessISelDAG - This hook allows targets to hack on the graph before instruction selection starts.

Definition at line 72 of file SelectionDAGISel.h.

| void llvm::SelectionDAGISel::ReplaceUses | ( | SDValue | F, |

| SDValue | T | ||

| ) | [inline, protected] |

ReplaceUses - replace all uses of the old node F with the use of the new node T.

Definition at line 182 of file SelectionDAGISel.h.

References CurDAG, and llvm::SelectionDAG::ReplaceAllUsesOfValueWith().

| void llvm::SelectionDAGISel::ReplaceUses | ( | const SDValue * | F, |

| const SDValue * | T, | ||

| unsigned | Num | ||

| ) | [inline, protected] |

ReplaceUses - replace all uses of the old nodes F with the use of the new nodes T.

Definition at line 188 of file SelectionDAGISel.h.

References CurDAG, and llvm::SelectionDAG::ReplaceAllUsesOfValuesWith().

| void llvm::SelectionDAGISel::ReplaceUses | ( | SDNode * | F, |

| SDNode * | T | ||

| ) | [inline, protected] |

ReplaceUses - replace all uses of the old node F with the use of the new node T.

Definition at line 194 of file SelectionDAGISel.h.

References CurDAG, and llvm::SelectionDAG::ReplaceAllUsesWith().

| bool SelectionDAGISel::runOnMachineFunction | ( | MachineFunction & | MF | ) | [override, virtual] |

runOnMachineFunction - This method must be overloaded to perform the desired machine code transformation or analysis.

Implements llvm::MachineFunctionPass.

Reimplemented in llvm::MipsDAGToDAGISel.

Definition at line 406 of file SelectionDAGISel.cpp.

References AA, llvm::FunctionLoweringInfo::ArgDbgValues, llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::begin(), llvm::MachineBasicBlock::begin(), llvm::MachineFunction::begin(), llvm::FunctionLoweringInfo::BPI, llvm::BuildMI(), llvm::Function::callsFunctionThatReturnsTwice(), llvm::FunctionLoweringInfo::clear(), llvm::MachineRegisterInfo::constrainRegClass(), CurDAG, llvm::TargetOpcode::DBG_VALUE, llvm::dbgs(), DEBUG, llvm::tgtok::Def, llvm::MachineRegisterInfo::EmitLiveInCopies(), llvm::SmallVectorBase::empty(), llvm::TargetOptions::EnableFastISel, EnableFastISelAbort, EnableFastISelVerbose, llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::end(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::find(), llvm::MachineRegisterInfo::freezeReservedRegs(), FuncInfo, llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::MachineFunction::getFrameInfo(), llvm::TargetRegisterInfo::getFrameRegister(), llvm::MachineFunction::getFunction(), llvm::MachineOperand::getImm(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::Value::getName(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetSubtargetInfo::getTargetLowering(), llvm::MachineRegisterInfo::getVRegDef(), GFI, llvm::MachineFrameInfo::hasCalls(), llvm::Function::hasFnAttribute(), llvm::Function::hasGC(), I, llvm::SelectionDAG::init(), llvm::SelectionDAGBuilder::init(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::insert(), llvm::MachineBasicBlock::insert(), llvm::MachineBasicBlock::insertAfter(), llvm::MCInstrDesc::isCall(), llvm::MachineInstr::isCopy(), llvm::MachineInstr::isDebugValue(), llvm::MachineOperand::isFI(), llvm::MachineInstr::isIndirectDebugValue(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MCInstrDesc::isReturn(), llvm::TargetRegisterInfo::isVirtualRegister(), LI, LibInfo, llvm::MachineRegisterInfo::livein_begin(), llvm::MachineRegisterInfo::livein_end(), MF, llvm::AArch64CC::MI, llvm::CodeGenOpt::None, llvm::Attribute::OptimizeNone, llvm::TargetMachine::Options, OptLevel, llvm::FunctionLoweringInfo::RegFixups, RegInfo, llvm::MachineRegisterInfo::replaceRegWith(), llvm::TargetMachine::resetTargetOptions(), SDB, llvm::FunctionLoweringInfo::set(), llvm::MachineFrameInfo::setHasCalls(), llvm::MachineFunction::setHasInlineAsm(), llvm::SmallVectorTemplateCommon< T, typename >::size(), SplitCriticalSideEffectEdges(), TII, TM, llvm::MachineRegisterInfo::use_instr_begin(), llvm::MachineRegisterInfo::use_instr_end(), UseMBPI, and llvm::TargetRegisterInfo::virtReg2Index().

| virtual SDValue llvm::SelectionDAGISel::RunSDNodeXForm | ( | SDValue | V, |

| unsigned | XFormNo | ||

| ) | [inline, virtual] |

Definition at line 234 of file SelectionDAGISel.h.

References llvm_unreachable.

Referenced by SelectCodeCommon().

| virtual SDNode* llvm::SelectionDAGISel::Select | ( | SDNode * | N | ) | [pure virtual] |

Select - Main hook targets implement to select a node.

| SDNode * SelectionDAGISel::SelectCodeCommon | ( | SDNode * | NodeToMatch, |

| const unsigned char * | MatcherTable, | ||

| unsigned | TableSize | ||

| ) |

Definition at line 2441 of file SelectionDAGISel.cpp.

References llvm::MachineFunction::allocateMemRefsArray(), llvm::ISD::AssertSext, llvm::ISD::AssertZext, llvm::SmallVectorTemplateCommon< T >::back(), llvm::ISD::BasicBlock, llvm::SmallVectorTemplateCommon< T >::begin(), CheckAndImm(), CheckChildInteger(), CheckChildSame(), CheckChildType(), CheckComplexPattern(), CheckCondCode(), CheckInteger(), CheckNodePredicate(), CheckOpcode(), CheckOrImm(), CheckPatternPredicate(), CheckSame(), CheckType(), CheckValueType(), llvm::SmallVectorImpl< T >::clear(), llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::ISD::CopyFromReg, llvm::ISD::CopyToReg, CurDAG, llvm::dbgs(), DEBUG, llvm::ISD::DELETED_NODE, llvm::SDNode::dump(), llvm::ISD::EH_LABEL, llvm::SmallVectorBase::empty(), llvm::SmallVectorTemplateCommon< T >::end(), llvm::ISD::EntryToken, llvm::MCInstrInfo::get(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getConstantFP(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getEntryNode(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::SelectionDAG::getMachineNode(), llvm::SDValue::getNode(), getNumFixedFromVariadicInfo(), llvm::SDValue::getNumOperands(), llvm::SDNode::getNumOperands(), llvm::SDNode::getNumValues(), llvm::SDValue::getOpcode(), llvm::SDNode::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::EVT::getSizeInBits(), llvm::TargetMachine::getSubtargetImpl(), llvm::SelectionDAG::getTargetConstant(), getTargetLowering(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), GetVBR(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, HandleMergeInputChains(), llvm::ISD::HANDLENODE, I, llvm::ISD::INLINEASM, llvm::MVT::iPTR, IsLegalToFold(), llvm::SDNode::isMachineOpcode(), IsPredicateKnownToFail(), IsProfitableToFold(), llvm::ISD::LIFETIME_END, llvm::ISD::LIFETIME_START, llvm::MCInstrDesc::mayLoad(), llvm::MCInstrDesc::mayStore(), llvm::ISD::MDNODE_SDNODE, MF, OPC_CaptureGlueInput, OPC_CheckAndImm, OPC_CheckChild0Integer, OPC_CheckChild0Same, OPC_CheckChild0Type, OPC_CheckChild1Integer, OPC_CheckChild1Same, OPC_CheckChild1Type, OPC_CheckChild2Integer, OPC_CheckChild2Same, OPC_CheckChild2Type, OPC_CheckChild3Integer, OPC_CheckChild3Same, OPC_CheckChild3Type, OPC_CheckChild4Integer, OPC_CheckChild4Type, OPC_CheckChild5Type, OPC_CheckChild6Type, OPC_CheckChild7Type, OPC_CheckComplexPat, OPC_CheckCondCode, OPC_CheckFoldableChainNode, OPC_CheckInteger, OPC_CheckOpcode, OPC_CheckOrImm, OPC_CheckPatternPredicate, OPC_CheckPredicate, OPC_CheckSame, OPC_CheckType, OPC_CheckValueType, OPC_CompleteMatch, OPC_EmitConvertToTarget, OPC_EmitCopyToReg, OPC_EmitInteger, OPC_EmitMergeInputChains, OPC_EmitMergeInputChains1_0, OPC_EmitMergeInputChains1_1, OPC_EmitNode, OPC_EmitNodeXForm, OPC_EmitRegister, OPC_EmitRegister2, OPC_MarkGlueResults, OPC_MorphNodeTo, OPC_MoveChild, OPC_MoveParent, OPC_RecordChild0, OPC_RecordChild1, OPC_RecordChild2, OPC_RecordChild3, OPC_RecordChild4, OPC_RecordChild5, OPC_RecordChild6, OPC_RecordChild7, OPC_RecordMemRef, OPC_RecordNode, OPC_Scope, OPC_SwitchOpcode, OPC_SwitchType, OPFL_Chain, OPFL_GlueInput, OPFL_MemRefs, OPFL_VariadicInfo, OptLevel, llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::pop_back(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::ISD::READ_REGISTER, llvm::ISD::Register, llvm::ISD::RegisterMask, llvm::SelectionDAG::ReplaceAllUsesOfValueWith(), llvm::SmallVectorImpl< T >::resize(), RunSDNodeXForm(), llvm::SDNode::setNodeId(), llvm::MVT::SimpleTy, llvm::SmallVectorTemplateCommon< T >::size(), llvm::ISD::TargetBlockAddress, llvm::ISD::TargetConstant, llvm::ISD::TargetConstantFP, llvm::ISD::TargetConstantPool, llvm::ISD::TargetExternalSymbol, llvm::ISD::TargetFrameIndex, llvm::ISD::TargetGlobalAddress, llvm::ISD::TargetGlobalTLSAddress, llvm::ISD::TargetJumpTable, TM, llvm::ISD::TokenFactor, llvm::ISD::UNDEF, llvm::SDNode::use_empty(), and llvm::ISD::WRITE_REGISTER.

| virtual bool llvm::SelectionDAGISel::SelectInlineAsmMemoryOperand | ( | const SDValue & | Op, |

| char | ConstraintCode, | ||

| std::vector< SDValue > & | OutOps | ||

| ) | [inline, virtual] |

SelectInlineAsmMemoryOperand - Select the specified address as a target addressing mode, according to the specified constraint code. If this does not match or is not implemented, return true. The resultant operands (which will appear in the machine instruction) should be added to the OutOps vector.

Definition at line 86 of file SelectionDAGISel.h.

Referenced by SelectInlineAsmMemoryOperands().

| void SelectionDAGISel::SelectInlineAsmMemoryOperands | ( | std::vector< SDValue > & | Ops | ) | [protected] |

SelectInlineAsmMemoryOperands - Calls to this are automatically generated by tblgen. Others should not call it.

Definition at line 1671 of file SelectionDAGISel.cpp.

References CurDAG, llvm::InlineAsm::getFlagWord(), llvm::InlineAsm::getNumOperandRegisters(), llvm::SelectionDAG::getTargetConstant(), llvm::MVT::Glue, llvm::MVT::i32, llvm::InlineAsm::isMemKind(), llvm::InlineAsm::Kind_Mem, llvm::InlineAsm::Op_AsmString, llvm::InlineAsm::Op_ExtraInfo, llvm::InlineAsm::Op_FirstOperand, llvm::InlineAsm::Op_InputChain, llvm::InlineAsm::Op_MDNode, llvm::report_fatal_error(), SelectInlineAsmMemoryOperand(), and std::swap().

Member Data Documentation

Definition at line 51 of file SelectionDAGISel.h.

Referenced by llvm::createVLIWDAGScheduler(), and runOnMachineFunction().

Definition at line 49 of file SelectionDAGISel.h.

Referenced by CheckAndMask(), CheckOrMask(), llvm::MipsDAGToDAGISel::getGlobalBaseReg(), ReplaceUses(), runOnMachineFunction(), SelectCodeCommon(), SelectInlineAsmMemoryOperands(), and ~SelectionDAGISel().

unsigned llvm::SelectionDAGISel::DAGSize [protected] |

DAGSize - Size of DAG being instruction selected.

Definition at line 178 of file SelectionDAGISel.h.

Definition at line 46 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction(), and ~SelectionDAGISel().

Definition at line 52 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

char SelectionDAGISel::ID = 0 [static] |

Definition at line 54 of file SelectionDAGISel.h.

Referenced by initializePassOnce().

Definition at line 45 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

Definition at line 47 of file SelectionDAGISel.h.

Referenced by llvm::createBURRListDAGScheduler(), llvm::createDAGLinearizer(), llvm::createFastDAGScheduler(), llvm::createHybridListDAGScheduler(), llvm::createILPListDAGScheduler(), llvm::createSourceListDAGScheduler(), llvm::createVLIWDAGScheduler(), llvm::MipsDAGToDAGISel::getGlobalBaseReg(), llvm::ResourcePriorityQueue::ResourcePriorityQueue(), runOnMachineFunction(), and SelectCodeCommon().

Definition at line 53 of file SelectionDAGISel.h.

Referenced by getAnalysisUsage(), IsProfitableToFold(), runOnMachineFunction(), and SelectCodeCommon().

Definition at line 48 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction().

Definition at line 50 of file SelectionDAGISel.h.

Referenced by runOnMachineFunction(), and ~SelectionDAGISel().

Definition at line 44 of file SelectionDAGISel.h.

Referenced by llvm::createBURRListDAGScheduler(), llvm::createDefaultScheduler(), llvm::createHybridListDAGScheduler(), llvm::createILPListDAGScheduler(), llvm::createSourceListDAGScheduler(), getTargetLowering(), llvm::MipsDAGToDAGISel::runOnMachineFunction(), runOnMachineFunction(), and SelectCodeCommon().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1