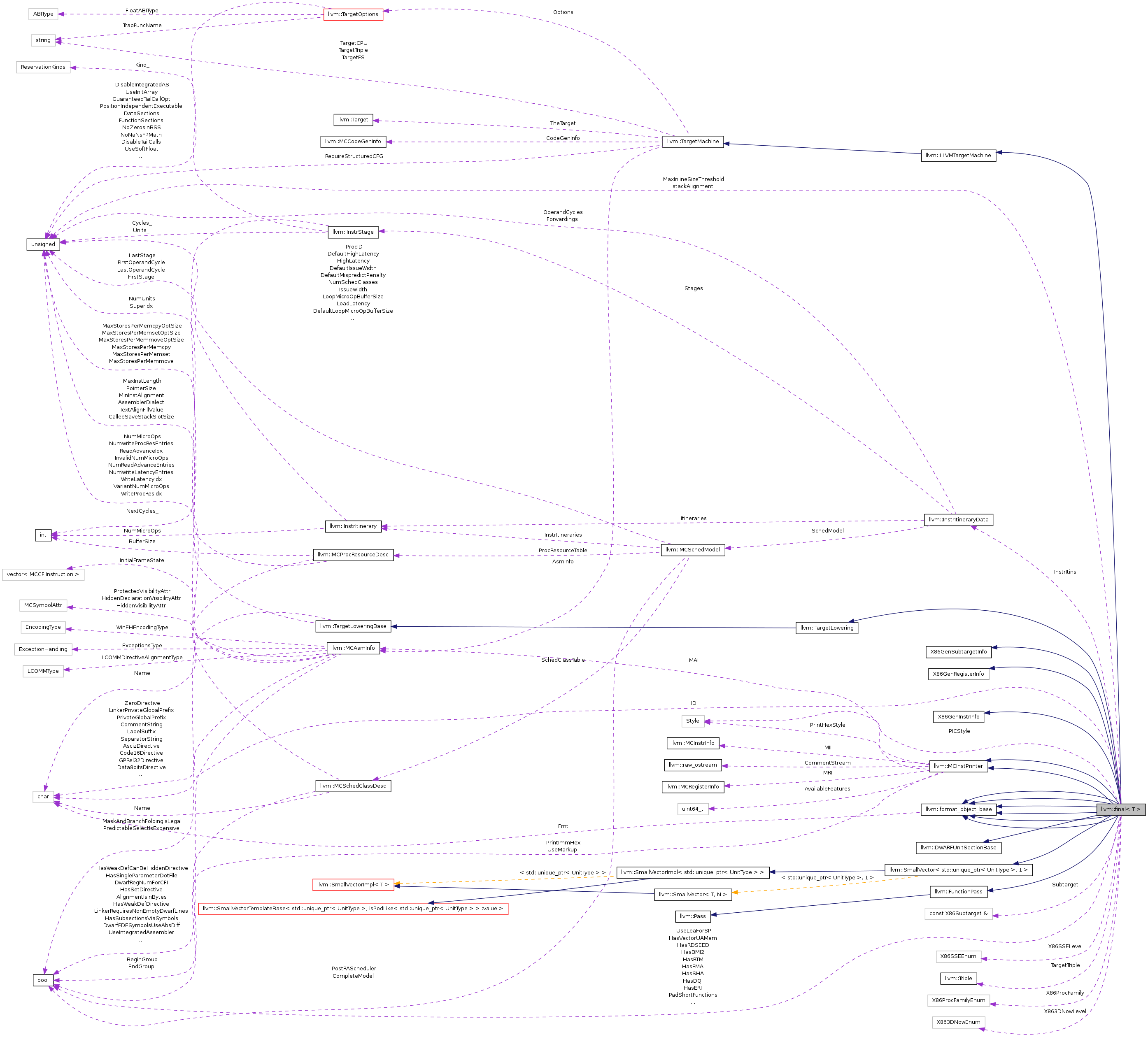

Concrete instance of DWARFUnitSection, specialized for one Unit type. More...

#include <FunctionTargetTransformInfo.h>

Detailed Description

template<typename T>

class llvm::final< T >

Concrete instance of DWARFUnitSection, specialized for one Unit type.

These are templated helper classes used by the format function that capture the object to be formated and the format string. When actually printed, this synthesizes the string into a temporary buffer provided and returns whether or not it is big enough.

Definition at line 23 of file FunctionTargetTransformInfo.h.

Member Typedef Documentation

| typedef UnitVector::iterator llvm::final< T >::iterator |

Reimplemented from llvm::SmallVectorImpl< std::unique_ptr< UnitType > >.

Definition at line 65 of file DWARFUnit.h.

| typedef llvm::iterator_range<typename UnitVector::iterator> llvm::final< T >::iterator_range |

Definition at line 66 of file DWARFUnit.h.

| typedef llvm::SmallVectorImpl<std::unique_ptr<UnitType> > llvm::final< T >::UnitVector |

Definition at line 64 of file DWARFUnit.h.

Member Enumeration Documentation

enum llvm::final::X863DNowEnum [protected] |

Definition at line 53 of file X86Subtarget.h.

enum llvm::final::X86ProcFamilyEnum [protected] |

Definition at line 57 of file X86Subtarget.h.

enum llvm::final::X86SSEEnum [protected] |

Definition at line 49 of file X86Subtarget.h.

Member Function Documentation

| void llvm::final< T >::addAnalysisPasses | ( | PassManagerBase & | PM | ) | [override, virtual] |

Register X86 analysis passes with a pass manager.

Reimplemented from llvm::LLVMTargetMachine.

| bool llvm::final< T >::allowsMisalignedMemoryAccesses | ( | EVT | VT, |

| unsigned | AS, | ||

| unsigned | Align, | ||

| bool * | Fast | ||

| ) | const [override, virtual] |

allowsMisalignedMemoryAccesses - Returns true if the target allows unaligned memory accesses. of the specified type. Returns whether it is "fast" by reference in the second argument.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::allowTruncateForTailCall | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if a truncation from Ty1 to Ty2 is permitted when deciding whether a call is in tail position. Typically this means that both results would be assigned to the same register or stack slot, but it could mean the target performs adequate checks of its own before proceeding with the tail call.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::AnalyzeBranch | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock *& | TBB, | ||

| MachineBasicBlock *& | FBB, | ||

| SmallVectorImpl< MachineOperand > & | Cond, | ||

| bool | AllowModify | ||

| ) | const [override] |

| bool llvm::final< T >::analyzeCompare | ( | const MachineInstr * | MI, |

| unsigned & | SrcReg, | ||

| unsigned & | SrcReg2, | ||

| int & | CmpMask, | ||

| int & | CmpValue | ||

| ) | const [override] |

analyzeCompare - For a comparison instruction, return the source registers in SrcReg and SrcReg2 if having two register operands, and the value it compares against in CmpValue. Return true if the comparison instruction can be analyzed.

| bool llvm::final< T >::areLoadsFromSameBasePtr | ( | SDNode * | Load1, |

| SDNode * | Load2, | ||

| int64_t & | Offset1, | ||

| int64_t & | Offset2 | ||

| ) | const [override] |

areLoadsFromSameBasePtr - This is used by the pre-regalloc scheduler to determine if two loads are loading from the same base address. It should only return true if the base pointers are the same and the only differences between the two addresses are the offset. It also returns the offsets by reference.

| void llvm::final< T >::breakPartialRegDependency | ( | MachineBasicBlock::iterator | MI, |

| unsigned | OpNum, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

| SDValue llvm::final< T >::BuildFILD | ( | SDValue | Op, |

| EVT | SrcVT, | ||

| SDValue | Chain, | ||

| SDValue | StackSlot, | ||

| SelectionDAG & | DAG | ||

| ) | const |

| bool llvm::final< T >::callRegIndirect | ( | ) | const [inline] |

Definition at line 368 of file X86Subtarget.h.

| bool llvm::final< T >::canFoldMemoryOperand | ( | const MachineInstr * | , |

| const SmallVectorImpl< unsigned > & | |||

| ) | const [override] |

canFoldMemoryOperand - Returns true if the specified load / store is folding is possible.

| bool llvm::final< T >::canInsertSelect | ( | const MachineBasicBlock & | , |

| const SmallVectorImpl< MachineOperand > & | Cond, | ||

| unsigned | , | ||

| unsigned | , | ||

| int & | , | ||

| int & | , | ||

| int & | |||

| ) | const [override] |

| bool llvm::final< T >::canRealignStack | ( | const MachineFunction & | MF | ) | const |

| unsigned char llvm::final< T >::ClassifyBlockAddressReference | ( | ) | const |

ClassifyBlockAddressReference - Classify a blockaddress reference for the current subtarget according to how we should reference it in a non-pcrel context.

| unsigned char llvm::final< T >::ClassifyGlobalReference | ( | const GlobalValue * | GV, |

| const TargetMachine & | TM | ||

| ) | const |

ClassifyGlobalReference - Classify a global variable reference for the current subtarget according to how we should reference it in a non-pcrel context.

| bool llvm::final< T >::classifyLEAReg | ( | MachineInstr * | MI, |

| const MachineOperand & | Src, | ||

| unsigned | LEAOpcode, | ||

| bool | AllowSP, | ||

| unsigned & | NewSrc, | ||

| bool & | isKill, | ||

| bool & | isUndef, | ||

| MachineOperand & | ImplicitOp | ||

| ) | const |

Given an operand within a MachineInstr, insert preceding code to put it into the right format for a particular kind of LEA instruction. This may involve using an appropriate super-register instead (with an implicit use of the original) or creating a new virtual register and inserting COPY instructions to get the data into the right class.

Reference parameters are set to indicate how caller should add this operand to the LEA instruction.

| MachineInstr* llvm::final< T >::commuteInstruction | ( | MachineInstr * | MI, |

| bool | NewMI | ||

| ) | const [override] |

commuteInstruction - We have a few instructions that must be hacked on to commute them.

| void llvm::final< T >::computeKnownBitsForTargetNode | ( | const SDValue | Op, |

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [override, virtual] |

computeKnownBitsForTargetNode - Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

Reimplemented from llvm::TargetLowering.

| unsigned llvm::final< T >::ComputeNumSignBitsForTargetNode | ( | SDValue | Op, |

| const SelectionDAG & | DAG, | ||

| unsigned | Depth | ||

| ) | const [override, virtual] |

This method can be implemented by targets that want to expose additional information about sign bits to the DAG Combiner.

ComputeNumSignBitsForTargetNode - This method can be implemented by targets that want to expose additional information about sign bits to the DAG Combiner.

Reimplemented from llvm::TargetLowering.

| MachineInstr* llvm::final< T >::convertToThreeAddress | ( | MachineFunction::iterator & | MFI, |

| MachineBasicBlock::iterator & | MBBI, | ||

| LiveVariables * | LV | ||

| ) | const [override] |

convertToThreeAddress - This method must be implemented by targets that set the M_CONVERTIBLE_TO_3_ADDR flag. When this flag is set, the target may be able to convert a two-address instruction into a true three-address instruction on demand. This allows the X86 target (for example) to convert ADD and SHL instructions into LEA instructions if they would require register copies due to two-addressness.

This method returns a null pointer if the transformation cannot be performed, otherwise it returns the new instruction.

| void llvm::final< T >::copyPhysReg | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| DebugLoc | DL, | ||

| unsigned | DestReg, | ||

| unsigned | SrcReg, | ||

| bool | KillSrc | ||

| ) | const [override] |

| FastISel* llvm::final< T >::createFastISel | ( | FunctionLoweringInfo & | funcInfo, |

| const TargetLibraryInfo * | libInfo | ||

| ) | const [override, virtual] |

createFastISel - This method returns a target specific FastISel object, or null if the target does not support "fast" ISel.

Reimplemented from llvm::TargetLowering.

| TargetPassConfig* llvm::final< T >::createPassConfig | ( | PassManagerBase & | PM | ) | [override, virtual] |

createPassConfig - Create a pass configuration object to be used by addPassToEmitX methods for generating a pipeline of CodeGen passes.

createPassConfig - Create a pass configuration object to be used by addPassToEmitX methods for generating a pipeline of CodeGen passes.

Targets may override this to extend TargetPassConfig.

Reimplemented from llvm::LLVMTargetMachine.

| void llvm::final< T >::eliminateFrameIndex | ( | MachineBasicBlock::iterator | MI, |

| int | SPAdj, | ||

| unsigned | FIOperandNum, | ||

| RegScavenger * | RS = nullptr |

||

| ) | const [override] |

| MachineBasicBlock* llvm::final< T >::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::TargetLowering.

| bool llvm::final< T >::enableEarlyIfConversion | ( | ) | const [override] |

| bool llvm::final< T >::enableMachineScheduler | ( | ) | const [inline, override] |

Enable the MachineScheduler pass for all X86 subtargets.

Definition at line 477 of file X86Subtarget.h.

| bool llvm::final< T >::ExpandInlineAsm | ( | CallInst * | ) | const [override, virtual] |

This hook allows the target to expand an inline asm call to be explicit llvm code if it wants to. This is useful for turning simple inline asms into LLVM intrinsics, which gives the compiler more information about the behavior of the code.

Reimplemented from llvm::TargetLowering.

| bool llvm::final< T >::expandPostRAPseudo | ( | MachineBasicBlock::iterator | MI | ) | const [override] |

| bool llvm::final< T >::findCommutedOpIndices | ( | MachineInstr * | MI, |

| unsigned & | SrcOpIdx1, | ||

| unsigned & | SrcOpIdx2 | ||

| ) | const [override] |

| std::pair<const TargetRegisterClass*, uint8_t> llvm::final< T >::findRepresentativeClass | ( | MVT | VT | ) | const [override, protected, virtual] |

Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

findRepresentativeClass - Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

Reimplemented from llvm::TargetLoweringBase.

| MachineInstr* llvm::final< T >::foldMemoryOperandImpl | ( | MachineFunction & | MF, |

| MachineInstr * | MI, | ||

| const SmallVectorImpl< unsigned > & | Ops, | ||

| int | FrameIndex | ||

| ) | const [override] |

foldMemoryOperand - If this target supports it, fold a load or store of the specified stack slot into the specified machine instruction for the specified operand(s). If this is possible, the target should perform the folding and return true, otherwise it should return false. If it folds the instruction, it is likely that the MachineInstruction the iterator references has been changed.

| MachineInstr* llvm::final< T >::foldMemoryOperandImpl | ( | MachineFunction & | MF, |

| MachineInstr * | MI, | ||

| const SmallVectorImpl< unsigned > & | Ops, | ||

| MachineInstr * | LoadMI | ||

| ) | const [override] |

foldMemoryOperand - Same as the previous version except it allows folding of any load and store from / to any address, not just from a specific stack slot.

| MachineInstr* llvm::final< T >::foldMemoryOperandImpl | ( | MachineFunction & | MF, |

| MachineInstr * | MI, | ||

| unsigned | OpNum, | ||

| const SmallVectorImpl< MachineOperand > & | MOs, | ||

| unsigned | Size, | ||

| unsigned | Alignment | ||

| ) | const |

| llvm::final< T >::format_object1 | ( | const char * | fmt, |

| const T & | val | ||

| ) | [inline] |

| llvm::final< T >::format_object2 | ( | const char * | fmt, |

| const T1 & | val1, | ||

| const T2 & | val2 | ||

| ) | [inline] |

| llvm::final< T >::format_object3 | ( | const char * | fmt, |

| const T1 & | val1, | ||

| const T2 & | val2, | ||

| const T3 & | val3 | ||

| ) | [inline] |

| llvm::final< T >::format_object4 | ( | const char * | fmt, |

| const T1 & | val1, | ||

| const T2 & | val2, | ||

| const T3 & | val3, | ||

| const T4 & | val4 | ||

| ) | [inline] |

| llvm::final< T >::format_object5 | ( | const char * | fmt, |

| const T1 & | val1, | ||

| const T2 & | val2, | ||

| const T3 & | val3, | ||

| const T4 & | val4, | ||

| const T5 & | val5 | ||

| ) | [inline] |

| llvm::final< T >::FunctionTargetTransformInfo | ( | ) |

| void llvm::final< T >::getAnalysisUsage | ( | AnalysisUsage & | ) | const [override, virtual] |

getAnalysisUsage - This function should be overriden by passes that need analysis information to do their job. If a pass specifies that it uses a particular analysis result to this function, it can then use the getAnalysis<AnalysisType>() function, below.

Reimplemented from llvm::Pass.

| AntiDepBreakMode llvm::final< T >::getAntiDepBreakMode | ( | ) | const [inline, override] |

Definition at line 487 of file X86Subtarget.h.

References llvm::TargetSubtargetInfo::ANTIDEP_CRITICAL.

| unsigned llvm::final< T >::getBaseRegister | ( | ) | const [inline] |

Definition at line 126 of file X86RegisterInfo.h.

| unsigned llvm::final< T >::getByValTypeAlignment | ( | Type * | Ty | ) | const [override, virtual] |

getByValTypeAlignment - Return the desired alignment for ByVal aggregate function arguments in the caller parameter area. For X86, aggregates that contains are placed at 16-byte boundaries while the rest are at 4-byte boundaries.

Reimplemented from llvm::TargetLoweringBase.

| const char* llvm::final< T >::getBZeroEntry | ( | ) | const |

This function returns the name of a function which has an interface like the non-standard bzero function, if such a function exists on the current subtarget and it is considered prefereable over memset with zero passed as the second argument. Otherwise it returns null.

| const MCPhysReg* llvm::final< T >::getCalleeSavedRegs | ( | const MachineFunction * | MF | ) | const [override] |

getCalleeSavedRegs - Return a null-terminated list of all of the callee-save registers on this target.

| const uint32_t* llvm::final< T >::getCallPreservedMask | ( | CallingConv::ID | ) | const [override] |

| const char* llvm::final< T >::getClearCacheBuiltinName | ( | ) | const [inline, override, virtual] |

Intel processors have a unified instruction and data cache.

Reimplemented from llvm::TargetLowering.

Definition at line 789 of file X86ISelLowering.h.

| ConstraintType llvm::final< T >::getConstraintType | ( | const std::string & | Constraint | ) | const [override, virtual] |

Given a constraint, return the type of constraint it is for this target.

Reimplemented from llvm::TargetLowering.

| const TargetRegisterClass* llvm::final< T >::getCrossCopyRegClass | ( | const TargetRegisterClass * | RC | ) | const [override] |

getCrossCopyRegClass - Returns a legal register class to copy a register in the specified class to or from. Returns NULL if it is possible to copy between a two registers of the specified class.

| const DataLayout* llvm::final< T >::getDataLayout | ( | ) | const [inline, override] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 262 of file X86Subtarget.h.

| std::pair<uint16_t, uint16_t> llvm::final< T >::getExecutionDomain | ( | const MachineInstr * | MI | ) | const [override] |

| const X86FrameLowering* llvm::final< T >::getFrameLowering | ( | ) | const [inline, override] |

Definition at line 263 of file X86Subtarget.h.

| unsigned llvm::final< T >::getFrameRegister | ( | const MachineFunction & | MF | ) | const [override] |

| unsigned llvm::final< T >::getGlobalBaseReg | ( | MachineFunction * | MF | ) | const |

getGlobalBaseReg - Return a virtual register initialized with the the global base register value. Output instructions required to initialize the register in the function entry block, if necessary.

| const X86InstrInfo* llvm::final< T >::getInstrInfo | ( | ) | const [inline, override] |

Definition at line 261 of file X86Subtarget.h.

| const InstrItineraryData* llvm::final< T >::getInstrItineraryData | ( | ) | const [inline, override] |

getInstrItins = Return the instruction itineraries based on the subtarget selection.

Definition at line 483 of file X86Subtarget.h.

| unsigned llvm::final< T >::getJumpTableEncoding | ( | ) | const [override, virtual] |

Return the entry encoding for a jump table in the current function. The returned value is a member of the MachineJumpTableInfo::JTEntryKind enum.

getJumpTableEncoding - Return the entry encoding for a jump table in the current function. The returned value is a member of the MachineJumpTableInfo::JTEntryKind enum.

Reimplemented from llvm::TargetLowering.

| const TargetRegisterClass* llvm::final< T >::getLargestLegalSuperClass | ( | const TargetRegisterClass * | RC | ) | const [override] |

| const TargetRegisterClass* llvm::final< T >::getMatchingSuperRegClass | ( | const TargetRegisterClass * | A, |

| const TargetRegisterClass * | B, | ||

| unsigned | Idx | ||

| ) | const [override] |

getMatchingSuperRegClass - Return a subclass of the specified register class A so that each register in it has a sub-register of the specified sub-register index which is in the specified register class B.

| unsigned llvm::final< T >::getMaxInlineSizeThreshold | ( | ) | const [inline] |

getMaxInlineSizeThreshold - Returns the maximum memset / memcpy size that still makes it profitable to inline the call.

Definition at line 280 of file X86Subtarget.h.

| void llvm::final< T >::getNoopForMachoTarget | ( | MCInst & | NopInst | ) | const [override] |

| const uint32_t* llvm::final< T >::getNoPreservedMask | ( | ) | const |

| unsigned llvm::final< T >::getOpcodeAfterMemoryUnfold | ( | unsigned | Opc, |

| bool | UnfoldLoad, | ||

| bool | UnfoldStore, | ||

| unsigned * | LoadRegIndex = nullptr |

||

| ) | const [override] |

getOpcodeAfterMemoryUnfold - Returns the opcode of the would be new instruction after load / store are unfolded from an instruction of the specified opcode. It returns zero if the specified unfolding is not possible. If LoadRegIndex is non-null, it is filled in with the operand index of the operand which will hold the register holding the loaded value.

| EVT llvm::final< T >::getOptimalMemOpType | ( | uint64_t | Size, |

| unsigned | DstAlign, | ||

| unsigned | SrcAlign, | ||

| bool | IsMemset, | ||

| bool | ZeroMemset, | ||

| bool | MemcpyStrSrc, | ||

| MachineFunction & | MF | ||

| ) | const [override, virtual] |

getOptimalMemOpType - Returns the target specific optimal type for load and store operations as a result of memset, memcpy, and memmove lowering. If DstAlign is zero that means it's safe to destination alignment can satisfy any constraint. Similarly if SrcAlign is zero it means there isn't a need to check it against alignment requirement, probably because the source does not need to be loaded. If 'IsMemset' is true, that means it's expanding a memset. If 'ZeroMemset' is true, that means it's a memset of zero. 'MemcpyStrSrc' indicates whether the memcpy source is constant so it does not need to be loaded. It returns EVT::Other if the type should be determined using generic target-independent logic.

Reimplemented from llvm::TargetLoweringBase.

| unsigned llvm::final< T >::getPartialRegUpdateClearance | ( | const MachineInstr * | MI, |

| unsigned | OpNum, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

| SDValue llvm::final< T >::getPICJumpTableRelocBase | ( | SDValue | Table, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

getPICJumpTableRelocaBase - Returns relocation base for the given PIC jumptable.

Reimplemented from llvm::TargetLowering.

| const MCExpr* llvm::final< T >::getPICJumpTableRelocBaseExpr | ( | const MachineFunction * | MF, |

| unsigned | JTI, | ||

| MCContext & | Ctx | ||

| ) | const [override, virtual] |

This returns the relocation base for the given PIC jumptable, the same as getPICJumpTableRelocBase, but as an MCExpr.

getPICJumpTableRelocBaseExpr - This returns the relocation base for the given PIC jumptable, the same as getPICJumpTableRelocBase, but as an MCExpr.

Reimplemented from llvm::TargetLowering.

| PICStyles::Style llvm::final< T >::getPICStyle | ( | ) | const [inline] |

Definition at line 318 of file X86Subtarget.h.

| const TargetRegisterClass* llvm::final< T >::getPointerRegClass | ( | const MachineFunction & | MF, |

| unsigned | Kind = 0 |

||

| ) | const [override] |

getPointerRegClass - Returns a TargetRegisterClass used for pointer values.

| LegalizeTypeAction llvm::final< T >::getPreferredVectorAction | ( | EVT | VT | ) | const [override, virtual] |

Customize the preferred legalization strategy for certain types.

Reimplemented from llvm::TargetLoweringBase.

| std::pair<unsigned, const TargetRegisterClass*> llvm::final< T >::getRegForInlineAsmConstraint | ( | const std::string & | Constraint, |

| MVT | VT | ||

| ) | const [override, virtual] |

getRegForInlineAsmConstraint - Given a physical register constraint (e.g. {edx}), return the register number and the register class for the register. This should only be used for C_Register constraints. On error, this returns a register number of 0.

Reimplemented from llvm::TargetLowering.

| unsigned llvm::final< T >::getRegisterByName | ( | const char * | RegName, |

| EVT | VT | ||

| ) | const [override, virtual] |

Return the register ID of the name passed in. Used by named register global variables extension. There is no target-independent behaviour so the default action is to bail.

Reimplemented from llvm::TargetLowering.

| const X86RegisterInfo& llvm::final< T >::getRegisterInfo | ( | ) | const [inline] |

getRegisterInfo - TargetInstrInfo is a superset of MRegister info. As such, whenever a client has an instance of instruction info, it should always be able to get register info as well (through this method).

Definition at line 175 of file X86InstrInfo.h.

| const X86RegisterInfo* llvm::final< T >::getRegisterInfo | ( | ) | const [inline, override] |

Definition at line 269 of file X86Subtarget.h.

| static const char* llvm::final< T >::getRegisterName | ( | unsigned | RegNo | ) | [static] |

| static const char* llvm::final< T >::getRegisterName | ( | unsigned | RegNo | ) | [static] |

| unsigned llvm::final< T >::getRegPressureLimit | ( | const TargetRegisterClass * | RC, |

| MachineFunction & | MF | ||

| ) | const [override] |

| BitVector llvm::final< T >::getReservedRegs | ( | const MachineFunction & | MF | ) | const [override] |

getReservedRegs - Returns a bitset indexed by physical register number indicating if a register is a special register that has particular uses and should be considered unavailable at all times, e.g. SP, RA. This is used by register scavenger to determine what registers are free.

| SDValue llvm::final< T >::getReturnAddressFrameIndex | ( | SelectionDAG & | DAG | ) | const |

| MVT llvm::final< T >::getScalarShiftAmountTy | ( | EVT | LHSTy | ) | const [inline, override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 540 of file X86ISelLowering.h.

References llvm::MVT::i8.

| int llvm::final< T >::getScalingFactorCost | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

Return the cost of the scaling factor used in the addressing mode represented by AM for this target, for a load/store of the specified type. If the AM is supported, the return value must be >= 0. If the AM is not supported, it returns a negative value.

Reimplemented from llvm::TargetLoweringBase.

| int llvm::final< T >::getSEHRegNum | ( | unsigned | i | ) | const |

| const X86SelectionDAGInfo* llvm::final< T >::getSelectionDAGInfo | ( | ) | const [inline, override] |

Definition at line 266 of file X86Subtarget.h.

| EVT llvm::final< T >::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [override, virtual] |

getSetCCResultType - Return the value type to use for ISD::SETCC.

Reimplemented from llvm::TargetLoweringBase.

| ConstraintWeight llvm::final< T >::getSingleConstraintMatchWeight | ( | AsmOperandInfo & | info, |

| const char * | constraint | ||

| ) | const [override, virtual] |

Examine constraint string and operand type and determine a weight value. The operand object must already have been set up with the operand type.

Reimplemented from llvm::TargetLowering.

| unsigned llvm::final< T >::getSlotSize | ( | ) | const [inline] |

Definition at line 128 of file X86RegisterInfo.h.

| unsigned llvm::final< T >::getStackAlignment | ( | ) | const [inline] |

getStackAlignment - Returns the minimum alignment known to hold of the stack frame on entry to the function and which must be maintained by every function for this subtarget.

Definition at line 276 of file X86Subtarget.h.

| bool llvm::final< T >::getStackCookieLocation | ( | unsigned & | AddressSpace, |

| unsigned & | Offset | ||

| ) | const [override, virtual] |

getStackCookieLocation - Return true if the target stores stack protector cookies at a fixed offset in some non-standard address space, and populates the address space and offset as appropriate.

Reimplemented from llvm::TargetLoweringBase.

| unsigned llvm::final< T >::getStackRegister | ( | ) | const [inline] |

Definition at line 125 of file X86RegisterInfo.h.

| const TargetRegisterClass* llvm::final< T >::getSubClassWithSubReg | ( | const TargetRegisterClass * | RC, |

| unsigned | Idx | ||

| ) | const [override] |

| const X86Subtarget* llvm::final< T >::getSubtarget | ( | ) | const [inline] |

getSubtarget - This method returns a pointer to the specified type of TargetSubtargetInfo. In debug builds, it verifies that the object being returned is of the correct type.

Reimplemented from llvm::TargetMachine.

Definition at line 762 of file X86ISelLowering.h.

| const X86Subtarget* llvm::final< T >::getSubtargetImpl | ( | ) | const [inline, override, virtual] |

getSubtargetImpl - virtual method implemented by subclasses that returns a reference to that target's TargetSubtargetInfo-derived member variable.

Reimplemented from llvm::TargetMachine.

Definition at line 34 of file X86TargetMachine.h.

| const X86TargetLowering* llvm::final< T >::getTargetLowering | ( | ) | const [inline, override] |

Definition at line 258 of file X86Subtarget.h.

| const char* llvm::final< T >::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

getTargetNodeName - This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

| const Triple& llvm::final< T >::getTargetTriple | ( | ) | const [inline] |

Reimplemented from llvm::TargetMachine.

Definition at line 382 of file X86Subtarget.h.

| void llvm::final< T >::getTrap | ( | MCInst & | MI | ) | const [override] |

| void llvm::final< T >::getUnconditionalBranch | ( | MCInst & | Branch, |

| const MCSymbolRefExpr * | BranchTarget | ||

| ) | const [override] |

| unsigned llvm::final< T >::getUndefRegClearance | ( | const MachineInstr * | MI, |

| unsigned & | OpNum, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

| UnitType* llvm::final< T >::getUnitForOffset | ( | uint32_t | Offset | ) | const [inline, virtual] |

Returns the Unit that contains the given section offset in the same section this Unit originated from.

Implements llvm::DWARFUnitSectionBase.

Definition at line 68 of file DWARFUnit.h.

References llvm::sys::path::begin(), and llvm::sys::path::end().

| void llvm::final< T >::getUnrollingPreferences | ( | Loop * | L, |

| TargetTransformInfo::UnrollingPreferences & | UP | ||

| ) | const [inline] |

Definition at line 43 of file FunctionTargetTransformInfo.h.

| bool llvm::final< T >::has3DNow | ( | ) | const [inline] |

Definition at line 335 of file X86Subtarget.h.

| bool llvm::final< T >::has3DNowA | ( | ) | const [inline] |

Definition at line 336 of file X86Subtarget.h.

| bool llvm::final< T >::hasADX | ( | ) | const [inline] |

Definition at line 354 of file X86Subtarget.h.

| bool llvm::final< T >::hasAES | ( | ) | const [inline] |

Definition at line 338 of file X86Subtarget.h.

| bool llvm::final< T >::hasAVX | ( | ) | const [inline] |

Definition at line 329 of file X86Subtarget.h.

| bool llvm::final< T >::hasAVX2 | ( | ) | const [inline] |

Definition at line 330 of file X86Subtarget.h.

| bool llvm::final< T >::hasAVX512 | ( | ) | const [inline] |

Definition at line 331 of file X86Subtarget.h.

| bool llvm::final< T >::hasBasePointer | ( | const MachineFunction & | MF | ) | const |

| bool llvm::final< T >::hasBMI | ( | ) | const [inline] |

Definition at line 350 of file X86Subtarget.h.

| bool llvm::final< T >::hasBMI2 | ( | ) | const [inline] |

Definition at line 351 of file X86Subtarget.h.

| bool llvm::final< T >::hasBWI | ( | ) | const [inline] |

Definition at line 376 of file X86Subtarget.h.

| bool llvm::final< T >::hasCDI | ( | ) | const [inline] |

Definition at line 372 of file X86Subtarget.h.

| bool llvm::final< T >::hasCMov | ( | ) | const [inline] |

Definition at line 321 of file X86Subtarget.h.

| bool llvm::final< T >::hasCmpxchg16b | ( | ) | const [inline] |

Definition at line 364 of file X86Subtarget.h.

| bool llvm::final< T >::hasDQI | ( | ) | const [inline] |

Definition at line 375 of file X86Subtarget.h.

| bool llvm::final< T >::hasERI | ( | ) | const [inline] |

Definition at line 374 of file X86Subtarget.h.

| bool llvm::final< T >::hasF16C | ( | ) | const [inline] |

Definition at line 347 of file X86Subtarget.h.

| bool llvm::final< T >::hasFMA | ( | ) | const [inline] |

Definition at line 340 of file X86Subtarget.h.

| bool llvm::final< T >::hasFMA4 | ( | ) | const [inline] |

Definition at line 342 of file X86Subtarget.h.

| bool llvm::final< T >::hasFp256 | ( | ) | const [inline] |

Definition at line 332 of file X86Subtarget.h.

| bool llvm::final< T >::hasFSGSBase | ( | ) | const [inline] |

Definition at line 348 of file X86Subtarget.h.

| bool llvm::final< T >::hasHighOperandLatency | ( | const InstrItineraryData * | ItinData, |

| const MachineRegisterInfo * | MRI, | ||

| const MachineInstr * | DefMI, | ||

| unsigned | DefIdx, | ||

| const MachineInstr * | UseMI, | ||

| unsigned | UseIdx | ||

| ) | const [override] |

| bool llvm::final< T >::hasHLE | ( | ) | const [inline] |

Definition at line 353 of file X86Subtarget.h.

| bool llvm::final< T >::hasInt256 | ( | ) | const [inline] |

Definition at line 333 of file X86Subtarget.h.

| bool llvm::final< T >::hasLZCNT | ( | ) | const [inline] |

Definition at line 349 of file X86Subtarget.h.

| bool llvm::final< T >::hasMMX | ( | ) | const [inline] |

Definition at line 322 of file X86Subtarget.h.

| bool llvm::final< T >::hasMOVBE | ( | ) | const [inline] |

Definition at line 345 of file X86Subtarget.h.

| bool llvm::final< T >::hasPCLMUL | ( | ) | const [inline] |

Definition at line 339 of file X86Subtarget.h.

| bool llvm::final< T >::hasPFI | ( | ) | const [inline] |

Definition at line 373 of file X86Subtarget.h.

| bool llvm::final< T >::hasPOPCNT | ( | ) | const [inline] |

Definition at line 337 of file X86Subtarget.h.

| bool llvm::final< T >::hasPRFCHW | ( | ) | const [inline] |

Definition at line 357 of file X86Subtarget.h.

| bool llvm::final< T >::hasRDRAND | ( | ) | const [inline] |

Definition at line 346 of file X86Subtarget.h.

| bool llvm::final< T >::hasRDSEED | ( | ) | const [inline] |

Definition at line 358 of file X86Subtarget.h.

| bool llvm::final< T >::hasReservedSpillSlot | ( | const MachineFunction & | MF, |

| unsigned | Reg, | ||

| int & | FrameIdx | ||

| ) | const [override] |

| bool llvm::final< T >::hasRTM | ( | ) | const [inline] |

Definition at line 352 of file X86Subtarget.h.

| bool llvm::final< T >::hasSGX | ( | ) | const [inline] |

Definition at line 356 of file X86Subtarget.h.

| bool llvm::final< T >::hasSHA | ( | ) | const [inline] |

Definition at line 355 of file X86Subtarget.h.

| bool llvm::final< T >::hasSinCos | ( | ) | const |

This function returns true if the target has sincos() routine in its compiler runtime or math libraries.

| bool llvm::final< T >::hasSlowDivide | ( | ) | const [inline] |

Definition at line 366 of file X86Subtarget.h.

| bool llvm::final< T >::hasSMAP | ( | ) | const [inline] |

Definition at line 359 of file X86Subtarget.h.

| bool llvm::final< T >::hasSSE1 | ( | ) | const [inline] |

Definition at line 323 of file X86Subtarget.h.

| bool llvm::final< T >::hasSSE2 | ( | ) | const [inline] |

Definition at line 324 of file X86Subtarget.h.

| bool llvm::final< T >::hasSSE3 | ( | ) | const [inline] |

Definition at line 325 of file X86Subtarget.h.

| bool llvm::final< T >::hasSSE41 | ( | ) | const [inline] |

Definition at line 327 of file X86Subtarget.h.

| bool llvm::final< T >::hasSSE42 | ( | ) | const [inline] |

Definition at line 328 of file X86Subtarget.h.

| bool llvm::final< T >::hasSSE4A | ( | ) | const [inline] |

Definition at line 334 of file X86Subtarget.h.

| bool llvm::final< T >::hasSSSE3 | ( | ) | const [inline] |

Definition at line 326 of file X86Subtarget.h.

| bool llvm::final< T >::hasTBM | ( | ) | const [inline] |

Definition at line 344 of file X86Subtarget.h.

| bool llvm::final< T >::hasVectorUAMem | ( | ) | const [inline] |

Definition at line 363 of file X86Subtarget.h.

| bool llvm::final< T >::hasVLX | ( | ) | const [inline] |

Definition at line 377 of file X86Subtarget.h.

| bool llvm::final< T >::hasXOP | ( | ) | const [inline] |

Definition at line 343 of file X86Subtarget.h.

| unsigned llvm::final< T >::InsertBranch | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock * | TBB, | ||

| MachineBasicBlock * | FBB, | ||

| const SmallVectorImpl< MachineOperand > & | Cond, | ||

| DebugLoc | DL | ||

| ) | const [override] |

| void llvm::final< T >::insertSelect | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| DebugLoc | DL, | ||

| unsigned | DstReg, | ||

| const SmallVectorImpl< MachineOperand > & | Cond, | ||

| unsigned | TrueReg, | ||

| unsigned | FalseReg | ||

| ) | const [override] |

| bool llvm::final< T >::is16Bit | ( | ) | const [inline] |

Definition at line 302 of file X86Subtarget.h.

| bool llvm::final< T >::is32Bit | ( | ) | const [inline] |

Definition at line 298 of file X86Subtarget.h.

| bool llvm::final< T >::is64Bit | ( | ) | const [inline] |

Is this x86_64? (disregarding specific ABI / programming model)

Definition at line 294 of file X86Subtarget.h.

| bool llvm::final< T >::isAtom | ( | ) | const [inline] |

Definition at line 379 of file X86Subtarget.h.

| bool llvm::final< T >::isBTMemSlow | ( | ) | const [inline] |

Definition at line 360 of file X86Subtarget.h.

| bool llvm::final< T >::isCallingConvWin64 | ( | CallingConv::ID | CC | ) | const [inline] |

Definition at line 445 of file X86Subtarget.h.

References llvm::CallingConv::X86_64_SysV, and llvm::CallingConv::X86_64_Win64.

| bool llvm::final< T >::isCoalescableExtInstr | ( | const MachineInstr & | MI, |

| unsigned & | SrcReg, | ||

| unsigned & | DstReg, | ||

| unsigned & | SubIdx | ||

| ) | const [override] |

isCoalescableExtInstr - Return true if the instruction is a "coalescable" extension instruction. That is, it's like a copy where it's legal for the source to overlap the destination. e.g. X86::MOVSX64rr32. If this returns true, then it's expected the pre-extension value is available as a subreg of the result register. This also returns the sub-register index in SubIdx.

| bool llvm::final< T >::IsDesirableToPromoteOp | ( | SDValue | Op, |

| EVT & | PVT | ||

| ) | const [override, virtual] |

isTypeDesirable - Return true if the target has native support for the specified value type and it is 'desirable' to use the type. e.g. On x86 i16 is legal, but undesirable since i16 instruction encodings are longer and some i16 instructions are slow.

Reimplemented from llvm::TargetLowering.

| bool llvm::final< T >::isFMAFasterThanFMulAndFAdd | ( | EVT | VT | ) | const [override, virtual] |

isFMAFasterThanFMulAndFAdd - Return true if an FMA operation is faster than a pair of fmul and fadd instructions. fmuladd intrinsics will be expanded to FMAs when this method returns true, otherwise fmuladd is expanded to fmul + fadd.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isFPImmLegal | ( | const APFloat & | Imm, |

| EVT | VT | ||

| ) | const [override, virtual] |

isFPImmLegal - Returns true if the target can instruction select the specified FP immediate natively. If false, the legalizer will materialize the FP immediate as a load from a constant pool.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isGAPlusOffset | ( | SDNode * | N, |

| const GlobalValue *& | GA, | ||

| int64_t & | Offset | ||

| ) | const [override, virtual] |

Returns true (and the GlobalValue and the offset) if the node is a GlobalAddress + offset.

isGAPlusOffset - Returns true (and the GlobalValue and the offset) if the node is a GlobalAddress + offset.

Reimplemented from llvm::TargetLowering.

| bool llvm::final< T >::isHighLatencyDef | ( | int | opc | ) | const [override] |

| bool llvm::final< T >::isIntegerTypeFTOL | ( | EVT | VT | ) | const [inline] |

isIntegerTypeFTOL - Return true if the MSVC _ftol2 routine should be used for fptoui to the given type.

Definition at line 779 of file X86ISelLowering.h.

References llvm::MVT::i64.

| bool llvm::final< T >::isLegalAddImmediate | ( | int64_t | Imm | ) | const [override, virtual] |

isLegalAddImmediate - Return true if the specified immediate is legal add immediate, that is the target has add instructions which can add a register and the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isLegalAddressingMode | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isLegalICmpImmediate | ( | int64_t | Imm | ) | const [override, virtual] |

isLegalICmpImmediate - Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::IsLegalToCallImmediateAddr | ( | const TargetMachine & | TM | ) | const |

IsLegalToCallImmediateAddr - Return true if the subtarget allows calls to immediate address.

| unsigned llvm::final< T >::isLoadFromStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

| unsigned llvm::final< T >::isLoadFromStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

isLoadFromStackSlotPostFE - Check for post-frame ptr elimination stack locations as well. This uses a heuristic so it isn't reliable for correctness.

| bool llvm::final< T >::isNarrowingProfitable | ( | EVT | VT1, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

isNarrowingProfitable - Return true if it's profitable to narrow operations of type VT1 to VT2. e.g. on x86, it's profitable to narrow from i32 to i8 but not from i32 to i16.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isNoopAddrSpaceCast | ( | unsigned | SrcAS, |

| unsigned | DestAS | ||

| ) | const [override, virtual] |

Returns true if a cast between SrcAS and DestAS is a noop.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isOSWindows | ( | ) | const [inline] |

Definition at line 419 of file X86Subtarget.h.

| bool llvm::final< T >::isPICStyleGOT | ( | ) | const [inline] |

Definition at line 430 of file X86Subtarget.h.

References llvm::ARMCP::GOT.

| bool llvm::final< T >::isPICStyleRIPRel | ( | ) | const [inline] |

Definition at line 431 of file X86Subtarget.h.

References llvm::PICStyles::RIPRel.

| bool llvm::final< T >::isPICStyleSet | ( | ) | const [inline] |

Definition at line 429 of file X86Subtarget.h.

References llvm::None.

| bool llvm::final< T >::isPICStyleStubAny | ( | ) | const [inline] |

Definition at line 440 of file X86Subtarget.h.

References llvm::PICStyles::StubDynamicNoPIC, and llvm::PICStyles::StubPIC.

| bool llvm::final< T >::isPICStyleStubNoDynamic | ( | ) | const [inline] |

Definition at line 437 of file X86Subtarget.h.

References llvm::PICStyles::StubDynamicNoPIC.

| bool llvm::final< T >::isPICStyleStubPIC | ( | ) | const [inline] |

Definition at line 433 of file X86Subtarget.h.

References llvm::PICStyles::StubPIC.

| bool llvm::final< T >::isReallyTriviallyReMaterializable | ( | const MachineInstr * | MI, |

| AliasAnalysis * | AA | ||

| ) | const [override] |

| bool llvm::final< T >::isSafeMemOpType | ( | MVT | VT | ) | const [override, virtual] |

isSafeMemOpType - Returns true if it's safe to use load / store of the specified type to expand memcpy / memset inline. This is mostly true for all types except for some special cases. For example, on X86 targets without SSE2 f64 load / store are done with fldl / fstpl which also does type conversion. Note the specified type doesn't have to be legal as the hook is used before type legalization.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isSafeToClobberEFLAGS | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I | ||

| ) | const |

isSafeToClobberEFLAGS - Return true if it's safe insert an instruction tha would clobber the EFLAGS condition register. Note the result may be conservative. If it cannot definitely determine the safety after visiting a few instructions in each direction it assumes it's not safe.

| bool llvm::final< T >::isSafeToMoveRegClassDefs | ( | const TargetRegisterClass * | RC | ) | const [override] |

isSafeToMoveRegClassDefs - Return true if it's safe to move a machine instruction that defines the specified register class.

| bool llvm::final< T >::isScalarFPTypeInSSEReg | ( | EVT | VT | ) | const [inline] |

isScalarFPTypeInSSEReg - Return true if the specified scalar FP type is computed in an SSE register, not on the X87 floating point stack.

Definition at line 768 of file X86ISelLowering.h.

References llvm::MVT::f32, and llvm::MVT::f64.

| bool llvm::final< T >::isSHLDSlow | ( | ) | const [inline] |

Definition at line 361 of file X86Subtarget.h.

| bool llvm::final< T >::isShuffleMaskLegal | ( | const SmallVectorImpl< int > & | Mask, |

| EVT | VT | ||

| ) | const [override, virtual] |

isShuffleMaskLegal - Targets can use this to indicate that they only support *some* VECTOR_SHUFFLE operations, those with specific masks. By default, if a target supports the VECTOR_SHUFFLE node, all mask values are assumed to be legal.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isSLM | ( | ) | const [inline] |

Definition at line 380 of file X86Subtarget.h.

| unsigned llvm::final< T >::isStoreToStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

| unsigned llvm::final< T >::isStoreToStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

isStoreToStackSlotPostFE - Check for post-frame ptr elimination stack locations as well. This uses a heuristic so it isn't reliable for correctness.

| bool llvm::final< T >::isTarget64BitILP32 | ( | ) | const [inline] |

Is this x86_64 with the ILP32 programming model (x32 ABI)?

Definition at line 307 of file X86Subtarget.h.

References llvm::Triple::GNUX32, and llvm::Triple::NaCl.

| bool llvm::final< T >::isTarget64BitLP64 | ( | ) | const [inline] |

Is this x86_64 with the LP64 programming model (standard AMD64, no x32)?

Definition at line 313 of file X86Subtarget.h.

References llvm::Triple::GNUX32, and llvm::Triple::NaCl.

| bool llvm::final< T >::isTargetCOFF | ( | ) | const [inline] |

Definition at line 393 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetCygMing | ( | ) | const [inline] |

Definition at line 417 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetDarwin | ( | ) | const [inline] |

Definition at line 384 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetELF | ( | ) | const [inline] |

Definition at line 392 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetFreeBSD | ( | ) | const [inline] |

Definition at line 385 of file X86Subtarget.h.

References llvm::Triple::FreeBSD.

| bool llvm::final< T >::isTargetFTOL | ( | ) | const |

isTargetFTOL - Return true if the target uses the MSVC _ftol2 routine for fptoui.

| bool llvm::final< T >::isTargetKnownWindowsMSVC | ( | ) | const [inline] |

Definition at line 405 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetLinux | ( | ) | const [inline] |

Definition at line 396 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetMacho | ( | ) | const [inline] |

Definition at line 394 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetNaCl | ( | ) | const [inline] |

Definition at line 397 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetNaCl32 | ( | ) | const [inline] |

Definition at line 398 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetNaCl64 | ( | ) | const [inline] |

Definition at line 399 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetSolaris | ( | ) | const [inline] |

Definition at line 388 of file X86Subtarget.h.

References llvm::Triple::Solaris.

| bool llvm::final< T >::isTargetWin32 | ( | ) | const [inline] |

Definition at line 425 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetWin64 | ( | ) | const [inline] |

Definition at line 421 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetWindowsCygwin | ( | ) | const [inline] |

Definition at line 409 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetWindowsGNU | ( | ) | const [inline] |

Definition at line 413 of file X86Subtarget.h.

| bool llvm::final< T >::isTargetWindowsMSVC | ( | ) | const [inline] |

Definition at line 401 of file X86Subtarget.h.

| bool llvm::final< T >::isTruncateFree | ( | Type * | Ty1, |

| Type * | Ty2 | ||

| ) | const [override, virtual] |

isTruncateFree - Return true if it's free to truncate a value of type Ty1 to type Ty2. e.g. On x86 it's free to truncate a i32 value in register EAX to i16 by referencing its sub-register AX.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isTruncateFree | ( | EVT | VT1, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isTypeDesirableForOp | ( | unsigned | Opc, |

| EVT | VT | ||

| ) | const [override, virtual] |

isTypeDesirableForOp - Return true if the target has native support for the specified value type and it is 'desirable' to use the type for the given node type. e.g. On x86 i16 is legal, but undesirable since i16 instruction encodings are longer and some i16 instructions are slow.

Reimplemented from llvm::TargetLowering.

| bool llvm::final< T >::isUnalignedMemAccessFast | ( | ) | const [inline] |

Definition at line 362 of file X86Subtarget.h.

| bool llvm::final< T >::isUnpredicatedTerminator | ( | const MachineInstr * | MI | ) | const [override] |

| bool llvm::final< T >::isVectorClearMaskLegal | ( | const SmallVectorImpl< int > & | Mask, |

| EVT | VT | ||

| ) | const [override, virtual] |

isVectorClearMaskLegal - Similar to isShuffleMaskLegal. This is used by Targets can use this to indicate if there is a suitable VECTOR_SHUFFLE that can be used to replace a VAND with a constant pool entry.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isVectorShiftByScalarCheap | ( | Type * | Ty | ) | const [override, virtual] |

Return true if it's significantly cheaper to shift a vector by a uniform scalar than by an amount which will vary across each lane. On x86, for example, there is a "psllw" instruction for the former case, but no simple instruction for a general "a << b" operation on vectors.

Reimplemented from llvm::TargetLoweringBase.

| static bool llvm::final< T >::isX86_64ExtendedReg | ( | const MachineOperand & | MO | ) | [inline, static] |

Definition at line 379 of file X86InstrInfo.h.

References llvm::MachineOperand::getReg(), llvm::MachineOperand::isReg(), and llvm::X86II::isX86_64ExtendedReg().

| bool llvm::final< T >::isZExtFree | ( | Type * | Ty1, |

| Type * | Ty2 | ||

| ) | const [override, virtual] |

isZExtFree - Return true if any actual instruction that defines a value of type Ty1 implicit zero-extends the value to Ty2 in the result register. This does not necessarily include registers defined in unknown ways, such as incoming arguments, or copies from unknown virtual registers. Also, if isTruncateFree(Ty2, Ty1) is true, this does not necessarily apply to truncate instructions. e.g. on x86-64, all instructions that define 32-bit values implicit zero-extend the result out to 64 bits.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isZExtFree | ( | EVT | VT1, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::isZExtFree | ( | SDValue | Val, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Return true if zero-extending the specific node Val to type VT2 is free (either because it's implicitly zero-extended such as ARM ldrb / ldrh or because it's folded such as X86 zero-extending loads).

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::LEAusesAG | ( | ) | const [inline] |

Definition at line 369 of file X86Subtarget.h.

| void llvm::final< T >::loadRegFromAddr | ( | MachineFunction & | MF, |

| unsigned | DestReg, | ||

| SmallVectorImpl< MachineOperand > & | Addr, | ||

| const TargetRegisterClass * | RC, | ||

| MachineInstr::mmo_iterator | MMOBegin, | ||

| MachineInstr::mmo_iterator | MMOEnd, | ||

| SmallVectorImpl< MachineInstr * > & | NewMIs | ||

| ) | const |

| void llvm::final< T >::loadRegFromStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | DestReg, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

| void llvm::final< T >::LowerAsmOperandForConstraint | ( | SDValue | Op, |

| std::string & | Constraint, | ||

| std::vector< SDValue > & | Ops, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerAsmOperandForConstraint - Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops. If hasMemory is true it means one of the asm constraint of the inline asm instruction being processed is 'm'.

Reimplemented from llvm::TargetLowering.

| const MCExpr* llvm::final< T >::LowerCustomJumpTableEntry | ( | const MachineJumpTableInfo * | MJTI, |

| const MachineBasicBlock * | MBB, | ||

| unsigned | uid, | ||

| MCContext & | Ctx | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLowering.

| SDValue llvm::final< T >::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerOperation - Provide custom lowering hooks for some operations.

Reimplemented from llvm::TargetLowering.

| const char* llvm::final< T >::LowerXConstraint | ( | EVT | ConstraintVT | ) | const [override, virtual] |

Try to replace an X constraint, which matches anything, with another that has more specific requirements based on the type of the corresponding operand. This returns null if there is no replacement to make.

LowerXConstraint - try to replace an X constraint, which matches anything, with another that has more specific requirements based on the type of the corresponding operand.

Reimplemented from llvm::TargetLowering.

| bool llvm::final< T >::needsStackRealignment | ( | const MachineFunction & | MF | ) | const [override] |

| bool llvm::final< T >::optimizeCompareInstr | ( | MachineInstr * | CmpInstr, |

| unsigned | SrcReg, | ||

| unsigned | SrcReg2, | ||

| int | CmpMask, | ||

| int | CmpValue, | ||

| const MachineRegisterInfo * | MRI | ||

| ) | const [override] |

optimizeCompareInstr - Check if there exists an earlier instruction that operates on the same source operands and sets flags in the same way as Compare; remove Compare if possible.

| MachineInstr* llvm::final< T >::optimizeLoadInstr | ( | MachineInstr * | MI, |

| const MachineRegisterInfo * | MRI, | ||

| unsigned & | FoldAsLoadDefReg, | ||

| MachineInstr *& | DefMI | ||

| ) | const [override] |

optimizeLoadInstr - Try to remove the load by folding it to a register operand at the use. We fold the load instructions if and only if the def and use are in the same BB. We only look at one load and see whether it can be folded into MI. FoldAsLoadDefReg is the virtual register defined by the load we are trying to fold. DefMI returns the machine instruction that defines FoldAsLoadDefReg, and the function returns the machine instruction generated due to folding.

| bool llvm::final< T >::padShortFunctions | ( | ) | const [inline] |

Definition at line 367 of file X86Subtarget.h.

| void llvm::final< T >::ParseSubtargetFeatures | ( | StringRef | CPU, |

| StringRef | FS | ||

| ) |

ParseSubtargetFeatures - Parses features string setting specified subtarget options. Definition of function is auto generated by tblgen.

| SDValue llvm::final< T >::PerformDAGCombine | ( | SDNode * | N, |

| DAGCombinerInfo & | DCI | ||

| ) | const [override, virtual] |

This method will be invoked for all target nodes and for any target-independent nodes that the target has registered with invoke it for.

The semantics are as follows: Return Value: SDValue.Val == 0 - No change was made SDValue.Val == N - N was replaced, is dead, and is already handled. otherwise - N should be replaced by the returned Operand.

In addition, methods provided by DAGCombinerInfo may be used to perform more complex transformations.

Reimplemented from llvm::TargetLowering.

| bool llvm::final< T >::printAliasInstr | ( | const MCInst * | MI, |

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printAVXCC | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printAVXCC | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printCustomAliasOperand | ( | const MCInst * | MI, |

| unsigned | OpIdx, | ||

| unsigned | PrintMethodIdx, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printDstIdx | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printDstIdx | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printDstIdx16 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 115 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printDstIdx16 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 126 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printDstIdx32 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 118 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printDstIdx32 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 130 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printDstIdx64 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 121 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printDstIdx64 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 134 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printDstIdx8 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 112 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printDstIdx8 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 122 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printf128mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 90 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf128mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 92 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf256mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 93 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf256mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 96 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf32mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 80 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf32mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 81 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf512mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 96 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf512mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 100 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf64mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 84 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf64mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 84 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf80mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 87 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printf80mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 88 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi128mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 68 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi128mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 72 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi16mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 56 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi16mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 63 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi256mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 72 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi256mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 75 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi32mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 60 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi32mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 66 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi512mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 76 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi512mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 78 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi64mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 64 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi64mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 69 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi8mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 52 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printi8mem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 60 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printInst | ( | const MCInst * | MI, |

| raw_ostream & | OS, | ||

| StringRef | Annot | ||

| ) | [override, virtual] |

printInst - Print the specified MCInst to the specified raw_ostream.

Implements llvm::MCInstPrinter.

| void llvm::final< T >::printInst | ( | const MCInst * | MI, |

| raw_ostream & | OS, | ||

| StringRef | Annot | ||

| ) | [override, virtual] |

printInst - Print the specified MCInst to the specified raw_ostream.

Implements llvm::MCInstPrinter.

| void llvm::final< T >::printInstruction | ( | const MCInst * | MI, |

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printInstruction | ( | const MCInst * | MI, |

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printMemOffs16 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 127 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printMemOffs16 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 142 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printMemOffs32 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 130 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printMemOffs32 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 146 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printMemOffs64 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 133 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printMemOffs64 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 150 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printMemOffs8 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 124 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printMemOffs8 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 138 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printMemOffset | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printMemOffset | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printMemReference | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printMemReference | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printopaquemem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 47 of file X86IntelInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printopaquemem | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 56 of file X86ATTInstPrinter.h.

References printMemReference().

| void llvm::final< T >::printOperand | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printOperand | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printPCRelImm | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printPCRelImm | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printRegName | ( | raw_ostream & | OS, |

| unsigned | RegNo | ||

| ) | const [override, virtual] |

printRegName - Print the assembler register name.

Reimplemented from llvm::MCInstPrinter.

| void llvm::final< T >::printRegName | ( | raw_ostream & | OS, |

| unsigned | RegNo | ||

| ) | const [override, virtual] |

printRegName - Print the assembler register name.

Reimplemented from llvm::MCInstPrinter.

| void llvm::final< T >::printRoundingControl | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printRoundingControl | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printSrcIdx | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printSrcIdx | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::printSrcIdx16 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 103 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printSrcIdx16 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 110 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printSrcIdx32 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 106 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printSrcIdx32 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 114 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printSrcIdx64 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 109 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printSrcIdx64 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 118 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printSrcIdx8 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 100 of file X86ATTInstPrinter.h.

| void llvm::final< T >::printSrcIdx8 | ( | const MCInst * | MI, |

| unsigned | OpNo, | ||

| raw_ostream & | O | ||

| ) | [inline] |

Definition at line 106 of file X86IntelInstPrinter.h.

| void llvm::final< T >::printSSECC | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | O | ||

| ) |

| void llvm::final< T >::printSSECC | ( | const MCInst * | MI, |

| unsigned | Op, | ||

| raw_ostream & | OS | ||

| ) |

| void llvm::final< T >::releaseMemory | ( | ) | [override, virtual] |

releaseMemory() - This member can be implemented by a pass if it wants to be able to release its memory when it is no longer needed. The default behavior of passes is to hold onto memory for the entire duration of their lifetime (which is the entire compile time). For pipelined passes, this is not a big deal because that memory gets recycled every time the pass is invoked on another program unit. For IP passes, it is more important to free memory when it is unused.

Optionally implement this function to release pass memory when it is no longer used.

Reimplemented from llvm::Pass.

| void llvm::final< T >::reMaterialize | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | DestReg, | ||

| unsigned | SubIdx, | ||

| const MachineInstr * | Orig, | ||

| const TargetRegisterInfo & | TRI | ||

| ) | const [override] |

| unsigned llvm::final< T >::RemoveBranch | ( | MachineBasicBlock & | MBB | ) | const [override] |

| void llvm::final< T >::ReplaceNodeResults | ( | SDNode * | N, |

| SmallVectorImpl< SDValue > & | Results, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

ReplaceNodeResults - Replace the results of node with an illegal result type with new values built out of custom code.

Reimplemented from llvm::TargetLowering.

| void llvm::final< T >::resetOperationActions | ( | ) | [override, virtual] |

Reset the operation actions based on target options.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::ReverseBranchCondition | ( | SmallVectorImpl< MachineOperand > & | Cond | ) | const [override] |

| bool llvm::final< T >::runOnFunction | ( | Function & | F | ) | [override, virtual] |

runOnFunction - Virtual method overriden by subclasses to do the per-function processing of the pass.

Implements llvm::FunctionPass.

| void llvm::final< T >::setExecutionDomain | ( | MachineInstr * | MI, |

| unsigned | Domain | ||

| ) | const [override] |

| void llvm::final< T >::setPICStyle | ( | PICStyles::Style | Style | ) | [inline] |

Definition at line 319 of file X86Subtarget.h.

| bool llvm::final< T >::shouldConvertConstantLoadToIntImm | ( | const APInt & | Imm, |

| Type * | Ty | ||

| ) | const [override, virtual] |

Returns true if it is beneficial to convert a load of a constant to just the constant itself.

Reimplemented from llvm::TargetLoweringBase.

| bool llvm::final< T >::shouldScheduleAdjacent | ( | MachineInstr * | First, |

| MachineInstr * | Second | ||

| ) | const [override] |

| bool llvm::final< T >::shouldScheduleLoadsNear | ( | SDNode * | Load1, |

| SDNode * | Load2, | ||

| int64_t | Offset1, | ||

| int64_t | Offset2, | ||

| unsigned | NumLoads | ||

| ) | const [override] |

shouldScheduleLoadsNear - This is a used by the pre-regalloc scheduler to determine (in conjunction with areLoadsFromSameBasePtr) if two loads should be scheduled togther. On some targets if two loads are loading from addresses in the same cache line, it's better if they are scheduled together. This function takes two integers that represent the load offsets from the common base address. It returns true if it decides it's desirable to schedule the two loads together. "NumLoads" is the number of loads that have already been scheduled after Load1.

| bool llvm::final< T >::ShouldShrinkFPConstant | ( | EVT | VT | ) | const [inline, override, virtual] |

ShouldShrinkFPConstant - If true, then instruction selection should seek to shrink the FP constant of the specified type to a smaller type in order to save space and / or reduce runtime.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 755 of file X86ISelLowering.h.

References llvm::MVT::f80.