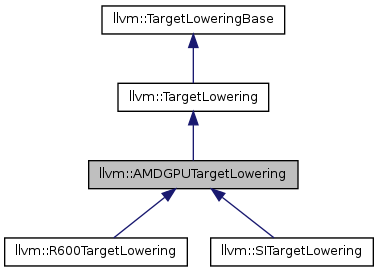

#include <AMDGPUISelLowering.h>

Detailed Description

Definition at line 27 of file AMDGPUISelLowering.h.

Constructor & Destructor Documentation

Definition at line 105 of file AMDGPUISelLowering.cpp.

References llvm::ISD::ADD, llvm::TargetLoweringBase::addBypassSlowDiv(), llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::TargetLoweringBase::AddPromotedToType(), llvm::ISD::AND, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BRIND, llvm::ISD::BSWAP, llvm::ISD::CONCAT_VECTORS, llvm::ISD::Constant, llvm::ISD::ConstantFP, llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::TargetLoweringBase::Custom, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::ISD::EXTRACT_SUBVECTOR, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FCEIL, llvm::ISD::FCOPYSIGN, llvm::ISD::FCOS, llvm::ISD::FDIV, llvm::ISD::FEXP2, llvm::ISD::FFLOOR, llvm::ISD::FLOG2, llvm::ISD::FMA, llvm::ISD::FMUL, llvm::ISD::FNEARBYINT, llvm::ISD::FNEG, llvm::ISD::FP16_TO_FP, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FPOW, llvm::ISD::FREM, llvm::ISD::FRINT, llvm::ISD::FROUND, llvm::ISD::FSIN, llvm::ISD::FSQRT, llvm::ISD::FSUB, llvm::ISD::FTRUNC, llvm::AMDGPUSubtarget::getGeneration(), llvm::TargetMachine::getSubtarget(), llvm::AMDGPUSubtarget::hasBCNT(), llvm::AMDGPUSubtarget::hasBFI(), llvm::AMDGPUSubtarget::hasFFBH(), llvm::AMDGPUSubtarget::hasFFBL(), llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::TargetLoweringBase::Legal, llvm::ISD::LOAD, llvm::TargetLoweringBase::MaxStoresPerMemcpy, llvm::TargetLoweringBase::MaxStoresPerMemmove, llvm::TargetLoweringBase::MaxStoresPerMemset, llvm::ISD::MUL, llvm::ISD::MULHS, llvm::ISD::MULHU, llvm::ISD::OR, llvm::MVT::Other, llvm::TargetLoweringBase::PredictableSelectIsExpensive, llvm::TargetLoweringBase::Promote, llvm::Sched::RegPressure, llvm::ISD::ROTL, llvm::ISD::ROTR, llvm::ISD::SDIV, llvm::ISD::SDIVREM, llvm::AMDGPUSubtarget::SEA_ISLANDS, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::TargetLoweringBase::setHasFloatingPointExceptions(), llvm::TargetLoweringBase::setIntDivIsCheap(), llvm::TargetLoweringBase::setJumpIsExpensive(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setPow2SDivIsCheap(), llvm::TargetLoweringBase::setSchedulingPreference(), llvm::TargetLoweringBase::setSelectIsExpensive(), llvm::TargetLoweringBase::setTargetDAGCombine(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SEXTLOAD, llvm::ISD::SHL, llvm::ISD::SINT_TO_FP, llvm::ISD::SMUL_LOHI, llvm::ISD::SRA, llvm::ISD::SREM, llvm::ISD::SRL, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ISD::SUBC, llvm::ISD::SUBE, Subtarget, llvm::ISD::UDIV, llvm::ISD::UDIVREM, llvm::ISD::UINT_TO_FP, llvm::ISD::UMUL_LOHI, llvm::ISD::UREM, llvm::MVT::v16f32, llvm::MVT::v16i32, llvm::MVT::v2f32, llvm::MVT::v2f64, llvm::MVT::v2i1, llvm::MVT::v2i16, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v2i8, llvm::MVT::v4f32, llvm::MVT::v4i1, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v4i64, llvm::MVT::v4i8, llvm::MVT::v8f32, llvm::MVT::v8i32, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::VSELECT, llvm::ISD::XOR, and llvm::ISD::ZEXTLOAD.

Member Function Documentation

| void AMDGPUTargetLowering::AnalyzeFormalArguments | ( | CCState & | State, |

| const SmallVectorImpl< ISD::InputArg > & | Ins | ||

| ) | const [protected] |

Definition at line 501 of file AMDGPUISelLowering.cpp.

References llvm::CCState::AnalyzeFormalArguments().

Referenced by llvm::R600TargetLowering::LowerFormalArguments(), and llvm::SITargetLowering::LowerFormalArguments().

| SDValue AMDGPUTargetLowering::CombineMinMax | ( | SDNode * | N, |

| SelectionDAG & | DAG | ||

| ) | const |

Generate Min/Max node.

Definition at line 970 of file AMDGPUISelLowering.cpp.

References llvm::MVT::f32, llvm::AMDGPUISD::FMAX, llvm::AMDGPUISD::FMIN, llvm::SelectionDAG::getNode(), llvm::SDNode::getOperand(), llvm::SDNode::getValueType(), llvm_unreachable, llvm::ISD::SETCC_INVALID, llvm::ISD::SETEQ, llvm::ISD::SETFALSE, llvm::ISD::SETFALSE2, llvm::ISD::SETGE, llvm::ISD::SETGT, llvm::ISD::SETLE, llvm::ISD::SETLT, llvm::ISD::SETNE, llvm::ISD::SETO, llvm::ISD::SETOEQ, llvm::ISD::SETOGE, llvm::ISD::SETOGT, llvm::ISD::SETOLE, llvm::ISD::SETOLT, llvm::ISD::SETONE, llvm::ISD::SETTRUE, llvm::ISD::SETTRUE2, llvm::ISD::SETUEQ, llvm::ISD::SETUGE, llvm::ISD::SETUGT, llvm::ISD::SETULE, llvm::ISD::SETULT, llvm::ISD::SETUNE, and llvm::ISD::SETUO.

Referenced by PerformDAGCombine().

| void AMDGPUTargetLowering::computeKnownBitsForTargetNode | ( | const SDValue | Op, |

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [override, virtual] |

Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero and KnownOne bitsets.

Reimplemented from llvm::TargetLowering.

Definition at line 2242 of file AMDGPUISelLowering.cpp.

References llvm::AMDGPUISD::BFE_I32, llvm::AMDGPUISD::BFE_U32, computeKnownBitsForMinMax(), llvm::dyn_cast(), llvm::APInt::getAllOnesValue(), llvm::APInt::getBitWidth(), llvm::APInt::getHighBitsSet(), llvm::APInt::getNullValue(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::ConstantSDNode::getZExtValue(), llvm::ISD::INTRINSIC_WO_CHAIN, llvm::AMDGPUISD::SMAX, llvm::AMDGPUISD::SMIN, llvm::AMDGPUISD::UMAX, and llvm::AMDGPUISD::UMIN.

| unsigned AMDGPUTargetLowering::ComputeNumSignBitsForTargetNode | ( | SDValue | Op, |

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [override, virtual] |

This method can be implemented by targets that want to expose additional information about sign bits to the DAG Combiner.

ComputeNumSignBitsForTargetNode - This method can be implemented by targets that want to expose additional information about sign bits to the DAG Combiner.

Reimplemented from llvm::TargetLowering.

Definition at line 2308 of file AMDGPUISelLowering.cpp.

References llvm::AMDGPUISD::BFE_I32, llvm::AMDGPUISD::BFE_U32, llvm::SelectionDAG::ComputeNumSignBits(), llvm::dyn_cast(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::ConstantSDNode::getZExtValue(), and llvm::ConstantSDNode::isNullValue().

| SDValue AMDGPUTargetLowering::CreateLiveInRegister | ( | SelectionDAG & | DAG, |

| const TargetRegisterClass * | RC, | ||

| unsigned | Reg, | ||

| EVT | VT | ||

| ) | const [virtual] |

Helper function that adds Reg to the LiveIn list of the DAG's MachineFunction.

- Returns:

- a RegisterSDNode representing Reg.

Reimplemented in llvm::SITargetLowering.

Definition at line 2149 of file AMDGPUISelLowering.cpp.

References llvm::MachineRegisterInfo::addLiveIn(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineRegisterInfo::getLiveInVirtReg(), llvm::SelectionDAG::getMachineFunction(), llvm::MachineFunction::getRegInfo(), llvm::SelectionDAG::getRegister(), and llvm::MachineRegisterInfo::isLiveIn().

Referenced by llvm::R600TargetLowering::LowerOperation().

| EVT AMDGPUTargetLowering::getEquivalentLoadRegType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | [static, protected] |

Definition at line 97 of file AMDGPUISelLowering.cpp.

References llvm::EVT::getIntegerVT(), llvm::EVT::getStoreSizeInBits(), llvm::EVT::getVectorVT(), and llvm::MVT::i32.

| EVT AMDGPUTargetLowering::getEquivalentMemType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | [static, protected] |

Definition at line 87 of file AMDGPUISelLowering.cpp.

References llvm::EVT::getIntegerVT(), llvm::EVT::getStoreSizeInBits(), llvm::EVT::getVectorVT(), and llvm::MVT::i32.

| void AMDGPUTargetLowering::getOriginalFunctionArgs | ( | SelectionDAG & | DAG, |

| const Function * | F, | ||

| const SmallVectorImpl< ISD::InputArg > & | Ins, | ||

| SmallVectorImpl< ISD::InputArg > & | OrigIns | ||

| ) | const [protected] |

The SelectionDAGBuilder will automatically promote function arguments with illegal types. However, this does not work for the AMDGPU targets since the function arguments are stored in memory as these illegal types. In order to handle this properly we need to get the origianl types sizes from the LLVM IR Function and fixup the ISD:InputArg values before passing them to AnalyzeFormalArguments()

Definition at line 2097 of file AMDGPUISelLowering.cpp.

References llvm::EVT::isVector(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), and llvm::SmallVectorTemplateCommon< T, typename >::size().

Referenced by llvm::R600TargetLowering::LowerFormalArguments(), and llvm::SITargetLowering::LowerFormalArguments().

| const char * AMDGPUTargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

Definition at line 2166 of file AMDGPUISelLowering.cpp.

References llvm::AMDGPUISD::BFE_I32, llvm::AMDGPUISD::BFE_U32, llvm::ARMISD::BFI, llvm::AMDGPUISD::BFM, llvm::AMDGPUISD::BRANCH_COND, llvm::AMDGPUISD::BREV, llvm::AMDGPUISD::BUILD_VERTICAL_VECTOR, llvm::AArch64ISD::CALL, llvm::AMDGPUISD::CLAMP, llvm::AMDGPUISD::CONST_ADDRESS, llvm::AMDGPUISD::CONST_DATA_PTR, llvm::AMDGPUISD::CVT_F32_UBYTE0, llvm::AMDGPUISD::CVT_F32_UBYTE1, llvm::AMDGPUISD::CVT_F32_UBYTE2, llvm::AMDGPUISD::CVT_F32_UBYTE3, llvm::AMDGPUISD::DIV_FIXUP, llvm::AMDGPUISD::DIV_FMAS, llvm::AMDGPUISD::DIV_SCALE, llvm::AMDGPUISD::DOT4, llvm::AMDGPUISD::DWORDADDR, llvm::AMDGPUISD::EXPORT, llvm::AArch64ISD::FMAX, llvm::AArch64ISD::FMIN, llvm::AMDGPUISD::FRACT, llvm::AMDGPUISD::LDEXP, llvm::AMDGPUISD::LOAD_CONSTANT, llvm::AMDGPUISD::LOAD_INPUT, llvm::AMDGPUISD::MAD, llvm::AMDGPUISD::MAD_I24, llvm::AMDGPUISD::MAD_U24, llvm::AMDGPUISD::MUL_I24, llvm::AMDGPUISD::MUL_U24, NODE_NAME_CASE, llvm::AMDGPUISD::REGISTER_LOAD, llvm::AMDGPUISD::REGISTER_STORE, llvm::AArch64ISD::RET_FLAG, llvm::AMDGPUISD::RSQ, llvm::AMDGPUISD::RSQ_CLAMPED, llvm::AMDGPUISD::RSQ_LEGACY, llvm::AMDGPUISD::SAMPLE, llvm::AMDGPUISD::SAMPLEB, llvm::AMDGPUISD::SAMPLED, llvm::AMDGPUISD::SAMPLEL, llvm::AMDGPUISD::SMAX, llvm::AMDGPUISD::SMIN, llvm::AMDGPUISD::STORE_MSKOR, llvm::AMDGPUISD::TBUFFER_STORE_FORMAT, llvm::AMDGPUISD::TRIG_PREOP, llvm::AMDGPUISD::UMAX, llvm::AMDGPUISD::UMIN, llvm::AMDGPUISD::UMUL, and llvm::AMDGPUISD::URECIP.

| MVT AMDGPUTargetLowering::getVectorIdxTy | ( | ) | const [override, virtual] |

Returns the type to be used for the index operand of: ISD::INSERT_VECTOR_ELT, ISD::EXTRACT_VECTOR_ELT, ISD::INSERT_SUBVECTOR, and ISD::EXTRACT_SUBVECTOR

Reimplemented from llvm::TargetLoweringBase.

Definition at line 408 of file AMDGPUISelLowering.cpp.

References llvm::MVT::i32.

| bool AMDGPUTargetLowering::isFAbsFree | ( | EVT | VT | ) | const [override, virtual] |

Return true if an fabs operation is free to the point where it is never worthwhile to replace it with a bitwise operation.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 446 of file AMDGPUISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, and llvm::EVT::isFloatingPoint().

| bool AMDGPUTargetLowering::isFNegFree | ( | EVT | VT | ) | const [override, virtual] |

Return true if an fneg operation is free to the point where it is never worthwhile to replace it with a bitwise operation.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 451 of file AMDGPUISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, and llvm::EVT::isFloatingPoint().

| bool AMDGPUTargetLowering::isFPImmLegal | ( | const APFloat & | , |

| EVT | |||

| ) | const [override, virtual] |

Returns true if the target can instruction select the specified FP immediate natively. If false, the legalizer will materialize the FP immediate as a load from a constant pool.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 418 of file AMDGPUISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, and llvm::EVT::getScalarType().

| bool AMDGPUTargetLowering::isHWFalseValue | ( | SDValue | Op | ) | const [protected] |

Definition at line 2139 of file AMDGPUISelLowering.cpp.

References llvm::CallingConv::C.

Referenced by llvm::R600TargetLowering::PerformDAGCombine().

| bool AMDGPUTargetLowering::isHWTrueValue | ( | SDValue | Op | ) | const [protected] |

Definition at line 2129 of file AMDGPUISelLowering.cpp.

References llvm::CallingConv::C.

Referenced by llvm::R600TargetLowering::PerformDAGCombine().

| bool AMDGPUTargetLowering::isLoadBitCastBeneficial | ( | EVT | , |

| EVT | |||

| ) | const [override, virtual] |

isLoadBitCastBeneficial() - Return true if the following transform is beneficial. fold (conv (load x)) -> (load (conv*)x) On architectures that don't natively support some vector loads efficiently, casting the load to a smaller vector of larger types and loading is more efficient, however, this can be undone by optimizations in dag combiner.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 429 of file AMDGPUISelLowering.cpp.

References llvm::EVT::getScalarType(), and llvm::EVT::getSizeInBits().

| bool AMDGPUTargetLowering::isNarrowingProfitable | ( | EVT | , |

| EVT | |||

| ) | const [override, virtual] |

Return true if it's profitable to narrow operations of type VT1 to VT2. e.g. on x86, it's profitable to narrow from i32 to i8 but not from i32 to i16.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 487 of file AMDGPUISelLowering.cpp.

References llvm::EVT::getSizeInBits().

| bool AMDGPUTargetLowering::isSelectSupported | ( | SelectSupportKind | SelType | ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 412 of file AMDGPUISelLowering.cpp.

| bool AMDGPUTargetLowering::isTruncateFree | ( | EVT | Src, |

| EVT | Dest | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 456 of file AMDGPUISelLowering.cpp.

References llvm::EVT::bitsLT(), and llvm::EVT::getSizeInBits().

| bool AMDGPUTargetLowering::isTruncateFree | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if it's free to truncate a value of type Ty1 to type Ty2. e.g. On x86 it's free to truncate a i32 value in register EAX to i16 by referencing its sub-register AX.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 461 of file AMDGPUISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits().

| bool AMDGPUTargetLowering::isZExtFree | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if any actual instruction that defines a value of type Ty1 implicitly zero-extends the value to Ty2 in the result register.

This does not necessarily include registers defined in unknown ways, such as incoming arguments, or copies from unknown virtual registers. Also, if isTruncateFree(Ty2, Ty1) is true, this does not necessarily apply to truncate instructions. e.g. on x86-64, all instructions that define 32-bit values implicit zero-extend the result out to 64 bits.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 467 of file AMDGPUISelLowering.cpp.

References llvm::TargetLoweringBase::getDataLayout(), llvm::Type::getScalarType(), and llvm::DataLayout::getTypeSizeInBits().

Referenced by isZExtFree().

| bool AMDGPUTargetLowering::isZExtFree | ( | EVT | Src, |

| EVT | Dest | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 475 of file AMDGPUISelLowering.cpp.

References llvm::MVT::i32, and llvm::MVT::i64.

| bool AMDGPUTargetLowering::isZExtFree | ( | SDValue | Val, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Return true if zero-extending the specific node Val to type VT2 is free (either because it's implicitly zero-extended such as ARM ldrb / ldrh or because it's folded such as X86 zero-extending loads).

Reimplemented from llvm::TargetLoweringBase.

Definition at line 483 of file AMDGPUISelLowering.cpp.

References llvm::SDValue::getValueType(), and isZExtFree().

| SDValue AMDGPUTargetLowering::LowerCall | ( | CallLoweringInfo & | , |

| SmallVectorImpl< SDValue > & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower calls into the the specified DAG. The outgoing arguments to the call are described by the Outs array, and the values to be returned by the call are described by the Ins array. The implementation should fill in the InVals array with legal-type return values from the call, and return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 521 of file AMDGPUISelLowering.cpp.

References llvm::TargetLowering::CallLoweringInfo::Callee, llvm::TargetLowering::CallLoweringInfo::DAG, llvm::LLVMContext::diagnose(), FuncName, G, llvm::SelectionDAG::getContext(), llvm::MachineFunction::getFunction(), and llvm::SelectionDAG::getMachineFunction().

| SDValue AMDGPUTargetLowering::LowerDIVREM24 | ( | SDValue | Op, |

| SelectionDAG & | DAG, | ||

| bool | sign | ||

| ) | const [protected] |

Definition at line 1399 of file AMDGPUISelLowering.cpp.

References llvm::ISD::ADD, llvm::MVT::f32, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FMUL, llvm::ISD::FNEG, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FTRUNC, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getMergeValues(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::EVT::getScalarType(), llvm::SelectionDAG::getSetCC(), llvm::TargetLoweringBase::getSetCCResultType(), llvm::SelectionDAG::getSExtOrTrunc(), llvm::EVT::getSizeInBits(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::MVT::getVectorVT(), llvm::SelectionDAG::getZExtOrTrunc(), llvm::MVT::i32, llvm::ARM_AM::ia, llvm::ARM_AM::ib, llvm::EVT::isVector(), llvm::ISD::MUL, llvm::ISD::OR, llvm::AMDGPUISD::RCP, llvm::ISD::SELECT, llvm::ISD::SETOGE, llvm::ISD::SINT_TO_FP, llvm::ISD::SRA, llvm::ISD::SUB, llvm::ISD::UINT_TO_FP, and llvm::ISD::XOR.

Referenced by LowerSDIVREM().

| SDValue AMDGPUTargetLowering::LowerGlobalAddress | ( | AMDGPUMachineFunction * | MFI, |

| SDValue | Op, | ||

| SelectionDAG & | DAG | ||

| ) | const [protected, virtual] |

Definition at line 689 of file AMDGPUISelLowering.cpp.

References llvm::SmallVectorTemplateCommon< T >::begin(), AMDGPUAS::CONSTANT_ADDRESS, llvm::MachineFrameInfo::CreateStackObject(), llvm::SmallVectorTemplateCommon< T >::end(), G, llvm::GlobalAddressSDNode::getAddressSpace(), llvm::SelectionDAG::getConstant(), llvm::TargetSubtargetInfo::getDataLayout(), llvm::SelectionDAG::getEntryNode(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::GlobalAddressSDNode::getGlobal(), llvm::GlobalVariable::getInitializer(), llvm::SelectionDAG::getMachineFunction(), llvm::GlobalAddressSDNode::getOffset(), llvm::TargetLoweringBase::getPointerTy(), llvm::DataLayout::getPrefTypeAlignment(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::DataLayout::getTypeAllocSize(), llvm::SelectionDAG::getZExtOrTrunc(), llvm::GlobalVariable::hasInitializer(), I, llvm::AMDGPUMachineFunction::LDSSize, llvm_unreachable, llvm::ISD::LOAD, AMDGPUAS::LOCAL_ADDRESS, llvm::AMDGPUMachineFunction::LocalMemoryObjects, AMDGPUAS::PRIVATE_ADDRESS, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::AMDGPUISD::REGISTER_LOAD, llvm::SelectionDAG::UpdateNodeOperands(), llvm::SDNode::use_begin(), and llvm::SDNode::use_end().

Referenced by llvm::R600TargetLowering::LowerOperation().

| SDValue AMDGPUTargetLowering::LowerIntrinsicIABS | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

IABS(a) = SMAX(sub(0, a), a)

Definition at line 943 of file AMDGPUISelLowering.cpp.

References llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SDValue::getValueType(), llvm::AMDGPUISD::SMAX, and llvm::ISD::SUB.

| SDValue AMDGPUTargetLowering::LowerIntrinsicLRP | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Linear Interpolation LRP(a, b, c) = muladd(a, b, (1 - a) * c)

Definition at line 955 of file AMDGPUISelLowering.cpp.

References llvm::MVT::f32, llvm::ISD::FADD, llvm::ISD::FMUL, llvm::ISD::FSUB, llvm::SelectionDAG::getConstantFP(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), and llvm::SDValue::getValueType().

| SDValue AMDGPUTargetLowering::LowerLOAD | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [protected] |

Definition at line 1254 of file AMDGPUISelLowering.cpp.

References llvm::ISD::AND, llvm::EVT::bitsGE(), llvm::ISD::EXTLOAD, llvm::MemSDNode::getAddressSpace(), llvm::LoadSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::LoadSDNode::getExtensionType(), llvm::ISD::getExtForLoadExtType(), llvm::SelectionDAG::getExtLoad(), llvm::AMDGPUSubtarget::getGeneration(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SelectionDAG::getMergeValues(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::EVT::getScalarType(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getValueType(), llvm::SelectionDAG::getZeroExtendInReg(), llvm::MVT::i1, llvm::MVT::i32, llvm::MVT::i8, llvm::EVT::isVector(), llvm::ISD::NON_EXTLOAD, AMDGPUAS::PRIVATE_ADDRESS, llvm::AMDGPUISD::REGISTER_LOAD, llvm::MipsISD::Ret, llvm::ISD::SEXTLOAD, llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND_INREG, llvm::AMDGPUSubtarget::SOUTHERN_ISLANDS, llvm::ISD::SRL, Subtarget, and llvm::ISD::TRUNCATE.

Referenced by ReplaceNodeResults().

| SDValue AMDGPUTargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

This callback is invoked for operations that are unsupported by the target, which are registered to use 'custom' lowering, and whose defined values are all legal. If the target has no operations that require custom lowering, it need not implement this. The default implementation of this aborts.

Reimplemented from llvm::TargetLowering.

Reimplemented in llvm::SITargetLowering, and llvm::R600TargetLowering.

Definition at line 540 of file AMDGPUISelLowering.cpp.

References llvm::ISD::CONCAT_VECTORS, llvm::SDNode::dump(), llvm::ISD::EXTRACT_SUBVECTOR, llvm::ISD::FCEIL, llvm::ISD::FFLOOR, llvm::ISD::FNEARBYINT, llvm::ISD::FrameIndex, llvm::ISD::FREM, llvm::ISD::FRINT, llvm::ISD::FTRUNC, llvm::SDValue::getNode(), llvm::SDValue::getOpcode(), llvm::ISD::INTRINSIC_WO_CHAIN, llvm_unreachable, LowerSDIVREM(), llvm::ISD::SDIVREM, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::UDIVREM, and llvm::ISD::UINT_TO_FP.

| SDValue AMDGPUTargetLowering::LowerReturn | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::OutputArg > & | , | ||

| const SmallVectorImpl< SDValue > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower outgoing return values, described by the Outs array, into the specified DAG. The implementation should return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 507 of file AMDGPUISelLowering.cpp.

References llvm::SelectionDAG::getNode(), llvm::MVT::Other, and llvm::AMDGPUISD::RET_FLAG.

| SDValue AMDGPUTargetLowering::LowerSDIVREM | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [protected] |

Definition at line 1610 of file AMDGPUISelLowering.cpp.

References llvm::ISD::ADD, llvm::SelectionDAG::ComputeNumSignBits(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getMergeValues(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOperand(), llvm::SelectionDAG::getSelectCC(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::i32, LowerDIVREM24(), llvm::ISD::SETLT, llvm::ISD::SUB, llvm::ISD::UDIVREM, and llvm::ISD::XOR.

Referenced by LowerOperation(), and llvm::R600TargetLowering::ReplaceNodeResults().

| SDValue AMDGPUTargetLowering::LowerSTORE | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [protected] |

Definition at line 1339 of file AMDGPUISelLowering.cpp.

References llvm::ISD::AND, llvm::EVT::bitsLT(), llvm::MemSDNode::getAddressSpace(), llvm::StoreSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::MemSDNode::getMemoryVT(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getTargetConstant(), llvm::StoreSDNode::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getZeroExtendInReg(), llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i8, llvm::EVT::isVector(), AMDGPUAS::LOCAL_ADDRESS, llvm::ISD::OR, llvm::MVT::Other, AMDGPUAS::PRIVATE_ADDRESS, llvm::AMDGPUISD::REGISTER_LOAD, llvm::AMDGPUISD::REGISTER_STORE, ScalarizeVectorStore(), llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND, llvm::ISD::SRL, llvm::SPII::Store, and llvm::ISD::XOR.

Referenced by ReplaceNodeResults().

| SDValue AMDGPUTargetLowering::PerformDAGCombine | ( | SDNode * | N, |

| DAGCombinerInfo & | DCI | ||

| ) | const [override, virtual] |

This method will be invoked for all target nodes and for any target-independent nodes that the target has registered with invoke it for.

The semantics are as follows: Return Value: SDValue.Val == 0 - No change was made SDValue.Val == N - N was replaced, is dead, and is already handled. otherwise - N should be replaced by the returned Operand.

In addition, methods provided by DAGCombinerInfo may be used to perform more complex transformations.

Reimplemented from llvm::TargetLowering.

Reimplemented in llvm::SITargetLowering, and llvm::R600TargetLowering.

Definition at line 1987 of file AMDGPUISelLowering.cpp.

References llvm::AMDGPUISD::BFE_I32, llvm::AMDGPUISD::BFE_U32, CombineMinMax(), llvm::TargetLowering::DAGCombinerInfo::CommitTargetLoweringOpt(), llvm::SelectionDAG::ComputeNumSignBits(), llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::dyn_cast(), llvm::APInt::getBitsSet(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::EVT::getIntegerVT(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::SelectionDAG::getTargetLoweringInfo(), llvm::SelectionDAG::getValueType(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getZeroExtendInReg(), llvm::ConstantSDNode::getZExtValue(), llvm::MVT::i32, llvm::TargetLowering::DAGCombinerInfo::isBeforeLegalize(), llvm::TargetLowering::DAGCombinerInfo::isBeforeLegalizeOps(), llvm::EVT::isVector(), llvm::ISD::MUL, llvm::AMDGPUISD::MUL_I24, llvm::AMDGPUISD::MUL_U24, llvm::ISD::SELECT_CC, llvm::ISD::SIGN_EXTEND_INREG, Signed, simplifyI24(), llvm::ISD::SRA, llvm::ISD::SRL, and llvm::ISD::STORE.

| virtual SDNode* llvm::AMDGPUTargetLowering::PostISelFolding | ( | MachineSDNode * | N, |

| SelectionDAG & | DAG | ||

| ) | const [inline, virtual] |

Reimplemented in llvm::SITargetLowering.

Definition at line 143 of file AMDGPUISelLowering.h.

| void AMDGPUTargetLowering::ReplaceNodeResults | ( | SDNode * | , |

| SmallVectorImpl< SDValue > & | , | ||

| SelectionDAG & | |||

| ) | const [override, virtual] |

This callback is invoked when a node result type is illegal for the target, and the operation was registered to use 'custom' lowering for that result type. The target places new result values for the node in Results (their number and types must exactly match those of the original return values of the node), or leaves Results empty, which indicates that the node is not to be custom lowered after all.

If the target has no operations that require custom lowering, it need not implement this. The default implementation aborts.

Reimplemented from llvm::TargetLowering.

Reimplemented in llvm::R600TargetLowering.

Definition at line 566 of file AMDGPUISelLowering.cpp.

References llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm::ISD::LOAD, LowerLOAD(), LowerSTORE(), Node, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SelectionDAG::ReplaceAllUsesOfValueWith(), llvm::ISD::SIGN_EXTEND_INREG, and llvm::ISD::STORE.

| SDValue AMDGPUTargetLowering::ScalarizeVectorLoad | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [protected] |

Split a vector load into a scalar load of each component.

Definition at line 1025 of file AMDGPUISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::BUILD_VECTOR, llvm::MemSDNode::getAlignment(), llvm::LoadSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::LoadSDNode::getExtensionType(), llvm::SelectionDAG::getExtLoad(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SelectionDAG::getMergeValues(), llvm::SelectionDAG::getNode(), llvm::EVT::getStoreSize(), llvm::MachineMemOperand::getValue(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::MemSDNode::isInvariant(), llvm::MemSDNode::isNonTemporal(), llvm::MemSDNode::isVolatile(), llvm::SPII::Load, llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), and llvm::ISD::TokenFactor.

Referenced by SplitVectorLoad().

| SDValue AMDGPUTargetLowering::ScalarizeVectorStore | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [protected] |

Split a vector store into a scalar store of each component.

Definition at line 1172 of file AMDGPUISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::MemSDNode::getAlignment(), llvm::StoreSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getTruncStore(), llvm::MachineMemOperand::getValue(), llvm::StoreSDNode::getValue(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::MVT::i32, llvm::MemSDNode::isNonTemporal(), llvm::MemSDNode::isVolatile(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SPII::Store, and llvm::ISD::TokenFactor.

Referenced by LowerSTORE(), and SplitVectorStore().

| bool AMDGPUTargetLowering::ShouldShrinkFPConstant | ( | EVT | ) | const [override, virtual] |

If true, then instruction selection should seek to shrink the FP constant of the specified type to a smaller type in order to save space and / or reduce runtime.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 424 of file AMDGPUISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, and llvm::EVT::getScalarType().

| SDValue AMDGPUTargetLowering::SplitVectorLoad | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [protected] |

Split a vector load into 2 loads of half the vector.

Definition at line 1065 of file AMDGPUISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::AND, llvm::ISD::CONCAT_VECTORS, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::MemSDNode::getAlignment(), llvm::LoadSDNode::getBasePtr(), llvm::StoreSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::LoadSDNode::getExtensionType(), llvm::SelectionDAG::getExtLoad(), llvm::EVT::getIntegerVT(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SelectionDAG::getMergeValues(), llvm::SelectionDAG::getNode(), llvm::MachineMemOperand::getPointerInfo(), llvm::EVT::getScalarSizeInBits(), llvm::EVT::getSizeInBits(), llvm::SelectionDAG::GetSplitDestVTs(), llvm::SelectionDAG::getStore(), llvm::SelectionDAG::getTruncStore(), llvm::MachineMemOperand::getValue(), llvm::SDValue::getValue(), llvm::StoreSDNode::getValue(), llvm::SDValue::getValueType(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::SelectionDAG::getZExtOrTrunc(), llvm::HexagonISD::Hi, llvm::MVT::i32, llvm::MemSDNode::isInvariant(), llvm::MemSDNode::isNonTemporal(), llvm::MemSDNode::isVolatile(), llvm::HexagonISD::Lo, llvm::SPII::Load, llvm::ISD::OR, llvm::MVT::Other, ScalarizeVectorLoad(), llvm::ISD::SHL, llvm::SelectionDAG::SplitVector(), llvm::SPII::Store, and llvm::ISD::TokenFactor.

| SDValue AMDGPUTargetLowering::SplitVectorStore | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [protected] |

Split a vector store into 2 stores of half the vector.

Definition at line 1204 of file AMDGPUISelLowering.cpp.

References llvm::ISD::ADD, llvm::MemSDNode::getAlignment(), llvm::StoreSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::GetSplitDestVTs(), llvm::EVT::getStoreSize(), llvm::SelectionDAG::getTruncStore(), llvm::MachineMemOperand::getValue(), llvm::StoreSDNode::getValue(), llvm::SDValue::getValueType(), llvm::EVT::getVectorNumElements(), llvm::HexagonISD::Hi, llvm::MemSDNode::isNonTemporal(), llvm::MemSDNode::isVolatile(), llvm::HexagonISD::Lo, llvm::MVT::Other, ScalarizeVectorStore(), llvm::SelectionDAG::SplitVector(), llvm::SPII::Store, and llvm::ISD::TokenFactor.

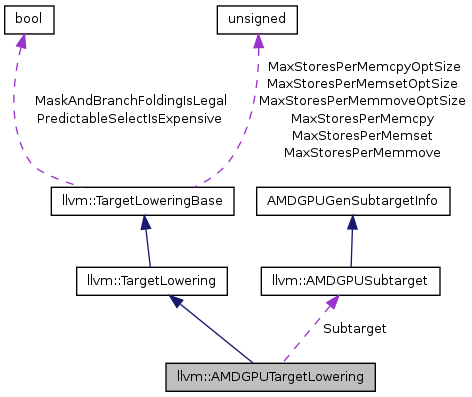

Member Data Documentation

const AMDGPUSubtarget* llvm::AMDGPUTargetLowering::Subtarget [protected] |

Definition at line 29 of file AMDGPUISelLowering.h.

Referenced by AMDGPUTargetLowering(), llvm::SITargetLowering::LowerFormalArguments(), LowerLOAD(), llvm::R600TargetLowering::R600TargetLowering(), llvm::R600TargetLowering::ReplaceNodeResults(), and llvm::SITargetLowering::SITargetLowering().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1