#include <ScheduleDAGInstrs.h>

Public Member Functions | |

| ScheduleDAGInstrs (MachineFunction &mf, const MachineLoopInfo *mli, bool IsPostRAFlag, bool RemoveKillFlags=false, LiveIntervals *LIS=nullptr) | |

| virtual | ~ScheduleDAGInstrs () |

| bool | isPostRA () const |

| LiveIntervals * | getLIS () const |

| Expose LiveIntervals for use in DAG mutators and such. | |

| const TargetSchedModel * | getSchedModel () const |

| Get the machine model for instruction scheduling. | |

| const MCSchedClassDesc * | getSchedClass (SUnit *SU) const |

| Resolve and cache a resolved scheduling class for an SUnit. | |

| MachineBasicBlock::iterator | begin () const |

| begin - Return an iterator to the top of the current scheduling region. | |

| MachineBasicBlock::iterator | end () const |

| end - Return an iterator to the bottom of the current scheduling region. | |

| SUnit * | newSUnit (MachineInstr *MI) |

| newSUnit - Creates a new SUnit and return a ptr to it. | |

| SUnit * | getSUnit (MachineInstr *MI) const |

| getSUnit - Return an existing SUnit for this MI, or NULL. | |

| virtual void | startBlock (MachineBasicBlock *BB) |

| startBlock - Prepare to perform scheduling in the given block. | |

| virtual void | finishBlock () |

| finishBlock - Clean up after scheduling in the given block. | |

| virtual void | enterRegion (MachineBasicBlock *bb, MachineBasicBlock::iterator begin, MachineBasicBlock::iterator end, unsigned regioninstrs) |

| Initialize the scheduler state for the next scheduling region. | |

| virtual void | exitRegion () |

| Notify that the scheduler has finished scheduling the current region. | |

| void | buildSchedGraph (AliasAnalysis *AA, RegPressureTracker *RPTracker=nullptr, PressureDiffs *PDiffs=nullptr) |

| void | addSchedBarrierDeps () |

| virtual void | schedule ()=0 |

| virtual void | finalizeSchedule () |

| void | dumpNode (const SUnit *SU) const override |

| std::string | getGraphNodeLabel (const SUnit *SU) const override |

| Return a label for a DAG node that points to an instruction. | |

| std::string | getDAGName () const override |

| Return a label for the region of code covered by the DAG. | |

| void | fixupKills (MachineBasicBlock *MBB) |

| Fix register kill flags that scheduling has made invalid. | |

Protected Types | |

| typedef std::vector< std::pair < MachineInstr *, MachineInstr * > > | DbgValueVector |

Protected Member Functions | |

| void | initSUnits () |

| void | addPhysRegDataDeps (SUnit *SU, unsigned OperIdx) |

| void | addPhysRegDeps (SUnit *SU, unsigned OperIdx) |

| void | addVRegDefDeps (SUnit *SU, unsigned OperIdx) |

| void | addVRegUseDeps (SUnit *SU, unsigned OperIdx) |

| void | startBlockForKills (MachineBasicBlock *BB) |

| PostRA helper for rewriting kill flags. | |

| bool | toggleKillFlag (MachineInstr *MI, MachineOperand &MO) |

| Toggle a register operand kill flag. | |

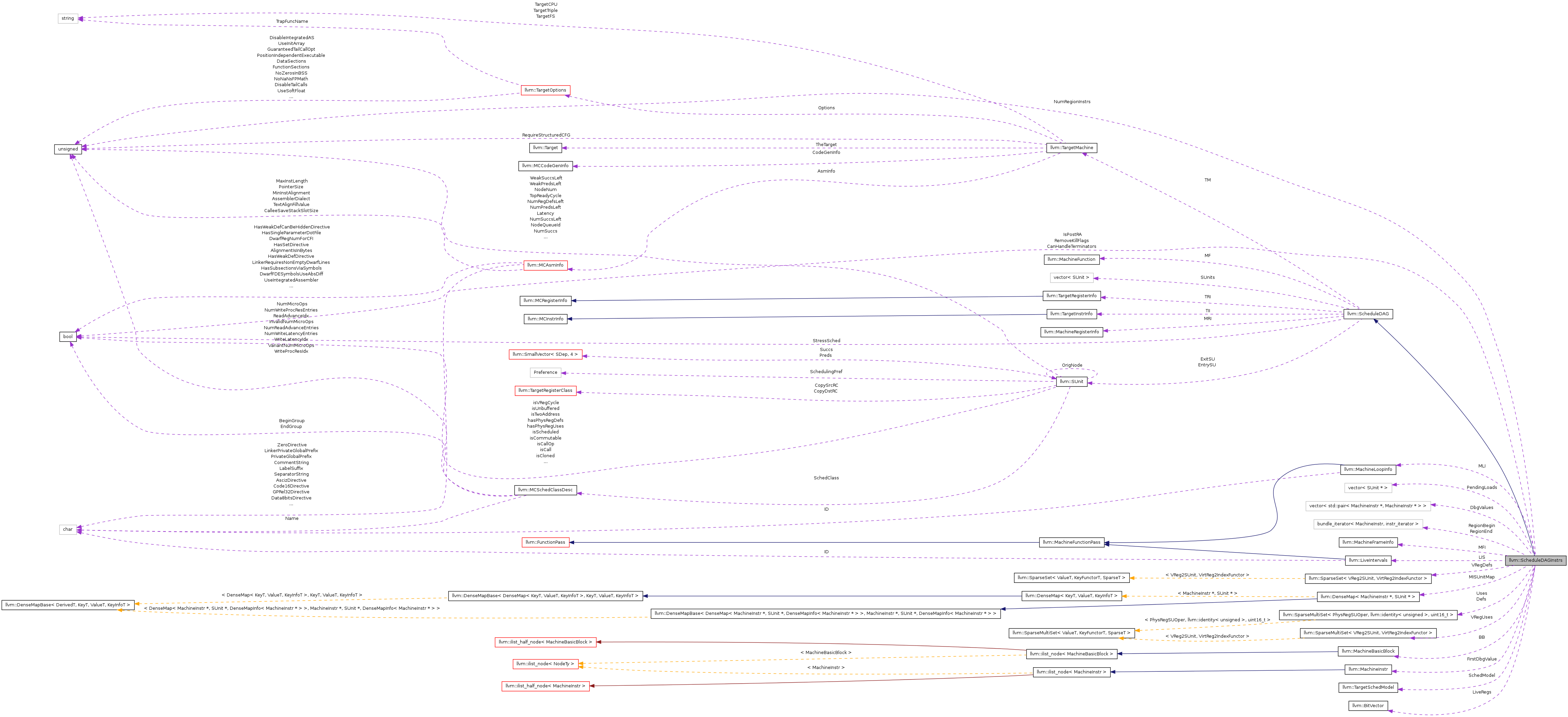

Protected Attributes | |

| const MachineLoopInfo * | MLI |

| const MachineFrameInfo * | MFI |

| LiveIntervals * | LIS |

| Live Intervals provides reaching defs in preRA scheduling. | |

| TargetSchedModel | SchedModel |

| TargetSchedModel provides an interface to the machine model. | |

| bool | IsPostRA |

| isPostRA flag indicates vregs cannot be present. | |

| bool | RemoveKillFlags |

| bool | CanHandleTerminators |

| MachineBasicBlock * | BB |

| The block in which to insert instructions. | |

| MachineBasicBlock::iterator | RegionBegin |

| The beginning of the range to be scheduled. | |

| MachineBasicBlock::iterator | RegionEnd |

| The end of the range to be scheduled. | |

| unsigned | NumRegionInstrs |

| Instructions in this region (distance(RegionBegin, RegionEnd)). | |

| DenseMap< MachineInstr *, SUnit * > | MISUnitMap |

| VReg2UseMap | VRegUses |

| Reg2SUnitsMap | Defs |

| Reg2SUnitsMap | Uses |

| VReg2SUnitMap | VRegDefs |

| Track the last instruction in this region defining each virtual register. | |

| std::vector< SUnit * > | PendingLoads |

| DbgValueVector | DbgValues |

| MachineInstr * | FirstDbgValue |

| BitVector | LiveRegs |

| Set of live physical registers for updating kill flags. | |

Detailed Description

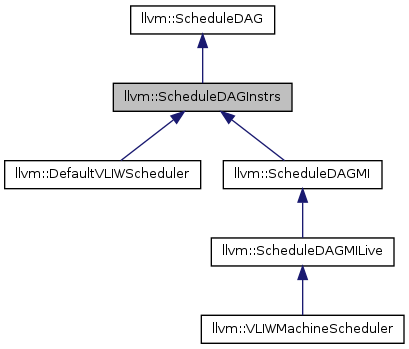

ScheduleDAGInstrs - A ScheduleDAG subclass for scheduling lists of MachineInstrs.

Definition at line 76 of file ScheduleDAGInstrs.h.

Member Typedef Documentation

typedef std::vector<std::pair<MachineInstr *, MachineInstr *> > llvm::ScheduleDAGInstrs::DbgValueVector [protected] |

DbgValues - Remember instruction that precedes DBG_VALUE. These are generated by buildSchedGraph but persist so they can be referenced when emitting the final schedule.

Definition at line 147 of file ScheduleDAGInstrs.h.

Constructor & Destructor Documentation

| ScheduleDAGInstrs::ScheduleDAGInstrs | ( | MachineFunction & | mf, |

| const MachineLoopInfo * | mli, | ||

| bool | IsPostRAFlag, | ||

| bool | RemoveKillFlags = false, |

||

| LiveIntervals * | LIS = nullptr |

||

| ) | [explicit] |

Definition at line 52 of file ScheduleDAGInstrs.cpp.

References DbgValues, llvm::MachineRegisterInfo::getNumVirtRegs(), llvm::MCSubtargetInfo::getSchedModel(), llvm::TargetMachine::getSubtarget(), llvm::TargetSchedModel::init(), IsPostRA, LIS, llvm::ScheduleDAG::MRI, SchedModel, llvm::AArch64DB::ST, llvm::ScheduleDAG::TII, and llvm::ScheduleDAG::TM.

| virtual llvm::ScheduleDAGInstrs::~ScheduleDAGInstrs | ( | ) | [inline, virtual] |

Definition at line 161 of file ScheduleDAGInstrs.h.

Member Function Documentation

| void ScheduleDAGInstrs::addPhysRegDataDeps | ( | SUnit * | SU, |

| unsigned | OperIdx | ||

| ) | [protected] |

MO is an operand of SU's instruction that defines a physical register. Add data dependencies from SU to any uses of the physical register.

Definition at line 251 of file ScheduleDAGInstrs.cpp.

References llvm::SUnit::addPred(), llvm::SDep::Artificial, llvm::TargetSchedModel::computeOperandLatency(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::contains(), llvm::SDep::Data, llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::end(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::find(), llvm::SUnit::getInstr(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::TargetMachine::getSubtarget(), llvm::SUnit::hasPhysRegDefs, I, llvm::MachineOperand::isDef(), llvm::MCRegAliasIterator::isValid(), SchedModel, llvm::SDep::setLatency(), llvm::AArch64DB::ST, llvm::ScheduleDAG::TM, llvm::ScheduleDAG::TRI, and Uses.

Referenced by addPhysRegDeps().

| void ScheduleDAGInstrs::addPhysRegDeps | ( | SUnit * | SU, |

| unsigned | OperIdx | ||

| ) | [protected] |

addPhysRegDeps - Add register dependencies (data, anti, and output) from this SUnit to following instructions in the same scheduling region that depend the physical register referenced at OperIdx.

Definition at line 294 of file ScheduleDAGInstrs.cpp.

References addPhysRegDataDeps(), llvm::SUnit::addPred(), llvm::SDep::Anti, llvm::TargetSchedModel::computeOutputLatency(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::contains(), Defs, llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::end(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::equal_range(), llvm::ScheduleDAG::ExitSU, llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::find(), llvm::SUnit::getInstr(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::SUnit::hasPhysRegUses, I, llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::insert(), llvm::SUnit::isCall, llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isUse(), llvm::MCRegAliasIterator::isValid(), llvm::AArch64CC::MI, llvm::SDep::Output, P, llvm::MachineInstr::registerDefIsDead(), RemoveKillFlags, SchedModel, llvm::MachineOperand::setIsKill(), llvm::SDep::setLatency(), llvm::ScheduleDAG::TRI, and Uses.

Referenced by buildSchedGraph().

addSchedBarrierDeps - Add dependencies from instructions in the current list of instructions being scheduled to scheduling barrier. We want to make sure instructions which define registers that are either used by the terminator or are live-out are properly scheduled. This is especially important when the definition latency of the return value(s) are too high to be hidden by the branch or when the liveout registers used by instructions in the fallthrough block.

addSchedBarrierDeps - Add dependencies from instructions in the current list of instructions being scheduled to scheduling barrier by adding the exit SU to the register defs and use list. This is because we want to make sure instructions which define registers that are either used by the terminator or are live-out are properly scheduled. This is especially important when the definition latency of the return value(s) are too high to be hidden by the branch or when the liveout registers used by instructions in the fallthrough block.

Definition at line 212 of file ScheduleDAGInstrs.cpp.

References addVRegUseDeps(), BB, llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::contains(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::empty(), llvm::MachineBasicBlock::end(), llvm::ScheduleDAG::ExitSU, llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), I, llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::insert(), llvm::MachineInstr::isBarrier(), llvm::MachineInstr::isCall(), llvm::MachineOperand::isDef(), llvm::TargetRegisterInfo::isPhysicalRegister(), IsPostRA, llvm::MachineOperand::isReg(), llvm::MachineOperand::readsReg(), RegionEnd, llvm::SUnit::setInstr(), llvm::MachineBasicBlock::succ_begin(), llvm::MachineBasicBlock::succ_end(), llvm::ScheduleDAG::TRI, and Uses.

Referenced by buildSchedGraph().

| void ScheduleDAGInstrs::addVRegDefDeps | ( | SUnit * | SU, |

| unsigned | OperIdx | ||

| ) | [protected] |

addVRegDefDeps - Add register output and data dependencies from this SUnit to instructions that occur later in the same scheduling region if they read from or write to the virtual register defined at OperIdx.

TODO: Hoist loop induction variable increments. This has to be reevaluated. Generally, IV scheduling should be done before coalescing.

Definition at line 375 of file ScheduleDAGInstrs.cpp.

References llvm::SUnit::addPred(), llvm::TargetSchedModel::computeOutputLatency(), llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::end(), llvm::ScheduleDAG::ExitSU, llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::find(), llvm::SUnit::getInstr(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::hasOneDef(), llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::insert(), llvm::AArch64CC::MI, llvm::ScheduleDAG::MRI, llvm::SDep::Output, SchedModel, llvm::SDep::setLatency(), llvm::VReg2SUnit::SU, and VRegDefs.

Referenced by buildSchedGraph().

| void ScheduleDAGInstrs::addVRegUseDeps | ( | SUnit * | SU, |

| unsigned | OperIdx | ||

| ) | [protected] |

addVRegUseDeps - Add a register data dependency if the instruction that defines the virtual register used at OperIdx is mapped to an SUnit. Add a register antidependency from this SUnit to instructions that occur later in the same scheduling region if they write the virtual register.

TODO: Handle ExitSU "uses" properly.

Definition at line 413 of file ScheduleDAGInstrs.cpp.

References llvm::SUnit::addPred(), llvm::TargetSubtargetInfo::adjustSchedDependency(), llvm::SDep::Anti, llvm::TargetSchedModel::computeOperandLatency(), llvm::SDep::Data, llvm::tgtok::Def, llvm::VNInfo::def, llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::end(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::end(), llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::find(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::find(), llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::SUnit::getInstr(), llvm::LiveIntervals::getInstructionFromIndex(), llvm::LiveIntervals::getInstructionIndex(), llvm::LiveIntervals::getInterval(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::TargetMachine::getSubtarget(), getSUnit(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::insert(), LIS, llvm::AArch64CC::MI, llvm::LiveRange::Query(), SchedModel, llvm::SDep::setLatency(), llvm::AArch64DB::ST, llvm::VReg2SUnit::SU, llvm::ScheduleDAG::TM, llvm::LiveQueryResult::valueIn(), VRegDefs, and VRegUses.

Referenced by addSchedBarrierDeps(), and buildSchedGraph().

| MachineBasicBlock::iterator llvm::ScheduleDAGInstrs::begin | ( | ) | const [inline] |

begin - Return an iterator to the top of the current scheduling region.

Definition at line 179 of file ScheduleDAGInstrs.h.

References RegionBegin.

Referenced by llvm::ScheduleDAGMI::dumpSchedule(), enterRegion(), llvm::ScheduleDAGMI::schedule(), and llvm::ScheduleDAGMILive::schedule().

| void ScheduleDAGInstrs::buildSchedGraph | ( | AliasAnalysis * | AA, |

| RegPressureTracker * | RPTracker = nullptr, |

||

| PressureDiffs * | PDiffs = nullptr |

||

| ) |

buildSchedGraph - Build SUnits from the MachineBasicBlock that we are input.

If RegPressure is non-null, compute register pressure as a side effect. The DAG builder is an efficient place to do it because it already visits operands.

Definition at line 742 of file ScheduleDAGInstrs.cpp.

References addChainDependency(), addPhysRegDeps(), llvm::SUnit::addPred(), addSchedBarrierDeps(), addVRegDefDeps(), addVRegUseDeps(), adjustChainDeps(), llvm::SDep::Artificial, llvm::SDep::Barrier, llvm::MapVector< KeyT, ValueT, MapType, VectorType >::begin(), llvm::SmallVectorTemplateCommon< T, typename >::begin(), CanHandleTerminators, llvm::MapVector< KeyT, ValueT, MapType, VectorType >::clear(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::clear(), llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::clear(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::clear(), llvm::ScheduleDAG::clearDAG(), DbgValues, Defs, llvm::SmallVectorBase::empty(), llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::empty(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::empty(), EnableAASchedMI, llvm::MapVector< KeyT, ValueT, MapType, VectorType >::end(), llvm::SmallVectorTemplateCommon< T, typename >::end(), llvm::ScheduleDAG::ExitSU, llvm::MapVector< KeyT, ValueT, MapType, VectorType >::find(), FirstDbgValue, llvm::MachineInstr::getNumOperands(), llvm::MCRegisterInfo::getNumRegs(), llvm::MachineRegisterInfo::getNumVirtRegs(), llvm::MachineInstr::getOperand(), llvm::RegPressureTracker::getPos(), llvm::MachineOperand::getReg(), llvm::TargetMachine::getSubtarget(), getUnderlyingObjectsForInstr(), I, llvm::ARM_PROC::IE, llvm::PressureDiffs::init(), initSUnits(), llvm::MachineInstr::isDebugValue(), llvm::MachineOperand::isDef(), isGlobalMemoryObject(), llvm::MachineInstr::isInvariantLoad(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MachineInstr::isPosition(), IsPostRA, llvm::MachineOperand::isReg(), llvm::MachineInstr::isTerminator(), llvm::SUnit::Latency, llvm::MachineInstr::mayLoad(), llvm::MachineInstr::mayStore(), MFI, llvm::AArch64CC::MI, MISUnitMap, llvm::ScheduleDAG::MRI, llvm::SUnit::NodeNum, llvm::SUnit::NumSuccs, PendingLoads, llvm::MachineOperand::readsReg(), llvm::RegPressureTracker::recede(), RegionBegin, RegionEnd, llvm::SDep::setLatency(), llvm::SparseSet< ValueT, KeyFunctorT, SparseT >::setUniverse(), llvm::SparseMultiSet< ValueT, KeyFunctorT, SparseT >::setUniverse(), llvm::MapVector< KeyT, ValueT, MapType, VectorType >::size(), llvm::AArch64DB::ST, llvm::ScheduleDAG::SUnits, llvm::ScheduleDAG::TM, llvm::ScheduleDAG::TRI, llvm::TargetSubtargetInfo::useAA(), Uses, VRegDefs, and VRegUses.

Referenced by llvm::ScheduleDAGMILive::buildDAGWithRegPressure(), llvm::DefaultVLIWScheduler::schedule(), and llvm::ScheduleDAGMI::schedule().

| void ScheduleDAGInstrs::dumpNode | ( | const SUnit * | SU | ) | const [override, virtual] |

Implements llvm::ScheduleDAG.

Definition at line 1201 of file ScheduleDAGInstrs.cpp.

References llvm::MachineInstr::dump(), and llvm::SUnit::getInstr().

| MachineBasicBlock::iterator llvm::ScheduleDAGInstrs::end | ( | ) | const [inline] |

end - Return an iterator to the bottom of the current scheduling region.

Definition at line 182 of file ScheduleDAGInstrs.h.

References RegionEnd.

Referenced by llvm::ScheduleDAGMI::dumpSchedule(), and enterRegion().

| void ScheduleDAGInstrs::enterRegion | ( | MachineBasicBlock * | bb, |

| MachineBasicBlock::iterator | begin, | ||

| MachineBasicBlock::iterator | end, | ||

| unsigned | regioninstrs | ||

| ) | [virtual] |

Initialize the scheduler state for the next scheduling region.

Initialize the DAG and common scheduler state for the current scheduling region. This does not actually create the DAG, only clears it. The scheduling driver may call BuildSchedGraph multiple times per scheduling region.

Reimplemented in llvm::ScheduleDAGMILive, and llvm::ScheduleDAGMI.

Definition at line 188 of file ScheduleDAGInstrs.cpp.

References BB, begin(), end(), NumRegionInstrs, RegionBegin, and RegionEnd.

Referenced by llvm::VLIWPacketizerList::PacketizeMIs().

| void ScheduleDAGInstrs::exitRegion | ( | ) | [virtual] |

Notify that the scheduler has finished scheduling the current region.

Close the current scheduling region. Don't clear any state in case the driver wants to refer to the previous scheduling region.

Definition at line 200 of file ScheduleDAGInstrs.cpp.

Referenced by llvm::VLIWPacketizerList::PacketizeMIs().

| virtual void llvm::ScheduleDAGInstrs::finalizeSchedule | ( | ) | [inline, virtual] |

finalizeSchedule - Allow targets to perform final scheduling actions at the level of the whole MachineFunction. By default does nothing.

Definition at line 229 of file ScheduleDAGInstrs.h.

| void ScheduleDAGInstrs::finishBlock | ( | ) | [virtual] |

finishBlock - Clean up after scheduling in the given block.

Definition at line 179 of file ScheduleDAGInstrs.cpp.

References BB.

Referenced by llvm::VLIWPacketizerList::PacketizeMIs().

| void ScheduleDAGInstrs::fixupKills | ( | MachineBasicBlock * | MBB | ) |

Fix register kill flags that scheduling has made invalid.

Definition at line 1113 of file ScheduleDAGInstrs.cpp.

References llvm::MachineBasicBlock::begin(), llvm::BitVector::clearBitsNotInMask(), llvm::dbgs(), DEBUG, llvm::MachineInstr::dump(), llvm::MachineBasicBlock::end(), llvm::MachineBasicBlock::getNumber(), llvm::MachineInstr::getNumOperands(), llvm::MCRegisterInfo::getNumRegs(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getRegMask(), I, llvm::MachineInstr::isDebugValue(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isKill(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), llvm::MachineInstr::isRegTiedToUseOperand(), llvm::MachineRegisterInfo::isReserved(), llvm::MachineOperand::isUndef(), llvm::MachineOperand::isUse(), llvm::MCRegisterInfo::DiffListIterator::isValid(), LiveRegs, llvm::AArch64CC::MI, llvm::ScheduleDAG::MRI, llvm::BitVector::reset(), llvm::BitVector::resize(), llvm::BitVector::set(), llvm::MachineBasicBlock::size(), startBlockForKills(), llvm::BitVector::test(), toggleKillFlag(), and llvm::ScheduleDAG::TRI.

| std::string ScheduleDAGInstrs::getDAGName | ( | ) | const [override, virtual] |

Return a label for the region of code covered by the DAG.

Return the basic block label. It is not necessarilly unique because a block contains multiple scheduling regions. But it is fine for visualization.

Implements llvm::ScheduleDAG.

Definition at line 1221 of file ScheduleDAGInstrs.cpp.

References BB, and llvm::MachineBasicBlock::getFullName().

| std::string ScheduleDAGInstrs::getGraphNodeLabel | ( | const SUnit * | SU | ) | const [override, virtual] |

Return a label for a DAG node that points to an instruction.

Implements llvm::ScheduleDAG.

Definition at line 1207 of file ScheduleDAGInstrs.cpp.

References llvm::ScheduleDAG::EntrySU, llvm::ScheduleDAG::ExitSU, llvm::SUnit::getInstr(), llvm::MachineInstr::print(), llvm::raw_string_ostream::str(), and llvm::ScheduleDAG::TM.

| LiveIntervals* llvm::ScheduleDAGInstrs::getLIS | ( | ) | const [inline] |

Expose LiveIntervals for use in DAG mutators and such.

Definition at line 166 of file ScheduleDAGInstrs.h.

References LIS.

| const MCSchedClassDesc* llvm::ScheduleDAGInstrs::getSchedClass | ( | SUnit * | SU | ) | const [inline] |

Resolve and cache a resolved scheduling class for an SUnit.

Definition at line 172 of file ScheduleDAGInstrs.h.

References llvm::SUnit::getInstr(), llvm::TargetSchedModel::hasInstrSchedModel(), llvm::TargetSchedModel::resolveSchedClass(), llvm::SUnit::SchedClass, and SchedModel.

Referenced by llvm::SchedBoundary::bumpNode(), llvm::SchedBoundary::checkHazard(), llvm::SchedRemainder::init(), llvm::GenericSchedulerBase::SchedCandidate::initResourceDelta(), and initSUnits().

| const TargetSchedModel* llvm::ScheduleDAGInstrs::getSchedModel | ( | ) | const [inline] |

Get the machine model for instruction scheduling.

Definition at line 169 of file ScheduleDAGInstrs.h.

References SchedModel.

Referenced by llvm::ConvergingVLIWScheduler::initialize(), and llvm::PostGenericScheduler::initialize().

| SUnit * llvm::ScheduleDAGInstrs::getSUnit | ( | MachineInstr * | MI | ) | const [inline] |

getSUnit - Return an existing SUnit for this MI, or NULL.

Definition at line 271 of file ScheduleDAGInstrs.h.

References llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::end(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::find(), I, and MISUnitMap.

Referenced by addVRegUseDeps(), llvm::ScheduleDAGMILive::computeCyclicCriticalPath(), and llvm::ScheduleDAGMI::dumpSchedule().

| void ScheduleDAGInstrs::initSUnits | ( | ) | [protected] |

Create an SUnit for each real instruction, numbered in top-down toplological order. The instruction order A < B, implies that no edge exists from B to A.

Map each real instruction to its SUnit.

After initSUnits, the SUnits vector cannot be resized and the scheduler may hang onto SUnit pointers. We may relax this in the future by using SUnit IDs instead of pointers.

MachineScheduler relies on initSUnits numbering the nodes by their order in the original instruction list.

Definition at line 692 of file ScheduleDAGInstrs.cpp.

References llvm::MCProcResourceDesc::BufferSize, llvm::TargetSchedModel::computeInstrLatency(), llvm::SUnit::getInstr(), llvm::TargetSchedModel::getProcResource(), getSchedClass(), llvm::TargetSchedModel::getWriteProcResBegin(), llvm::TargetSchedModel::getWriteProcResEnd(), llvm::TargetSchedModel::hasInstrSchedModel(), llvm::SUnit::hasReservedResource, I, llvm::SUnit::isCall, llvm::MachineInstr::isCall(), llvm::SUnit::isCommutable, llvm::MachineInstr::isCommutable(), llvm::MachineInstr::isDebugValue(), llvm::SUnit::isUnbuffered, llvm::SUnit::Latency, llvm::AArch64CC::MI, MISUnitMap, newSUnit(), NumRegionInstrs, RegionBegin, RegionEnd, llvm::PPCISD::SC, SchedModel, and llvm::ScheduleDAG::SUnits.

Referenced by buildSchedGraph().

| bool llvm::ScheduleDAGInstrs::isPostRA | ( | ) | const [inline] |

Definition at line 163 of file ScheduleDAGInstrs.h.

References IsPostRA.

| SUnit * llvm::ScheduleDAGInstrs::newSUnit | ( | MachineInstr * | MI | ) | [inline] |

newSUnit - Creates a new SUnit and return a ptr to it.

Definition at line 259 of file ScheduleDAGInstrs.h.

References llvm::ScheduleDAG::SUnits.

Referenced by initSUnits().

| virtual void llvm::ScheduleDAGInstrs::schedule | ( | ) | [pure virtual] |

schedule - Order nodes according to selected style, filling in the Sequence member.

Typically, a scheduling algorithm will implement schedule() without overriding enterRegion() or exitRegion().

Implemented in llvm::ScheduleDAGMILive, llvm::ScheduleDAGMI, llvm::DefaultVLIWScheduler, and llvm::VLIWMachineScheduler.

| void ScheduleDAGInstrs::startBlock | ( | MachineBasicBlock * | BB | ) | [virtual] |

startBlock - Prepare to perform scheduling in the given block.

Definition at line 175 of file ScheduleDAGInstrs.cpp.

References BB.

Referenced by llvm::VLIWPacketizerList::PacketizeMIs().

| void ScheduleDAGInstrs::startBlockForKills | ( | MachineBasicBlock * | BB | ) | [protected] |

PostRA helper for rewriting kill flags.

Initialize register live-range state for updating kills.

Definition at line 1063 of file ScheduleDAGInstrs.cpp.

References I, llvm::MCRegisterInfo::DiffListIterator::isValid(), LiveRegs, llvm::BitVector::reset(), llvm::BitVector::set(), llvm::MachineBasicBlock::succ_begin(), llvm::MachineBasicBlock::succ_end(), and llvm::ScheduleDAG::TRI.

Referenced by fixupKills().

| bool ScheduleDAGInstrs::toggleKillFlag | ( | MachineInstr * | MI, |

| MachineOperand & | MO | ||

| ) | [protected] |

Toggle a register operand kill flag.

Other adjustments may be made to the instruction if necessary. Return true if the operand has been deleted, false if not.

Definition at line 1081 of file ScheduleDAGInstrs.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::MachineOperand::getReg(), llvm::RegState::ImplicitDefine, llvm::MachineOperand::isKill(), llvm::MCRegisterInfo::DiffListIterator::isValid(), LiveRegs, llvm::ScheduleDAG::MF, llvm::MachineOperand::setIsKill(), llvm::BitVector::test(), and llvm::ScheduleDAG::TRI.

Referenced by fixupKills().

Member Data Documentation

MachineBasicBlock* llvm::ScheduleDAGInstrs::BB [protected] |

The block in which to insert instructions.

State specific to the current scheduling region. ------------------------------------------------

Definition at line 105 of file ScheduleDAGInstrs.h.

Referenced by addSchedBarrierDeps(), llvm::ScheduleDAGMILive::buildDAGWithRegPressure(), llvm::ScheduleDAGMILive::computeCyclicCriticalPath(), enterRegion(), finishBlock(), getDAGName(), llvm::ScheduleDAGMILive::initRegPressure(), llvm::ScheduleDAGMI::moveInstruction(), llvm::ScheduleDAGMI::placeDebugValues(), llvm::VLIWMachineScheduler::schedule(), startBlock(), and llvm::ScheduleDAGMILive::updatePressureDiffs().

bool llvm::ScheduleDAGInstrs::CanHandleTerminators [protected] |

The standard DAG builder does not normally include terminators as DAG nodes because it does not create the necessary dependencies to prevent reordering. A specialized scheduler can override TargetInstrInfo::isSchedulingBoundary then enable this flag to indicate it has taken responsibility for scheduling the terminator correctly.

Definition at line 99 of file ScheduleDAGInstrs.h.

Referenced by buildSchedGraph(), and llvm::DefaultVLIWScheduler::DefaultVLIWScheduler().

DbgValueVector llvm::ScheduleDAGInstrs::DbgValues [protected] |

Definition at line 148 of file ScheduleDAGInstrs.h.

Referenced by buildSchedGraph(), llvm::ScheduleDAGMI::placeDebugValues(), and ScheduleDAGInstrs().

Reg2SUnitsMap llvm::ScheduleDAGInstrs::Defs [protected] |

State internal to DAG building. ------------------------------- Defs, Uses - Remember where defs and uses of each register are as we iterate upward through the instructions. This is allocated here instead of inside BuildSchedGraph to avoid the need for it to be initialized and destructed for each block.

Definition at line 132 of file ScheduleDAGInstrs.h.

Referenced by addPhysRegDeps(), and buildSchedGraph().

MachineInstr* llvm::ScheduleDAGInstrs::FirstDbgValue [protected] |

Definition at line 149 of file ScheduleDAGInstrs.h.

Referenced by buildSchedGraph(), and llvm::ScheduleDAGMI::placeDebugValues().

bool llvm::ScheduleDAGInstrs::IsPostRA [protected] |

isPostRA flag indicates vregs cannot be present.

Definition at line 88 of file ScheduleDAGInstrs.h.

Referenced by addSchedBarrierDeps(), buildSchedGraph(), isPostRA(), and ScheduleDAGInstrs().

LiveIntervals* llvm::ScheduleDAGInstrs::LIS [protected] |

Live Intervals provides reaching defs in preRA scheduling.

Definition at line 82 of file ScheduleDAGInstrs.h.

Referenced by addVRegUseDeps(), getLIS(), and ScheduleDAGInstrs().

BitVector llvm::ScheduleDAGInstrs::LiveRegs [protected] |

Set of live physical registers for updating kill flags.

Definition at line 152 of file ScheduleDAGInstrs.h.

Referenced by fixupKills(), startBlockForKills(), and toggleKillFlag().

const MachineFrameInfo* llvm::ScheduleDAGInstrs::MFI [protected] |

Definition at line 79 of file ScheduleDAGInstrs.h.

Referenced by buildSchedGraph().

DenseMap<MachineInstr*, SUnit*> llvm::ScheduleDAGInstrs::MISUnitMap [protected] |

After calling BuildSchedGraph, each machine instruction in the current scheduling region is mapped to an SUnit.

Definition at line 118 of file ScheduleDAGInstrs.h.

Referenced by buildSchedGraph(), getSUnit(), and initSUnits().

const MachineLoopInfo* llvm::ScheduleDAGInstrs::MLI [protected] |

Definition at line 78 of file ScheduleDAGInstrs.h.

Referenced by llvm::VLIWMachineScheduler::schedule().

unsigned llvm::ScheduleDAGInstrs::NumRegionInstrs [protected] |

Instructions in this region (distance(RegionBegin, RegionEnd)).

Definition at line 114 of file ScheduleDAGInstrs.h.

Referenced by enterRegion(), and initSUnits().

std::vector<SUnit *> llvm::ScheduleDAGInstrs::PendingLoads [protected] |

PendingLoads - Remember where unknown loads are after the most recent unknown store, as we iterate. As with Defs and Uses, this is here to minimize construction/destruction.

Definition at line 141 of file ScheduleDAGInstrs.h.

Referenced by buildSchedGraph().

The beginning of the range to be scheduled.

Definition at line 108 of file ScheduleDAGInstrs.h.

Referenced by begin(), buildSchedGraph(), enterRegion(), llvm::ScheduleDAGMI::initQueues(), llvm::ScheduleDAGMILive::initRegPressure(), initSUnits(), llvm::ScheduleDAGMI::moveInstruction(), llvm::ScheduleDAGMI::placeDebugValues(), and llvm::ScheduleDAGMILive::schedule().

The end of the range to be scheduled.

Definition at line 111 of file ScheduleDAGInstrs.h.

Referenced by addSchedBarrierDeps(), llvm::ScheduleDAGMILive::buildDAGWithRegPressure(), buildSchedGraph(), end(), enterRegion(), llvm::ScheduleDAGMILive::enterRegion(), llvm::ScheduleDAGMI::initQueues(), llvm::ScheduleDAGMILive::initRegPressure(), initSUnits(), and llvm::ScheduleDAGMI::placeDebugValues().

bool llvm::ScheduleDAGInstrs::RemoveKillFlags [protected] |

True if the DAG builder should remove kill flags (in preparation for rescheduling).

Definition at line 92 of file ScheduleDAGInstrs.h.

Referenced by addPhysRegDeps().

TargetSchedModel llvm::ScheduleDAGInstrs::SchedModel [protected] |

TargetSchedModel provides an interface to the machine model.

Definition at line 85 of file ScheduleDAGInstrs.h.

Referenced by addPhysRegDataDeps(), addPhysRegDeps(), addVRegDefDeps(), addVRegUseDeps(), getSchedClass(), getSchedModel(), initSUnits(), and ScheduleDAGInstrs().

Reg2SUnitsMap llvm::ScheduleDAGInstrs::Uses [protected] |

Definition at line 133 of file ScheduleDAGInstrs.h.

Referenced by addPhysRegDataDeps(), addPhysRegDeps(), addSchedBarrierDeps(), and buildSchedGraph().

VReg2SUnitMap llvm::ScheduleDAGInstrs::VRegDefs [protected] |

Track the last instruction in this region defining each virtual register.

Definition at line 136 of file ScheduleDAGInstrs.h.

Referenced by addVRegDefDeps(), addVRegUseDeps(), and buildSchedGraph().

VReg2UseMap llvm::ScheduleDAGInstrs::VRegUses [protected] |

After calling BuildSchedGraph, each vreg used in the scheduling region is mapped to a set of SUnits. These include all local vreg uses, not just the uses for a singly defined vreg.

Definition at line 123 of file ScheduleDAGInstrs.h.

Referenced by addVRegUseDeps(), buildSchedGraph(), llvm::ScheduleDAGMILive::computeCyclicCriticalPath(), and llvm::ScheduleDAGMILive::updatePressureDiffs().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1