#include <SparcISelLowering.h>

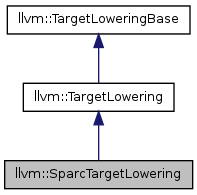

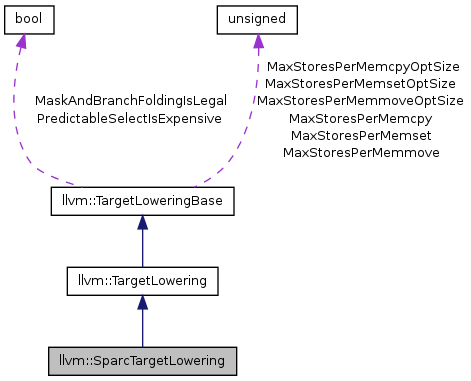

Detailed Description

Definition at line 54 of file SparcISelLowering.h.

Constructor & Destructor Documentation

Definition at line 1368 of file SparcISelLowering.cpp.

References llvm::RTLIB::ADD_F128, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::ATOMIC_CMP_SWAP, llvm::ISD::ATOMIC_FENCE, llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_STORE, llvm::ISD::ATOMIC_SWAP, llvm::ISD::BITCAST, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BRCOND, llvm::ISD::BRIND, llvm::ISD::BSWAP, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::ISD::ConstantPool, llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::TargetLoweringBase::Custom, llvm::RTLIB::DIV_F128, llvm::ISD::DYNAMIC_STACKALLOC, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::MVT::f128, llvm::MVT::f32, llvm::MVT::f64, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FCOPYSIGN, llvm::ISD::FCOS, llvm::ISD::FDIV, llvm::ISD::FMA, llvm::ISD::FMUL, llvm::ISD::FNEG, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::RTLIB::FPEXT_F32_F128, llvm::RTLIB::FPEXT_F64_F128, llvm::ISD::FPOW, llvm::RTLIB::FPROUND_F128_F32, llvm::RTLIB::FPROUND_F128_F64, llvm::RTLIB::FPTOSINT_F128_I32, llvm::RTLIB::FPTOSINT_F128_I64, llvm::RTLIB::FPTOUINT_F128_I32, llvm::RTLIB::FPTOUINT_F128_I64, llvm::ISD::FREM, llvm::ISD::FSIN, llvm::ISD::FSINCOS, llvm::ISD::FSQRT, llvm::ISD::FSUB, llvm::TargetLoweringBase::getPointerTy(), llvm::TargetMachine::getSubtarget(), llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::SparcSubtarget::hasHardQuad(), llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::SparcSubtarget::is64Bit(), llvm::SparcSubtarget::isV9(), llvm::TargetLoweringBase::Legal, llvm::ISD::LOAD, llvm::RTLIB::MUL_F128, llvm::ISD::MULHS, llvm::ISD::MULHU, llvm::MVT::Other, llvm::TargetLoweringBase::Promote, llvm::ISD::ROTL, llvm::ISD::ROTR, llvm::ISD::SDIVREM, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::ISD::SETCC, llvm::TargetLoweringBase::setExceptionPointerRegister(), llvm::TargetLoweringBase::setExceptionSelectorRegister(), llvm::TargetLoweringBase::setInsertFencesForAtomic(), llvm::TargetLoweringBase::setLibcallName(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setMinFunctionAlignment(), llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setStackPointerRegisterToSaveRestore(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SEXTLOAD, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SINT_TO_FP, llvm::RTLIB::SINTTOFP_I32_F128, llvm::RTLIB::SINTTOFP_I64_F128, llvm::ISD::SMUL_LOHI, llvm::ISD::SMULO, llvm::RTLIB::SQRT_F128, llvm::ISD::SRA_PARTS, llvm::ISD::SREM, llvm::ISD::SRL_PARTS, llvm::ISD::STACKRESTORE, llvm::ISD::STACKSAVE, llvm::ISD::STORE, llvm::RTLIB::SUB_F128, llvm::ISD::SUBC, llvm::ISD::SUBE, llvm::ISD::TRAP, llvm::ISD::UDIVREM, llvm::ISD::UINT_TO_FP, llvm::RTLIB::UINTTOFP_I32_F128, llvm::RTLIB::UINTTOFP_I64_F128, llvm::ISD::UMUL_LOHI, llvm::ISD::UMULO, llvm::ISD::UREM, llvm::SparcSubtarget::usePopc(), llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VAEND, and llvm::ISD::VASTART.

Member Function Documentation

| void SparcTargetLowering::computeKnownBitsForTargetNode | ( | const SDValue | Op, |

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [override, virtual] |

computeKnownBitsForTargetNode - Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

isMaskedValueZeroForTargetNode - Return true if 'Op & Mask' is known to be zero. Op is expected to be a target specific node. Used by DAG combiner.

Reimplemented from llvm::TargetLowering.

Definition at line 1712 of file SparcISelLowering.cpp.

References llvm::SelectionDAG::computeKnownBits(), llvm::APInt::getBitWidth(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SPISD::SELECT_FCC, llvm::SPISD::SELECT_ICC, and llvm::SPISD::SELECT_XCC.

| MachineBasicBlock * SparcTargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::TargetLowering.

Definition at line 2840 of file SparcISelLowering.cpp.

References expandAtomicRMW(), expandSelectCC(), llvm::MachineInstr::getOpcode(), llvm::SPCC::ICC_G, llvm::SPCC::ICC_GU, llvm::SPCC::ICC_LE, llvm::SPCC::ICC_LEU, and llvm_unreachable.

| MachineBasicBlock * SparcTargetLowering::expandAtomicRMW | ( | MachineInstr * | MI, |

| MachineBasicBlock * | BB, | ||

| unsigned | Opcode, | ||

| unsigned | CondCode = 0 |

||

| ) | const |

Definition at line 2964 of file SparcISelLowering.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SPCC::ICC_NE, llvm::MachineFunction::insert(), llvm::AArch64CC::MI, llvm::TargetOpcode::PHI, llvm::MachineInstrBuilder::setMemRefs(), llvm::MachineBasicBlock::splice(), TII, and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

Referenced by EmitInstrWithCustomInserter().

| MachineBasicBlock * SparcTargetLowering::expandSelectCC | ( | MachineInstr * | MI, |

| MachineBasicBlock * | BB, | ||

| unsigned | BROpcode | ||

| ) | const |

Definition at line 2903 of file SparcISelLowering.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), F(), llvm::MCInstrInfo::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getImm(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::MachineFunction::insert(), llvm::TargetOpcode::PHI, llvm::MachineBasicBlock::splice(), TII, and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

Referenced by EmitInstrWithCustomInserter().

| SparcTargetLowering::ConstraintType SparcTargetLowering::getConstraintType | ( | const std::string & | Constraint | ) | const [override, virtual] |

getConstraintType - Given a constraint letter, return the type of constraint it is for this target.

Reimplemented from llvm::TargetLowering.

Definition at line 3066 of file SparcISelLowering.cpp.

References llvm::TargetLowering::C_Other, and llvm::TargetLowering::C_RegisterClass.

| std::pair< unsigned, const TargetRegisterClass * > SparcTargetLowering::getRegForInlineAsmConstraint | ( | const std::string & | Constraint, |

| MVT | VT | ||

| ) | const [override, virtual] |

Given a physical register constraint (e.g. {edx}), return the register number and the register class for the register.

Given a register class constraint, like 'r', if this corresponds directly to an LLVM register class, return a register of 0 and the register class pointer.

This should only be used for C_Register constraints. On error, this returns a register number of 0 and a null register class pointer..

Reimplemented from llvm::TargetLowering.

Definition at line 3138 of file SparcISelLowering.cpp.

| MVT llvm::SparcTargetLowering::getScalarShiftAmountTy | ( | EVT | LHSTy | ) | const [inline, override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 87 of file SparcISelLowering.h.

References llvm::MVT::i32.

| EVT SparcTargetLowering::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [override, virtual] |

getSetCCResultType - Return the ISD::SETCC ValueType

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1702 of file SparcISelLowering.cpp.

References llvm::EVT::changeVectorElementTypeToInteger(), llvm::MVT::i32, and llvm::EVT::isVector().

| TargetLowering::ConstraintWeight SparcTargetLowering::getSingleConstraintMatchWeight | ( | AsmOperandInfo & | info, |

| const char * | constraint | ||

| ) | const [override, virtual] |

Examine constraint string and operand type and determine a weight value. The operand object must already have been set up with the operand type.

Examine constraint type and operand type and determine a weight value. This object must already have been set up with the operand type and the current alternative constraint selected.

Reimplemented from llvm::TargetLowering.

Definition at line 3080 of file SparcISelLowering.cpp.

References llvm::CallingConv::C, llvm::TargetLowering::AsmOperandInfo::CallOperandVal, llvm::TargetLowering::CW_Constant, llvm::TargetLowering::CW_Default, and llvm::TargetLowering::CW_Invalid.

| unsigned SparcTargetLowering::getSRetArgSize | ( | SelectionDAG & | DAG, |

| SDValue | Callee | ||

| ) | const |

Definition at line 971 of file SparcISelLowering.cpp.

References llvm::Function::arg_begin(), llvm::dyn_cast(), G, llvm::TargetLoweringBase::getDataLayout(), llvm::MachineFunction::getFunction(), llvm::Module::getFunction(), llvm::SelectionDAG::getMachineFunction(), llvm::GlobalValue::getParent(), llvm::DataLayout::getTypeAllocSize(), llvm::Function::hasStructRetAttr(), and isFP128ABICall().

Referenced by LowerCall_32().

| const char * SparcTargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

Definition at line 1675 of file SparcISelLowering.cpp.

References llvm::SPISD::BRFCC, llvm::SPISD::BRICC, llvm::SPISD::BRXCC, llvm::SPISD::CALL, llvm::SPISD::CMPFCC, llvm::SPISD::CMPICC, llvm::SPISD::FLUSHW, llvm::SPISD::FTOI, llvm::SPISD::FTOX, llvm::SPISD::GLOBAL_BASE_REG, llvm::SPISD::Hi, llvm::SPISD::ITOF, llvm::SPISD::Lo, llvm::SPISD::RET_FLAG, llvm::SPISD::SELECT_FCC, llvm::SPISD::SELECT_ICC, llvm::SPISD::SELECT_XCC, llvm::SPISD::TLS_ADD, llvm::SPISD::TLS_CALL, llvm::SPISD::TLS_LD, and llvm::SPISD::XTOF.

| bool SparcTargetLowering::isOffsetFoldingLegal | ( | const GlobalAddressSDNode * | GA | ) | const [override, virtual] |

Return true if folding a constant offset with the given GlobalAddress is legal. It is frequently not legal in PIC relocation models.

Reimplemented from llvm::TargetLowering.

Definition at line 3171 of file SparcISelLowering.cpp.

| void SparcTargetLowering::LowerAsmOperandForConstraint | ( | SDValue | Op, |

| std::string & | Constraint, | ||

| std::vector< SDValue > & | Ops, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerAsmOperandForConstraint - Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops.

Reimplemented from llvm::TargetLowering.

Definition at line 3107 of file SparcISelLowering.cpp.

References llvm::CallingConv::C, llvm::SDValue::getNode(), llvm::SelectionDAG::getTargetConstant(), and llvm::SDValue::getValueType().

| SDValue SparcTargetLowering::LowerBlockAddress | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1858 of file SparcISelLowering.cpp.

References makeAddress().

Referenced by LowerOperation().

| SDValue SparcTargetLowering::LowerCall | ( | TargetLowering::CallLoweringInfo & | , |

| SmallVectorImpl< SDValue > & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower calls into the the specified DAG. The outgoing arguments to the call are described by the Outs array, and the values to be returned by the call are described by the Ins array. The implementation should fill in the InVals array with legal-type return values from the call, and return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 653 of file SparcISelLowering.cpp.

References llvm::SparcSubtarget::is64Bit(), LowerCall_32(), and LowerCall_64().

| SDValue SparcTargetLowering::LowerCall_32 | ( | TargetLowering::CallLoweringInfo & | CLI, |

| SmallVectorImpl< SDValue > & | InVals | ||

| ) | const |

Definition at line 683 of file SparcISelLowering.cpp.

References llvm::ISD::ADD, llvm::CCValAssign::AExt, Align(), llvm::CCState::AnalyzeCallOperands(), llvm::CCState::AnalyzeCallResult(), llvm::ISD::ANY_EXTEND, llvm::CCValAssign::BCvt, llvm::ISD::BITCAST, llvm::SPISD::CALL, llvm::TargetLowering::CallLoweringInfo::CallConv, llvm::TargetLowering::CallLoweringInfo::Callee, llvm::TargetLowering::CallLoweringInfo::Chain, llvm::MachineFrameInfo::CreateStackObject(), llvm::SelectionDAG::CreateStackTemporary(), llvm::TargetLowering::CallLoweringInfo::CS, llvm::TargetLowering::CallLoweringInfo::DAG, llvm::TargetLowering::CallLoweringInfo::DL, llvm::SmallVectorBase::empty(), llvm::MVT::f32, llvm::MVT::f64, llvm::CCValAssign::Full, G, llvm::ISD::ArgFlagsTy::getByValAlign(), llvm::ISD::ArgFlagsTy::getByValSize(), llvm::SparcRegisterInfo::getCallPreservedMask(), llvm::SelectionDAG::getCALLSEQ_END(), llvm::SelectionDAG::getCALLSEQ_START(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getEntryNode(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getLoad(), llvm::CCValAssign::getLocInfo(), llvm::CCValAssign::getLocMemOffset(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getMemcpy(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getRegisterMask(), llvm::TargetMachine::getRelocationModel(), llvm::SparcRegisterInfo::getRTCallPreservedMask(), getSRetArgSize(), llvm::SelectionDAG::getStore(), llvm::TargetMachine::getSubtarget(), llvm::SelectionDAG::getTargetConstant(), llvm::SelectionDAG::getTargetExternalSymbol(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SDValue::getValue(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, hasReturnsTwiceAttr(), llvm::HexagonISD::Hi, llvm::MVT::i32, llvm::MipsISD::Ins, llvm::TargetLowering::CallLoweringInfo::Ins, llvm::ISD::ArgFlagsTy::isByVal(), llvm::CCValAssign::isMemLoc(), llvm::CCValAssign::isRegLoc(), llvm::ISD::ArgFlagsTy::isSRet(), llvm::TargetLowering::CallLoweringInfo::IsTailCall, llvm::TargetLowering::CallLoweringInfo::IsVarArg, llvm_unreachable, llvm::HexagonISD::Lo, llvm::CCValAssign::needsCustom(), llvm::MVT::Other, llvm::TargetLowering::CallLoweringInfo::Outs, llvm::TargetLowering::CallLoweringInfo::OutVals, llvm::Reloc::PIC_, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::CCValAssign::SExt, llvm::ISD::SIGN_EXTEND, llvm::SmallVectorTemplateCommon< T, typename >::size(), llvm::SmallVectorTemplateCommon< T >::size(), llvm::SPII::Store, toCallerWindow(), llvm::ISD::TokenFactor, llvm::SparcMCExpr::VK_Sparc_WPLT30, llvm::ISD::ZERO_EXTEND, and llvm::CCValAssign::ZExt.

Referenced by LowerCall().

| SDValue SparcTargetLowering::LowerCall_64 | ( | TargetLowering::CallLoweringInfo & | CLI, |

| SmallVectorImpl< SDValue > & | InVals | ||

| ) | const |

Definition at line 1053 of file SparcISelLowering.cpp.

References llvm::ISD::ADD, llvm::CCValAssign::AExt, llvm::CCState::AnalyzeCallOperands(), llvm::ISD::ANY_EXTEND, llvm::ISD::AssertSext, llvm::ISD::AssertZext, llvm::CCValAssign::BCvt, llvm::ISD::BITCAST, llvm::SPISD::CALL, llvm::TargetLowering::CallLoweringInfo::CallConv, llvm::TargetLowering::CallLoweringInfo::Callee, llvm::TargetLowering::CallLoweringInfo::Chain, llvm::ISD::CopyFromReg, llvm::TargetLowering::CallLoweringInfo::CS, llvm::TargetLowering::CallLoweringInfo::DAG, llvm::TargetLowering::CallLoweringInfo::DL, llvm::SmallVectorBase::empty(), llvm::MVT::f128, llvm::MVT::f32, fixupVariableFloatArgs(), llvm::CCValAssign::Full, G, llvm::SparcRegisterInfo::getCallPreservedMask(), llvm::SelectionDAG::getCALLSEQ_END(), llvm::SelectionDAG::getCALLSEQ_START(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getLoad(), llvm::CCValAssign::getLocInfo(), llvm::CCValAssign::getLocMemOffset(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOpcode(), llvm::SDValue::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getRegisterMask(), llvm::TargetMachine::getRelocationModel(), llvm::SparcRegisterInfo::getRTCallPreservedMask(), llvm::SparcSubtarget::getStackPointerBias(), llvm::SelectionDAG::getStore(), llvm::TargetMachine::getSubtarget(), llvm::SelectionDAG::getTargetExternalSymbol(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SDValue::getValue(), llvm::SelectionDAG::getValueType(), llvm::CCValAssign::getValVT(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, hasReturnsTwiceAttr(), llvm::MVT::i128, llvm::MVT::i32, llvm::MVT::i64, llvm::TargetLowering::CallLoweringInfo::Ins, llvm::CCValAssign::isExtInLoc(), llvm::CCValAssign::isMemLoc(), llvm::CCValAssign::isRegLoc(), llvm::TargetLowering::CallLoweringInfo::IsTailCall, llvm::TargetLowering::CallLoweringInfo::IsVarArg, llvm_unreachable, llvm::CCValAssign::needsCustom(), llvm::AArch64CC::NV, llvm::ISD::OR, llvm::MVT::Other, llvm::TargetLowering::CallLoweringInfo::Outs, llvm::TargetLowering::CallLoweringInfo::OutVals, llvm::Reloc::PIC_, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::RoundUpToAlignment(), llvm::CCValAssign::SExt, llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND, llvm::SmallVectorTemplateCommon< T, typename >::size(), llvm::SmallVectorTemplateCommon< T >::size(), llvm::ISD::SRL, llvm::SPII::Store, toCallerWindow(), llvm::ISD::TokenFactor, llvm::ISD::TRUNCATE, llvm::SparcMCExpr::VK_Sparc_WPLT30, llvm::ISD::ZERO_EXTEND, and llvm::CCValAssign::ZExt.

Referenced by LowerCall().

| SDValue SparcTargetLowering::LowerConstantPool | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1853 of file SparcISelLowering.cpp.

References makeAddress().

Referenced by LowerOperation().

| SDValue SparcTargetLowering::LowerF128_LibCallArg | ( | SDValue | Chain, |

| ArgListTy & | Args, | ||

| SDValue | Arg, | ||

| SDLoc | DL, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1969 of file SparcISelLowering.cpp.

References llvm::MachineFrameInfo::CreateStackObject(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::SelectionDAG::getMachineFunction(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getStore(), llvm::EVT::getTypeForEVT(), llvm::PointerType::getUnqual(), llvm::SDValue::getValueType(), llvm::Type::isFP128Ty(), llvm::TargetLowering::ArgListEntry::Node, and llvm::TargetLowering::ArgListEntry::Ty.

Referenced by LowerF128Compare(), and LowerF128Op().

| SDValue SparcTargetLowering::LowerF128Compare | ( | SDValue | LHS, |

| SDValue | RHS, | ||

| unsigned & | SPCC, | ||

| SDLoc | DL, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 2057 of file SparcISelLowering.cpp.

References llvm::ISD::AND, llvm::CallingConv::C, llvm::SPISD::CMPICC, llvm::SPCC::FCC_E, llvm::SPCC::FCC_G, llvm::SPCC::FCC_GE, llvm::SPCC::FCC_L, llvm::SPCC::FCC_LE, llvm::SPCC::FCC_LG, llvm::SPCC::FCC_NE, llvm::SPCC::FCC_O, llvm::SPCC::FCC_U, llvm::SPCC::FCC_UE, llvm::SPCC::FCC_UG, llvm::SPCC::FCC_UGE, llvm::SPCC::FCC_UL, llvm::SPCC::FCC_ULE, llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getEntryNode(), llvm::SelectionDAG::getExternalSymbol(), llvm::Type::getInt32Ty(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValueType(), llvm::MVT::Glue, llvm::SPCC::ICC_E, llvm::SPCC::ICC_G, llvm::SPCC::ICC_NE, llvm::SparcSubtarget::is64Bit(), llvm_unreachable, llvm::TargetLowering::LowerCallTo(), LowerF128_LibCallArg(), llvm::TargetLowering::CallLoweringInfo::setCallee(), llvm::TargetLowering::CallLoweringInfo::setChain(), and llvm::TargetLowering::CallLoweringInfo::setDebugLoc().

Referenced by LowerBR_CC(), and LowerSELECT_CC().

| SDValue SparcTargetLowering::LowerF128Op | ( | SDValue | Op, |

| SelectionDAG & | DAG, | ||

| const char * | LibFuncName, | ||

| unsigned | numArgs | ||

| ) | const |

Definition at line 2001 of file SparcISelLowering.cpp.

References llvm::CallingConv::C, llvm::MachineFrameInfo::CreateStackObject(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getEntryNode(), llvm::SelectionDAG::getExternalSymbol(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SDNode::getNumOperands(), llvm::SDValue::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::EVT::getTypeForEVT(), llvm::PointerType::getUnqual(), llvm::SDValue::getValueType(), llvm::Type::getVoidTy(), llvm::SparcSubtarget::is64Bit(), llvm::Type::isFP128Ty(), llvm::TargetLowering::ArgListEntry::isReturned, llvm::TargetLowering::ArgListEntry::isSRet, llvm::TargetLowering::LowerCallTo(), LowerF128_LibCallArg(), llvm::TargetLowering::ArgListEntry::Node, llvm::TargetLowering::CallLoweringInfo::setCallee(), llvm::TargetLowering::CallLoweringInfo::setChain(), llvm::TargetLowering::CallLoweringInfo::setDebugLoc(), and llvm::TargetLowering::ArgListEntry::Ty.

Referenced by LowerF128_FPEXTEND(), LowerF128_FPROUND(), LowerFP_TO_SINT(), LowerFP_TO_UINT(), LowerOperation(), LowerSINT_TO_FP(), LowerUINT_TO_FP(), and ReplaceNodeResults().

| SDValue SparcTargetLowering::LowerFormalArguments | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::InputArg > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | , | ||

| SmallVectorImpl< SDValue > & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower the incoming (formal) arguments, described by the Ins array, into the specified DAG. The implementation should fill in the InVals array with legal-type argument values, and return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 321 of file SparcISelLowering.cpp.

References llvm::SparcSubtarget::is64Bit(), LowerFormalArguments_32(), and LowerFormalArguments_64().

| SDValue SparcTargetLowering::LowerFormalArguments_32 | ( | SDValue | Chain, |

| CallingConv::ID | CallConv, | ||

| bool | isVarArg, | ||

| const SmallVectorImpl< ISD::InputArg > & | Ins, | ||

| SDLoc | dl, | ||

| SelectionDAG & | DAG, | ||

| SmallVectorImpl< SDValue > & | InVals | ||

| ) | const |

LowerFormalArguments32 - V8 uses a very simple ABI, where all values are passed in either one or two GPRs, including FP values. TODO: we should pass FP values in FP registers for fastcc functions.

Definition at line 339 of file SparcISelLowering.cpp.

References llvm::ISD::ADD, llvm::MachineFunction::addLiveIn(), llvm::MachineRegisterInfo::addLiveIn(), llvm::CCState::AnalyzeFormalArguments(), llvm::ISD::AssertSext, llvm::ISD::BITCAST, llvm::ISD::BUILD_PAIR, llvm::MachineFrameInfo::CreateFixedObject(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MVT::f32, llvm::MVT::f64, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getEntryNode(), llvm::SelectionDAG::getExtLoad(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getInfo(), llvm::SelectionDAG::getLoad(), llvm::CCValAssign::getLocMemOffset(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::MachineFunction::getRegInfo(), llvm::SelectionDAG::getRoot(), llvm::MVT::getSizeInBits(), llvm::SparcMachineFunctionInfo::getSRetReturnReg(), llvm::SelectionDAG::getStore(), llvm::SelectionDAG::getValueType(), llvm::CCValAssign::getValVT(), llvm::Function::hasStructRetAttr(), llvm::MVT::i32, llvm::MVT::i64, llvm::CCValAssign::isMemLoc(), llvm::CCValAssign::isRegLoc(), llvm::SPII::Load, llvm::CCValAssign::needsCustom(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::report_fatal_error(), llvm::SparcMachineFunctionInfo::setSRetReturnReg(), llvm::SparcMachineFunctionInfo::setVarArgsFrameOffset(), llvm::ISD::SEXTLOAD, llvm::ISD::TokenFactor, and llvm::ISD::TRUNCATE.

Referenced by LowerFormalArguments().

| SDValue SparcTargetLowering::LowerFormalArguments_64 | ( | SDValue | Chain, |

| CallingConv::ID | CallConv, | ||

| bool | isVarArg, | ||

| const SmallVectorImpl< ISD::InputArg > & | Ins, | ||

| SDLoc | dl, | ||

| SelectionDAG & | DAG, | ||

| SmallVectorImpl< SDValue > & | InVals | ||

| ) | const |

Definition at line 541 of file SparcISelLowering.cpp.

References llvm::MachineFunction::addLiveIn(), llvm::CCState::AnalyzeFormalArguments(), llvm::ISD::AssertSext, llvm::ISD::AssertZext, llvm::MachineFrameInfo::CreateFixedObject(), llvm::SmallVectorBase::empty(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::MachinePointerInfo::getFixedStack(), llvm::SelectionDAG::getFrameIndex(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getInfo(), llvm::SelectionDAG::getLoad(), llvm::CCValAssign::getLocInfo(), llvm::CCValAssign::getLocMemOffset(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::TargetLoweringBase::getRegClassFor(), llvm::MVT::getSizeInBits(), llvm::SparcSubtarget::getStackPointerBias(), llvm::SelectionDAG::getStore(), llvm::SelectionDAG::getValueType(), llvm::CCValAssign::getValVT(), llvm::MVT::i32, llvm::MVT::i64, llvm::CCValAssign::isExtInLoc(), llvm::CCValAssign::isMemLoc(), llvm::CCValAssign::isRegLoc(), llvm::CCValAssign::needsCustom(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::SparcMachineFunctionInfo::setVarArgsFrameOffset(), llvm::CCValAssign::SExt, llvm::SmallVectorTemplateCommon< T >::size(), llvm::ISD::SRL, llvm::ISD::TokenFactor, llvm::ISD::TRUNCATE, and llvm::CCValAssign::ZExt.

Referenced by LowerFormalArguments().

| SDValue SparcTargetLowering::LowerGlobalAddress | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1848 of file SparcISelLowering.cpp.

References makeAddress().

Referenced by LowerOperation().

| SDValue SparcTargetLowering::LowerGlobalTLSAddress | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1863 of file SparcISelLowering.cpp.

References llvm::ISD::ADD, llvm::CallingConv::C, llvm::TLSModel::GeneralDynamic, llvm::TargetRegisterInfo::getCallPreservedMask(), llvm::SelectionDAG::getCALLSEQ_END(), llvm::SelectionDAG::getCALLSEQ_START(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::SelectionDAG::getEntryNode(), llvm::MachineFunction::getFrameInfo(), llvm::GlobalAddressSDNode::getGlobal(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::SelectionDAG::getRegisterMask(), llvm::TargetMachine::getSubtargetImpl(), llvm::SelectionDAG::getTargetExternalSymbol(), llvm::TargetLoweringBase::getTargetMachine(), llvm::TargetMachine::getTLSModel(), llvm::SDValue::getValue(), llvm::SelectionDAG::getVTList(), llvm::SPISD::GLOBAL_BASE_REG, llvm::MVT::Glue, llvm::SPISD::Hi, llvm::HexagonISD::Hi, llvm::MVT::i64, llvm::TLSModel::InitialExec, llvm::SPISD::Lo, llvm::HexagonISD::Lo, llvm::TLSModel::LocalDynamic, llvm::TLSModel::LocalExec, makeHiLoPair(), llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::MipsISD::Ret, llvm::MachineFrameInfo::setHasCalls(), llvm::ARMBuildAttrs::Symbol, llvm::SPISD::TLS_ADD, llvm::SPISD::TLS_CALL, llvm::SPISD::TLS_LD, llvm::SparcMCExpr::VK_Sparc_TLS_GD_ADD, llvm::SparcMCExpr::VK_Sparc_TLS_GD_CALL, llvm::SparcMCExpr::VK_Sparc_TLS_GD_HI22, llvm::SparcMCExpr::VK_Sparc_TLS_GD_LO10, llvm::SparcMCExpr::VK_Sparc_TLS_IE_ADD, llvm::SparcMCExpr::VK_Sparc_TLS_IE_HI22, llvm::SparcMCExpr::VK_Sparc_TLS_IE_LD, llvm::SparcMCExpr::VK_Sparc_TLS_IE_LDX, llvm::SparcMCExpr::VK_Sparc_TLS_IE_LO10, llvm::SparcMCExpr::VK_Sparc_TLS_LDM_ADD, llvm::SparcMCExpr::VK_Sparc_TLS_LDM_CALL, llvm::SparcMCExpr::VK_Sparc_TLS_LDM_HI22, llvm::SparcMCExpr::VK_Sparc_TLS_LDM_LO10, llvm::SparcMCExpr::VK_Sparc_TLS_LDO_ADD, llvm::SparcMCExpr::VK_Sparc_TLS_LDO_HIX22, llvm::SparcMCExpr::VK_Sparc_TLS_LDO_LOX10, llvm::SparcMCExpr::VK_Sparc_TLS_LE_HIX22, llvm::SparcMCExpr::VK_Sparc_TLS_LE_LOX10, withTargetFlags(), and llvm::ISD::XOR.

Referenced by LowerOperation().

| SDValue SparcTargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

This callback is invoked for operations that are unsupported by the target, which are registered to use 'custom' lowering, and whose defined values are all legal. If the target has no operations that require custom lowering, it need not implement this. The default implementation of this aborts.

Reimplemented from llvm::TargetLowering.

Definition at line 2779 of file SparcISelLowering.cpp.

References llvm::RTLIB::ADD_F128, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_STORE, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::ConstantPool, llvm::RTLIB::DIV_F128, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FDIV, llvm::ISD::FMUL, llvm::ISD::FNEG, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FRAMEADDR, llvm::ISD::FSQRT, llvm::ISD::FSUB, llvm::TargetLoweringBase::getLibcallName(), llvm::SDValue::getOpcode(), llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::SparcSubtarget::hasHardQuad(), llvm::SparcSubtarget::isV9(), llvm_unreachable, llvm::ISD::LOAD, LowerADDC_ADDE_SUBC_SUBE(), LowerATOMIC_LOAD_STORE(), LowerBlockAddress(), LowerBR_CC(), LowerConstantPool(), LowerDYNAMIC_STACKALLOC(), LowerF128_FPEXTEND(), LowerF128_FPROUND(), LowerF128Load(), LowerF128Op(), LowerF128Store(), LowerFNEGorFABS(), LowerFP_TO_SINT(), LowerFP_TO_UINT(), LowerFRAMEADDR(), LowerGlobalAddress(), LowerGlobalTLSAddress(), LowerRETURNADDR(), LowerSELECT_CC(), LowerSINT_TO_FP(), LowerUINT_TO_FP(), LowerUMULO_SMULO(), LowerVAARG(), LowerVASTART(), llvm::RTLIB::MUL_F128, llvm::ISD::RETURNADDR, llvm::ISD::SELECT_CC, llvm::ISD::SINT_TO_FP, llvm::ISD::SMULO, llvm::RTLIB::SQRT_F128, llvm::ISD::STORE, llvm::RTLIB::SUB_F128, llvm::ISD::SUBC, llvm::ISD::SUBE, llvm::ISD::UINT_TO_FP, llvm::ISD::UMULO, llvm::ISD::VAARG, and llvm::ISD::VASTART.

| SDValue SparcTargetLowering::LowerReturn | ( | SDValue | , |

| CallingConv::ID | , | ||

| bool | , | ||

| const SmallVectorImpl< ISD::OutputArg > & | , | ||

| const SmallVectorImpl< SDValue > & | , | ||

| SDLoc | , | ||

| SelectionDAG & | |||

| ) | const [override, virtual] |

This hook must be implemented to lower outgoing return values, described by the Outs array, into the specified DAG. The implementation should return the resulting token chain value.

Reimplemented from llvm::TargetLowering.

Definition at line 171 of file SparcISelLowering.cpp.

References llvm::SparcSubtarget::is64Bit(), LowerReturn_32(), and LowerReturn_64().

| SDValue SparcTargetLowering::LowerReturn_32 | ( | SDValue | Chain, |

| CallingConv::ID | CallConv, | ||

| bool | IsVarArg, | ||

| const SmallVectorImpl< ISD::OutputArg > & | Outs, | ||

| const SmallVectorImpl< SDValue > & | OutVals, | ||

| SDLoc | DL, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 182 of file SparcISelLowering.cpp.

References llvm::CCState::AnalyzeReturn(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyFromReg(), llvm::SelectionDAG::getCopyToReg(), llvm::MachineFunction::getFunction(), llvm::MachineFunction::getInfo(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::SparcMachineFunctionInfo::getSRetReturnReg(), llvm::SDValue::getValue(), llvm::Function::hasStructRetAttr(), llvm::MVT::i32, llvm::CCValAssign::isRegLoc(), llvm_unreachable, llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SPISD::RET_FLAG, and llvm::SmallVectorTemplateCommon< T >::size().

Referenced by LowerReturn().

| SDValue SparcTargetLowering::LowerReturn_64 | ( | SDValue | Chain, |

| CallingConv::ID | CallConv, | ||

| bool | IsVarArg, | ||

| const SmallVectorImpl< ISD::OutputArg > & | Outs, | ||

| const SmallVectorImpl< SDValue > & | OutVals, | ||

| SDLoc | DL, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 244 of file SparcISelLowering.cpp.

References llvm::CCValAssign::AExt, llvm::CCState::AnalyzeReturn(), llvm::ISD::ANY_EXTEND, llvm::CCValAssign::Full, llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getCopyToReg(), llvm::CCValAssign::getLocInfo(), llvm::CCValAssign::getLocReg(), llvm::CCValAssign::getLocVT(), llvm::SelectionDAG::getMachineFunction(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SelectionDAG::getRegister(), llvm::SDValue::getValue(), llvm::CCValAssign::getValVT(), llvm::MVT::i32, llvm::MVT::i64, llvm::CCValAssign::isRegLoc(), llvm_unreachable, llvm::CCValAssign::needsCustom(), llvm::AArch64CC::NV, llvm::ISD::OR, llvm::MVT::Other, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::SPISD::RET_FLAG, llvm::CCValAssign::SExt, llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND, llvm::SmallVectorTemplateCommon< T >::size(), llvm::ISD::ZERO_EXTEND, and llvm::CCValAssign::ZExt.

Referenced by LowerReturn().

| SDValue SparcTargetLowering::makeAddress | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1800 of file SparcISelLowering.cpp.

References llvm::ISD::ADD, llvm::TargetMachine::getCodeModel(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getEntryNode(), llvm::MachineFunction::getFrameInfo(), llvm::MachinePointerInfo::getGOT(), llvm::SelectionDAG::getLoad(), llvm::SelectionDAG::getMachineFunction(), llvm::SelectionDAG::getNode(), llvm::TargetLoweringBase::getPointerTy(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SPISD::GLOBAL_BASE_REG, llvm::HexagonISD::Hi, llvm::MVT::i32, llvm::CodeModel::Large, llvm_unreachable, llvm::SPISD::Lo, llvm::HexagonISD::Lo, makeHiLoPair(), llvm::CodeModel::Medium, llvm::Reloc::PIC_, llvm::MachineFrameInfo::setHasCalls(), llvm::ISD::SHL, llvm::CodeModel::Small, llvm::SparcMCExpr::VK_Sparc_GOT10, llvm::SparcMCExpr::VK_Sparc_GOT22, llvm::SparcMCExpr::VK_Sparc_H44, llvm::SparcMCExpr::VK_Sparc_HH, llvm::SparcMCExpr::VK_Sparc_HI, llvm::SparcMCExpr::VK_Sparc_HM, llvm::SparcMCExpr::VK_Sparc_L44, llvm::SparcMCExpr::VK_Sparc_LO, llvm::SparcMCExpr::VK_Sparc_M44, and withTargetFlags().

Referenced by LowerBlockAddress(), LowerConstantPool(), and LowerGlobalAddress().

| SDValue SparcTargetLowering::makeHiLoPair | ( | SDValue | Op, |

| unsigned | HiTF, | ||

| unsigned | LoTF, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1788 of file SparcISelLowering.cpp.

References llvm::ISD::ADD, llvm::SelectionDAG::getNode(), llvm::SDValue::getValueType(), llvm::SPISD::Hi, llvm::HexagonISD::Hi, llvm::SPISD::Lo, llvm::HexagonISD::Lo, and withTargetFlags().

Referenced by LowerGlobalTLSAddress(), and makeAddress().

| void SparcTargetLowering::ReplaceNodeResults | ( | SDNode * | , |

| SmallVectorImpl< SDValue > & | , | ||

| SelectionDAG & | |||

| ) | const [override, virtual] |

This callback is invoked when a node result type is illegal for the target, and the operation was registered to use 'custom' lowering for that result type. The target places new result values for the node in Results (their number and types must exactly match those of the original return values of the node), or leaves Results empty, which indicates that the node is not to be custom lowered after all.

If the target has no operations that require custom lowering, it need not implement this. The default implementation aborts.

Reimplemented from llvm::TargetLowering.

Definition at line 3176 of file SparcISelLowering.cpp.

References llvm::MVT::f128, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::RTLIB::FPTOSINT_F128_I64, llvm::RTLIB::FPTOUINT_F128_I64, llvm::TargetLoweringBase::getLibcallName(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::MVT::i64, llvm_unreachable, LowerF128Op(), llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::ISD::SINT_TO_FP, llvm::RTLIB::SINTTOFP_I64_F128, llvm::ISD::UINT_TO_FP, llvm::RTLIB::UINTTOFP_I64_F128, and llvm::RTLIB::UNKNOWN_LIBCALL.

| bool llvm::SparcTargetLowering::ShouldShrinkFPConstant | ( | EVT | ) | const [inline, override, virtual] |

If true, then instruction selection should seek to shrink the FP constant of the specified type to a smaller type in order to save space and / or reduce runtime.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 159 of file SparcISelLowering.h.

References llvm::MVT::f128.

| SDValue SparcTargetLowering::withTargetFlags | ( | SDValue | Op, |

| unsigned | TF, | ||

| SelectionDAG & | DAG | ||

| ) | const |

Definition at line 1759 of file SparcISelLowering.cpp.

References llvm::SelectionDAG::getTargetBlockAddress(), llvm::SelectionDAG::getTargetConstantPool(), llvm::SelectionDAG::getTargetExternalSymbol(), llvm::SelectionDAG::getTargetGlobalAddress(), llvm::SDValue::getValueType(), and llvm_unreachable.

Referenced by LowerGlobalTLSAddress(), makeAddress(), and makeHiLoPair().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1