#include <ARMBaseInstrInfo.h>

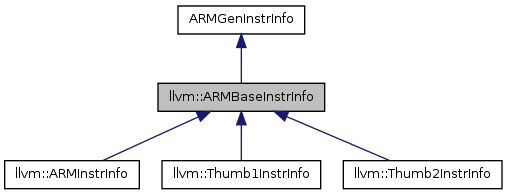

Detailed Description

Definition at line 31 of file ARMBaseInstrInfo.h.

Constructor & Destructor Documentation

| ARMBaseInstrInfo::ARMBaseInstrInfo | ( | const ARMSubtarget & | STI | ) | [explicit, protected] |

Definition at line 93 of file ARMBaseInstrInfo.cpp.

References ARM_MLxTable, llvm::array_lengthof(), llvm::SmallSet< T, N, C >::insert(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::insert(), and ARM_MLxEntry::MLxOpc.

Member Function Documentation

| const MachineInstrBuilder & ARMBaseInstrInfo::AddDReg | ( | MachineInstrBuilder & | MIB, |

| unsigned | Reg, | ||

| unsigned | SubIdx, | ||

| unsigned | State, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const |

Definition at line 827 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::MCRegisterInfo::getSubReg(), and llvm::TargetRegisterInfo::isPhysicalRegister().

Referenced by llvm::Thumb2InstrInfo::loadRegFromStackSlot(), loadRegFromStackSlot(), llvm::Thumb2InstrInfo::storeRegToStackSlot(), and storeRegToStackSlot().

| bool ARMBaseInstrInfo::AnalyzeBranch | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock *& | TBB, | ||

| MachineBasicBlock *& | FBB, | ||

| SmallVectorImpl< MachineOperand > & | Cond, | ||

| bool | AllowModify = false |

||

| ) | const [override] |

Definition at line 276 of file ARMBaseInstrInfo.cpp.

References llvm::MachineBasicBlock::begin(), llvm::SmallVectorImpl< T >::clear(), llvm::SmallVectorBase::empty(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), I, llvm::isCondBranchOpcode(), llvm::isIndirectBranchOpcode(), llvm::isJumpTableBranchOpcode(), isPredicated(), llvm::isUncondBranchOpcode(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

| bool ARMBaseInstrInfo::analyzeCompare | ( | const MachineInstr * | MI, |

| unsigned & | SrcReg, | ||

| unsigned & | SrcReg2, | ||

| int & | CmpMask, | ||

| int & | CmpValue | ||

| ) | const [override] |

analyzeCompare - For a comparison instruction, return the source registers in SrcReg and SrcReg2 if having two register operands, and the value it compares against in CmpValue. Return true if the comparison instruction can be analyzed.

Definition at line 2198 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::MachineOperand::getReg().

| bool ARMBaseInstrInfo::analyzeSelect | ( | const MachineInstr * | MI, |

| SmallVectorImpl< MachineOperand > & | Cond, | ||

| unsigned & | TrueOp, | ||

| unsigned & | FalseOp, | ||

| bool & | Optimizable | ||

| ) | const [override] |

Definition at line 1777 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), and llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back().

| bool ARMBaseInstrInfo::areLoadsFromSameBasePtr | ( | SDNode * | Load1, |

| SDNode * | Load2, | ||

| int64_t & | Offset1, | ||

| int64_t & | Offset2 | ||

| ) | const [override] |

areLoadsFromSameBasePtr - This is used by the pre-regalloc scheduler to determine if two loads are loading from the same base address. It should only return true if the base pointers are the same and the only differences between the two addresses is the offset. It also returns the offsets by reference.

areLoadsFromSameBasePtr - This is used by the pre-regalloc scheduler to determine if two loads are loading from the same base address. It should only return true if the base pointers are the same and the only differences between the two addresses is the offset. It also returns the offsets by reference.

FIXME: remove this in favor of the MachineInstr interface once pre-RA-sched is permanently disabled.

Definition at line 1485 of file ARMBaseInstrInfo.cpp.

References llvm::SDNode::getMachineOpcode(), llvm::SDNode::getOperand(), llvm::SDNode::isMachineOpcode(), and llvm::ARMSubtarget::isThumb1Only().

| void ARMBaseInstrInfo::breakPartialRegDependency | ( | MachineBasicBlock::iterator | MI, |

| unsigned | OpNum, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Definition at line 4419 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultPred(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstr::addRegisterKilled(), llvm::BuildMI(), contains(), llvm::MachineOperand::getReg(), llvm::TargetRegisterInfo::isPhysicalRegister(), llvm::MCRegisterInfo::isSuperRegister(), and llvm::AArch64CC::MI.

| bool llvm::ARMBaseInstrInfo::canCauseFpMLxStall | ( | unsigned | Opcode | ) | const [inline] |

canCauseFpMLxStall - Return true if an instruction of the specified opcode will cause stalls when scheduled after (within 4-cycle window) a fp MLA / MLS instruction.

Definition at line 372 of file ARMBaseInstrInfo.h.

References llvm::SmallSet< T, N, C >::count().

Referenced by llvm::ARMHazardRecognizer::getHazardType().

| MachineInstr * ARMBaseInstrInfo::commuteInstruction | ( | MachineInstr * | MI, |

| bool | NewMI = false |

||

| ) | const [override] |

commuteInstruction - Handle commutable instructions.

Definition at line 1716 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, llvm::MachineInstr::findFirstPredOperandIdx(), llvm::getInstrPredicate(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::ARMCC::getOppositeCondition(), and llvm::AArch64CC::MI.

| MachineInstr * ARMBaseInstrInfo::convertToThreeAddress | ( | MachineFunction::iterator & | MFI, |

| MachineBasicBlock::iterator & | MBBI, | ||

| LiveVariables * | LV | ||

| ) | const [override] |

Definition at line 126 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::ARMII::AddrMode2, llvm::ARMII::AddrMode3, llvm::ARMII::AddrModeMask, llvm::LiveVariables::addVirtualRegisterDead(), llvm::LiveVariables::addVirtualRegisterKilled(), llvm::BuildMI(), EnableARM3Addr, llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2Op(), llvm::ARM_AM::getAM2ShiftOpc(), llvm::ARM_AM::getAM3Offset(), llvm::ARM_AM::getAM3Op(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::ARM_AM::getSOImmVal(), llvm::ARM_AM::getSORegOpc(), getUnindexedOpcode(), llvm::LiveVariables::getVarInfo(), llvm::ARMII::IndexModeMask, llvm::ARMII::IndexModePost, llvm::ARMII::IndexModePre, llvm::ARMII::IndexModeShift, llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isKill(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isUse(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::LiveVariables::VarInfo::Kills, llvm_unreachable, llvm::MachineInstr::mayStore(), llvm::AArch64CC::MI, llvm::MachineInstr::readsRegister(), llvm::LiveVariables::VarInfo::removeKill(), llvm::MachineOperand::setIsDead(), sub(), and llvm::MCInstrDesc::TSFlags.

| void ARMBaseInstrInfo::copyPhysReg | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | I, | ||

| DebugLoc | DL, | ||

| unsigned | DestReg, | ||

| unsigned | SrcReg, | ||

| bool | KillSrc | ||

| ) | const [override] |

Reimplemented in llvm::Thumb2InstrInfo, and llvm::Thumb1InstrInfo.

Definition at line 701 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultCC(), llvm::AddDefaultPred(), llvm::MachineInstrBuilder::addReg(), llvm::MachineInstr::addRegisterDefined(), llvm::MachineInstr::addRegisterKilled(), llvm::BuildMI(), contains(), llvm::SmallSet< T, N, C >::count(), llvm::getKillRegState(), getRegisterInfo(), llvm::MCRegisterInfo::getSubReg(), llvm::SmallSet< T, N, C >::insert(), llvm::ARMSubtarget::isFPOnlySP(), llvm::ARMSubtarget::isThumb2(), and llvm::TargetRegisterInfo::regsOverlap().

| ScheduleHazardRecognizer * ARMBaseInstrInfo::CreateTargetHazardRecognizer | ( | const TargetSubtargetInfo * | STI, |

| const ScheduleDAG * | DAG | ||

| ) | const [override] |

Definition at line 107 of file ARMBaseInstrInfo.cpp.

| ScheduleHazardRecognizer * ARMBaseInstrInfo::CreateTargetPostRAHazardRecognizer | ( | const InstrItineraryData * | II, |

| const ScheduleDAG * | DAG | ||

| ) | const [override] |

Definition at line 118 of file ARMBaseInstrInfo.cpp.

References llvm::ARMSubtarget::hasVFP2(), and llvm::ARMSubtarget::isThumb2().

| bool ARMBaseInstrInfo::DefinesPredicate | ( | MachineInstr * | MI, |

| std::vector< MachineOperand > & | Pred | ||

| ) | const [override] |

Definition at line 506 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::clobbersPhysReg(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::isDef(), llvm::MachineOperand::isReg(), and llvm::MachineOperand::isRegMask().

| MachineInstr * ARMBaseInstrInfo::duplicate | ( | MachineInstr * | Orig, |

| MachineFunction & | MF | ||

| ) | const [override] |

Definition at line 1375 of file ARMBaseInstrInfo.cpp.

References duplicateCPV(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::AArch64CC::MI, llvm::MachineOperand::setImm(), and llvm::MachineOperand::setIndex().

| void ARMBaseInstrInfo::expandLoadStackGuardBase | ( | MachineBasicBlock::iterator | MI, |

| unsigned | LoadImmOpc, | ||

| unsigned | LoadOpc, | ||

| Reloc::Model | RM | ||

| ) | const [protected] |

Definition at line 3995 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultPred(), llvm::MachineInstrBuilder::addGlobalAddress(), llvm::BuildMI(), llvm::MachinePointerInfo::getGOT(), llvm::MachineBasicBlock::getParent(), llvm::ARMSubtarget::GVIsIndirectSymbol(), llvm::RegState::Kill, llvm::ARMII::MO_NONLAZY, llvm::MachineMemOperand::MOInvariant, and llvm::MachineMemOperand::MOLoad.

| bool ARMBaseInstrInfo::expandPostRAPseudo | ( | MachineBasicBlock::iterator | MI | ) | const [override] |

Definition at line 1221 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultPred(), contains(), llvm::dbgs(), DEBUG, llvm::MachineInstr::findRegisterDefOperandIdx(), llvm::TargetRegisterInfo::getMatchingSuperReg(), getRegisterInfo(), llvm::TargetMachine::getRelocationModel(), getSubtarget(), llvm::MachineFunction::getTarget(), llvm::RegState::Implicit, llvm::ARMSubtarget::isCortexA15(), llvm::ARMSubtarget::isFPOnlySP(), llvm::TargetOpcode::LOAD_STACK_GUARD, llvm::Triple::MachO, llvm::AArch64CC::MI, llvm::NVPTX::PTXCvtMode::RM, and WidenVMOVS.

| bool ARMBaseInstrInfo::FoldImmediate | ( | MachineInstr * | UseMI, |

| MachineInstr * | DefMI, | ||

| unsigned | Reg, | ||

| MachineRegisterInfo * | MRI | ||

| ) | const [override] |

FoldImmediate - 'Reg' is known to be defined by a move immediate instruction, try to fold the immediate into the use instruction.

Definition at line 2547 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultCC(), llvm::AddDefaultPred(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineOperand::ChangeToImmediate(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::getKillRegState(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::ARM_AM::getSOImmTwoPartFirst(), llvm::ARM_AM::getSOImmTwoPartSecond(), llvm::ARM_AM::getT2SOImmTwoPartFirst(), llvm::ARM_AM::getT2SOImmTwoPartSecond(), llvm::MachineRegisterInfo::hasOneNonDBGUse(), llvm::MCInstrDesc::hasOptionalDef(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isImm(), llvm::MachineOperand::isKill(), llvm::ARM_AM::isSOImmTwoPartVal(), llvm::ARM_AM::isT2SOImmTwoPartVal(), llvm::MachineInstr::setDesc(), llvm::MachineOperand::setIsKill(), and llvm::MachineOperand::setReg().

| std::pair< uint16_t, uint16_t > ARMBaseInstrInfo::getExecutionDomain | ( | const MachineInstr * | MI | ) | const [override] |

VFP/NEON execution domains.

Definition at line 4061 of file ARMBaseInstrInfo.cpp.

References llvm::ARMII::DomainMask, llvm::ARMII::DomainNEON, llvm::ARMII::DomainNEONA8, llvm::ARMII::DomainVFP, ExeGeneric, ExeNEON, ExeVFP, llvm::MachineInstr::getDesc(), llvm::MachineInstr::getOpcode(), llvm::ARMSubtarget::isCortexA8(), llvm::ARMSubtarget::isCortexA9(), isPredicated(), and llvm::MCInstrDesc::TSFlags.

| bool ARMBaseInstrInfo::getExtractSubregLikeInputs | ( | const MachineInstr & | MI, |

| unsigned | DefIdx, | ||

| RegSubRegPairAndIdx & | InputReg | ||

| ) | const [override, protected] |

Build the equivalent inputs of a EXTRACT_SUBREG for the given MI and DefIdx. [out] InputReg of the equivalent EXTRACT_SUBREG. E.g., EXTRACT_SUBREG vreg1:sub1, sub0, sub1 would produce:

- vreg1:sub1, sub0

- Returns:

- true if it is possible to build such an input sequence with the pair

MI,DefIdx. False otherwise.

- Precondition:

- MI.isExtractSubregLike().

Definition at line 4519 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineInstr::isExtractSubregLike(), llvm_unreachable, llvm::MachineOperand::Reg, and llvm::ARMISD::VMOVRRD.

| bool ARMBaseInstrInfo::getInsertSubregLikeInputs | ( | const MachineInstr & | MI, |

| unsigned | DefIdx, | ||

| RegSubRegPair & | BaseReg, | ||

| RegSubRegPairAndIdx & | InsertedReg | ||

| ) | const [override, protected] |

Build the equivalent inputs of a INSERT_SUBREG for the given MI and DefIdx. [out] BaseReg and [out] InsertedReg contain the equivalent inputs of INSERT_SUBREG. E.g., INSERT_SUBREG vreg0:sub0, vreg1:sub1, sub3 would produce:

- BaseReg: vreg0:sub0

- InsertedReg: vreg1:sub1, sub3

- Returns:

- true if it is possible to build such an input sequence with the pair

MI,DefIdx. False otherwise.

- Precondition:

- MI.isInsertSubregLike().

Definition at line 4540 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineInstr::isInsertSubregLike(), llvm_unreachable, and llvm::MachineOperand::Reg.

| unsigned ARMBaseInstrInfo::GetInstSizeInBytes | ( | const MachineInstr * | MI | ) | const [virtual] |

GetInstSize - Returns the size of the specified MachineInstr.

GetInstSize - Return the size of the specified MachineInstr.

Definition at line 609 of file ARMBaseInstrInfo.cpp.

References llvm::TargetOpcode::BUNDLE, llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::MachineFunction::getJumpTableInfo(), llvm::MachineJumpTableInfo::getJumpTables(), llvm::TargetMachine::getMCAsmInfo(), getNumJTEntries(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MCInstrDesc::getSize(), llvm::MachineOperand::getSymbolName(), llvm::MachineFunction::getTarget(), llvm::ISD::INLINEASM, and llvm::MachineInstr::isPredicable().

Referenced by GetFunctionSizeInBytes().

| unsigned ARMBaseInstrInfo::getNumLDMAddresses | ( | const MachineInstr * | MI | ) | const |

Get the number of addresses by LDM or VLDM or zero for unknown.

Definition at line 2908 of file ARMBaseInstrInfo.cpp.

References I, llvm::MachineInstr::memoperands_begin(), and llvm::MachineInstr::memoperands_end().

| unsigned ARMBaseInstrInfo::getNumMicroOps | ( | const InstrItineraryData * | ItinData, |

| const MachineInstr * | MI | ||

| ) | const [override] |

Definition at line 2918 of file ARMBaseInstrInfo.cpp.

References llvm::tgtok::Class, llvm::MachineInstr::getDesc(), llvm::InstrItineraryData::getNumMicroOps(), getNumMicroOpsSwiftLdSt(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MCInstrDesc::getSchedClass(), llvm::MachineInstr::hasOneMemOperand(), llvm::ARMSubtarget::isCortexA7(), llvm::ARMSubtarget::isCortexA8(), llvm::InstrItineraryData::isEmpty(), llvm::ARMSubtarget::isLikeA9(), llvm::ARMSubtarget::isSwift(), llvm_unreachable, llvm::MCInstrDesc::mayLoad(), llvm::MCInstrDesc::mayStore(), and llvm::MachineInstr::memoperands_begin().

| int ARMBaseInstrInfo::getOperandLatency | ( | const InstrItineraryData * | ItinData, |

| const MachineInstr * | DefMI, | ||

| unsigned | DefIdx, | ||

| const MachineInstr * | UseMI, | ||

| unsigned | UseIdx | ||

| ) | const [override] |

Definition at line 3554 of file ARMBaseInstrInfo.cpp.

References adjustDefLatency(), llvm::ARMISD::FMSTAT, llvm::AttributeSet::FunctionIndex, llvm::Function::getAttributes(), getBundledDefMI(), getBundledUseMI(), llvm::MachineInstr::getDesc(), llvm::MachineFunction::getFunction(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), llvm::MachineInstr::hasOneMemOperand(), llvm::MachineInstr::isBranch(), llvm::MachineInstr::isBundle(), llvm::MachineInstr::isCopyLike(), llvm::InstrItineraryData::isEmpty(), llvm::MachineOperand::isImplicit(), llvm::MachineInstr::isImplicitDef(), llvm::MachineInstr::isInsertSubreg(), llvm::ARMSubtarget::isLikeA9(), llvm::MachineInstr::isRegSequence(), llvm::ARMSubtarget::isThumb2(), llvm::MachineInstr::memoperands_begin(), and llvm::Attribute::OptimizeForSize.

Referenced by getOperandLatency().

| int ARMBaseInstrInfo::getOperandLatency | ( | const InstrItineraryData * | ItinData, |

| SDNode * | DefNode, | ||

| unsigned | DefIdx, | ||

| SDNode * | UseNode, | ||

| unsigned | UseIdx | ||

| ) | const [override] |

Definition at line 3645 of file ARMBaseInstrInfo.cpp.

References llvm::dyn_cast(), llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2ShiftOpc(), llvm::SDNode::getMachineOpcode(), llvm::MCInstrDesc::getOpcode(), llvm::SDNode::getOperand(), llvm::InstrItineraryData::getOperandCycle(), getOperandLatency(), llvm::MCInstrDesc::getSchedClass(), llvm::ARMSubtarget::isCortexA7(), llvm::ARMSubtarget::isCortexA8(), llvm::InstrItineraryData::isEmpty(), llvm::ARMSubtarget::isLikeA9(), llvm::SDNode::isMachineOpcode(), llvm::ARMSubtarget::isSwift(), llvm::ARM_AM::lsl, llvm::ARM_AM::lsr, llvm::MCInstrDesc::mayLoad(), llvm::MachineSDNode::memoperands_begin(), llvm::MachineSDNode::memoperands_empty(), and llvm::MCInstrDesc::Opcode.

| unsigned ARMBaseInstrInfo::getPartialRegUpdateClearance | ( | const MachineInstr * | MI, |

| unsigned | OpNum, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Definition at line 4357 of file ARMBaseInstrInfo.cpp.

References contains(), llvm::MachineInstr::definesRegister(), llvm::MachineInstr::findRegisterUseOperandIdx(), llvm::TargetRegisterInfo::getMatchingSuperReg(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::ARMSubtarget::isCortexA15(), llvm::ARMSubtarget::isSwift(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::MachineOperand::readsReg(), llvm::MachineInstr::readsVirtualRegister(), and SwiftPartialUpdateClearance.

| ARMCC::CondCodes llvm::ARMBaseInstrInfo::getPredicate | ( | const MachineInstr * | MI | ) | const [inline] |

Definition at line 129 of file ARMBaseInstrInfo.h.

References llvm::AArch64CC::AL, llvm::MachineInstr::findFirstPredOperandIdx(), llvm::MachineOperand::getImm(), and llvm::MachineInstr::getOperand().

| virtual const ARMBaseRegisterInfo& llvm::ARMBaseInstrInfo::getRegisterInfo | ( | ) | const [pure virtual] |

| bool ARMBaseInstrInfo::getRegSequenceLikeInputs | ( | const MachineInstr & | MI, |

| unsigned | DefIdx, | ||

| SmallVectorImpl< RegSubRegPairAndIdx > & | InputRegs | ||

| ) | const [override, protected] |

Build the equivalent inputs of a REG_SEQUENCE for the given MI and DefIdx. [out] InputRegs of the equivalent REG_SEQUENCE. Each element of the list is modeled as <Reg:SubReg, SubIdx>. E.g., REG_SEQUENCE vreg1:sub1, sub0, vreg2, sub1 would produce two elements:

- vreg1:sub1, sub0

- vreg2<:0>, sub1

- Returns:

- true if it is possible to build such an input sequence with the pair

MI,DefIdx. False otherwise.

- Precondition:

- MI.isRegSequenceLike().

Definition at line 4494 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::getDesc(), llvm::MCInstrDesc::getNumDefs(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineInstr::isRegSequenceLike(), llvm_unreachable, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), and llvm::ARMISD::VMOVDRR.

| const ARMSubtarget& llvm::ARMBaseInstrInfo::getSubtarget | ( | ) | const [inline] |

Definition at line 102 of file ARMBaseInstrInfo.h.

Referenced by expandPostRAPseudo(), llvm::ARMHazardRecognizer::getHazardType(), and isPredicable().

| void ARMBaseInstrInfo::getTrap | ( | MCInst & | MI | ) | const [override] |

Definition at line 4467 of file ARMBaseInstrInfo.cpp.

References llvm::ARMSubtarget::isThumb(), llvm::MCInst::setOpcode(), llvm::ISD::TRAP, and llvm::ARMSubtarget::useNaClTrap().

| void ARMBaseInstrInfo::getUnconditionalBranch | ( | MCInst & | Branch, |

| const MCSymbolRefExpr * | BranchTarget | ||

| ) | const [override] |

Definition at line 4453 of file ARMBaseInstrInfo.cpp.

References llvm::MCInst::addOperand(), llvm::ARMCC::AL, llvm::MCOperand::CreateExpr(), llvm::MCOperand::CreateImm(), llvm::MCOperand::CreateReg(), llvm::ARMSubtarget::isThumb(), llvm::ARMSubtarget::isThumb2(), and llvm::MCInst::setOpcode().

| virtual unsigned llvm::ARMBaseInstrInfo::getUnindexedOpcode | ( | unsigned | Opc | ) | const [pure virtual] |

Implemented in llvm::Thumb2InstrInfo, llvm::ARMInstrInfo, and llvm::Thumb1InstrInfo.

Referenced by convertToThreeAddress().

| bool ARMBaseInstrInfo::hasNOP | ( | ) | const |

Definition at line 4476 of file ARMBaseInstrInfo.cpp.

Referenced by llvm::ARMInstrInfo::getNoopForMachoTarget().

| unsigned ARMBaseInstrInfo::InsertBranch | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock * | TBB, | ||

| MachineBasicBlock * | FBB, | ||

| const SmallVectorImpl< MachineOperand > & | Cond, | ||

| DebugLoc | DL | ||

| ) | const [override] |

Definition at line 396 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::ARMCC::AL, llvm::BuildMI(), llvm::SmallVectorBase::empty(), llvm::MachineFunction::getInfo(), llvm::MachineBasicBlock::getParent(), getReg(), isThumb(), llvm::ARMFunctionInfo::isThumb2Function(), llvm::ARMFunctionInfo::isThumbFunction(), and llvm::SmallVectorTemplateCommon< T >::size().

| bool llvm::ARMBaseInstrInfo::isFpMLxInstruction | ( | unsigned | Opcode | ) | const [inline] |

isFpMLxInstruction - Return true if the specified opcode is a fp MLA / MLS instruction.

Definition at line 358 of file ARMBaseInstrInfo.h.

References llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::count().

Referenced by llvm::ARMHazardRecognizer::getHazardType().

| bool ARMBaseInstrInfo::isFpMLxInstruction | ( | unsigned | Opcode, |

| unsigned & | MulOpc, | ||

| unsigned & | AddSubOpc, | ||

| bool & | NegAcc, | ||

| bool & | HasLane | ||

| ) | const |

isFpMLxInstruction - This version also returns the multiply opcode and the addition / subtraction opcode to expand to. Return true for 'HasLane' for the MLX instructions with an extra lane operand.

Definition at line 4026 of file ARMBaseInstrInfo.cpp.

References ARM_MLxEntry::AddSubOpc, ARM_MLxTable, llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::end(), llvm::DenseMapBase< DerivedT, KeyT, ValueT, KeyInfoT >::find(), ARM_MLxEntry::HasLane, ARM_MLxEntry::MulOpc, and ARM_MLxEntry::NegAcc.

| unsigned ARMBaseInstrInfo::isLoadFromStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

Definition at line 1166 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), and llvm::MachineOperand::isReg().

| unsigned ARMBaseInstrInfo::isLoadFromStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

Definition at line 1214 of file ARMBaseInstrInfo.cpp.

References llvm::NVPTXISD::Dummy, and llvm::MachineInstr::mayLoad().

| bool ARMBaseInstrInfo::isPredicable | ( | MachineInstr * | MI | ) | const [override] |

isPredicable - Return true if the specified instruction can be predicated. By default, this returns true for every instruction with a PredicateOperand.

Definition at line 560 of file ARMBaseInstrInfo.cpp.

References llvm::ARMII::DomainMask, llvm::ARMII::DomainNEON, llvm::MachineInstr::getDesc(), llvm::MachineFunction::getInfo(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), getSubtarget(), isEligibleForITBlock(), llvm::MachineInstr::isPredicable(), llvm::ARMFunctionInfo::isThumb2Function(), llvm::isV8EligibleForIT(), llvm::ARMSubtarget::restrictIT(), and llvm::MCInstrDesc::TSFlags.

| bool ARMBaseInstrInfo::isPredicated | ( | const MachineInstr * | MI | ) | const [override] |

Definition at line 441 of file ARMBaseInstrInfo.cpp.

References llvm::AArch64CC::AL, llvm::MachineInstr::findFirstPredOperandIdx(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), I, llvm::MachineBasicBlock::instr_end(), llvm::MachineInstr::isBundle(), and llvm::AArch64CC::MI.

Referenced by AnalyzeBranch(), getExecutionDomain(), optimizeCompareInstr(), and setExecutionDomain().

| bool llvm::ARMBaseInstrInfo::isProfitableToDupForIfCvt | ( | MachineBasicBlock & | MBB, |

| unsigned | NumCycles, | ||

| const BranchProbability & | Probability | ||

| ) | const [inline, override] |

Definition at line 228 of file ARMBaseInstrInfo.h.

| bool ARMBaseInstrInfo::isProfitableToIfCvt | ( | MachineBasicBlock & | MBB, |

| unsigned | NumCycles, | ||

| unsigned | ExtraPredCycles, | ||

| const BranchProbability & | Probability | ||

| ) | const [override] |

Definition at line 1640 of file ARMBaseInstrInfo.cpp.

References llvm::BranchProbability::getDenominator(), llvm::ARMSubtarget::getMispredictionPenalty(), and llvm::BranchProbability::getNumerator().

| bool ARMBaseInstrInfo::isProfitableToIfCvt | ( | MachineBasicBlock & | TMBB, |

| unsigned | NumT, | ||

| unsigned | ExtraT, | ||

| MachineBasicBlock & | FMBB, | ||

| unsigned | NumF, | ||

| unsigned | ExtraF, | ||

| const BranchProbability & | Probability | ||

| ) | const [override] |

Definition at line 1656 of file ARMBaseInstrInfo.cpp.

References llvm::BranchProbability::getDenominator(), llvm::ARMSubtarget::getMispredictionPenalty(), and llvm::BranchProbability::getNumerator().

| bool ARMBaseInstrInfo::isProfitableToUnpredicate | ( | MachineBasicBlock & | TMBB, |

| MachineBasicBlock & | FMBB | ||

| ) | const [override] |

Definition at line 1680 of file ARMBaseInstrInfo.cpp.

References llvm::ARMSubtarget::isSwift().

| bool ARMBaseInstrInfo::isSchedulingBoundary | ( | const MachineInstr * | MI, |

| const MachineBasicBlock * | MBB, | ||

| const MachineFunction & | MF | ||

| ) | const [override] |

| unsigned ARMBaseInstrInfo::isStoreToStackSlot | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

Definition at line 975 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::MachineOperand::getSubReg(), llvm::MachineOperand::isFI(), llvm::MachineOperand::isImm(), and llvm::MachineOperand::isReg().

| unsigned ARMBaseInstrInfo::isStoreToStackSlotPostFE | ( | const MachineInstr * | MI, |

| int & | FrameIndex | ||

| ) | const [override] |

Definition at line 1023 of file ARMBaseInstrInfo.cpp.

References llvm::NVPTXISD::Dummy, and llvm::MachineInstr::mayStore().

| bool ARMBaseInstrInfo::isSwiftFastImmShift | ( | const MachineInstr * | MI | ) | const |

Returns true if the instruction has a shift by immediate that can be executed in one cycle less.

Definition at line 4480 of file ARMBaseInstrInfo.cpp.

References llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOperand(), llvm::ARM_AM::getSORegOffset(), llvm::ARM_AM::getSORegShOp(), llvm::ARM_AM::lsl, and llvm::ARM_AM::lsr.

| void ARMBaseInstrInfo::loadRegFromStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MBBI, | ||

| unsigned | DestReg, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Reimplemented in llvm::Thumb2InstrInfo, and llvm::Thumb1InstrInfo.

Definition at line 1030 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultPred(), AddDReg(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), Align(), llvm::BuildMI(), llvm::RegState::DefineNoRead, llvm::MachineBasicBlock::end(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), getRegisterInfo(), llvm::TargetRegisterClass::getSize(), llvm::ARMSubtarget::hasV5TEOps(), llvm::RegState::ImplicitDefine, llvm::TargetRegisterInfo::isPhysicalRegister(), llvm_unreachable, and llvm::MachineMemOperand::MOLoad.

| bool ARMBaseInstrInfo::optimizeCompareInstr | ( | MachineInstr * | CmpInstr, |

| unsigned | SrcReg, | ||

| unsigned | SrcReg2, | ||

| int | CmpMask, | ||

| int | CmpValue, | ||

| const MachineRegisterInfo * | MRI | ||

| ) | const [override] |

optimizeCompareInstr - Convert the instruction to set the zero flag so that we can remove a "comparison with zero"; Remove a redundant CMP instruction if the flags can be updated in the same way by an earlier instruction such as SUB.

optimizeCompareInstr - Convert the instruction supplying the argument to the comparison into one that sets the zero bit in the flags register; Remove a redundant Compare instruction if an earlier instruction can set the flags in the same way as Compare. E.g. SUBrr(r1,r2) and CMPrr(r1,r2). We also handle the case where two operands are swapped: SUBrr(r1,r2) and CMPrr(r2,r1), by updating the condition code of instructions which use the flags.

Definition at line 2312 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, llvm::MachineBasicBlock::begin(), llvm::MachineOperand::clobbersPhysReg(), llvm::MachineBasicBlock::end(), EQ, llvm::MachineInstr::eraseFromParent(), llvm::ARMCC::GE, llvm::AArch64CC::GE, llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), getSwappedCondition(), llvm::MachineRegisterInfo::getUniqueVRegDef(), llvm::ARMCC::GT, llvm::AArch64CC::GT, I, llvm::MachineOperand::isDef(), isPredicated(), isRedundantFlagInstr(), llvm::MachineOperand::isReg(), llvm::MachineOperand::isRegMask(), isSuitableForMask(), llvm::ARMCC::LE, llvm::ARMCC::LT, llvm::AArch64CC::MI, llvm::MachineInstr::modifiesRegister(), llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::MachineInstr::readsRegister(), llvm::MachineOperand::setIsDef(), llvm::MachineOperand::setReg(), llvm::SmallVectorTemplateCommon< T >::size(), llvm::MachineBasicBlock::succ_begin(), llvm::MachineBasicBlock::succ_end(), llvm::MachineRegisterInfo::use_instr_begin(), llvm::MachineRegisterInfo::use_instr_end(), llvm::ARMCC::VC, llvm::ARMCC::VS, and llvm::AArch64CC::VS.

| MachineInstr * ARMBaseInstrInfo::optimizeSelect | ( | MachineInstr * | MI, |

| bool | PreferFalse | ||

| ) | const [override] |

Definition at line 1798 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultCC(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addOperand(), llvm::BuildMI(), canFoldIntoMOVCC(), llvm::MachineRegisterInfo::constrainRegClass(), llvm::MachineInstr::eraseFromParent(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), llvm::MachineOperand::getImm(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::ARMCC::getOppositeCondition(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::MachineFunction::getRegInfo(), llvm::MachineInstr::hasOptionalDef(), llvm::AArch64CC::MI, llvm::MachineOperand::setImplicit(), and llvm::MachineInstr::tieOperands().

| bool ARMBaseInstrInfo::PredicateInstruction | ( | MachineInstr * | MI, |

| const SmallVectorImpl< MachineOperand > & | Pred | ||

| ) | const [override] |

Definition at line 458 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstr::findFirstPredOperandIdx(), llvm::getMatchingCondBranchOpcode(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), getReg(), llvm::isUncondBranchOpcode(), llvm::AArch64CC::MI, llvm::MachineInstr::setDesc(), llvm::MachineOperand::setImm(), and llvm::MachineOperand::setReg().

| bool ARMBaseInstrInfo::produceSameValue | ( | const MachineInstr * | MI0, |

| const MachineInstr * | MI1, | ||

| const MachineRegisterInfo * | MRI | ||

| ) | const [override] |

Definition at line 1390 of file ARMBaseInstrInfo.cpp.

References llvm::MachineConstantPoolEntry::ConstVal, llvm::MachineFunction::getConstantPool(), llvm::MachineConstantPool::getConstants(), llvm::MachineOperand::getGlobal(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getNumOperands(), llvm::MachineOperand::getOffset(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getVRegDef(), llvm::ARMConstantPoolValue::hasSameValue(), llvm::MachineInstr::IgnoreVRegDefs, llvm::MachineOperand::isIdenticalTo(), llvm::MachineInstr::isIdenticalTo(), llvm::MachineConstantPoolEntry::isMachineConstantPoolEntry(), llvm::TargetRegisterInfo::isVirtualRegister(), llvm::MachineConstantPoolEntry::MachineCPVal, and llvm::MachineConstantPoolEntry::Val.

| void ARMBaseInstrInfo::reMaterialize | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MI, | ||

| unsigned | DestReg, | ||

| unsigned | SubIdx, | ||

| const MachineInstr * | Orig, | ||

| const TargetRegisterInfo & | TRI | ||

| ) | const [override] |

Definition at line 1347 of file ARMBaseInstrInfo.cpp.

References llvm::MachineInstrBuilder::addConstantPoolIndex(), llvm::MachineInstrBuilder::addImm(), llvm::BuildMI(), llvm::MachineFunction::CloneMachineInstr(), duplicateCPV(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getIndex(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineBasicBlock::insert(), llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), llvm::MachineInstr::setMemRefs(), and llvm::MachineInstr::substituteRegister().

| unsigned ARMBaseInstrInfo::RemoveBranch | ( | MachineBasicBlock & | MBB | ) | const [override] |

Definition at line 367 of file ARMBaseInstrInfo.cpp.

References llvm::MachineBasicBlock::begin(), llvm::MachineBasicBlock::end(), I, llvm::isCondBranchOpcode(), and llvm::isUncondBranchOpcode().

| bool ARMBaseInstrInfo::ReverseBranchCondition | ( | SmallVectorImpl< MachineOperand > & | Cond | ) | const [override] |

Definition at line 435 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::getOppositeCondition().

| void ARMBaseInstrInfo::setExecutionDomain | ( | MachineInstr * | MI, |

| unsigned | Domain | ||

| ) | const [override] |

Definition at line 4151 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultPred(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::RegState::Define, ExeNEON, getCorrespondingDRegAndLane(), llvm::MachineInstr::getDebugLoc(), llvm::MachineInstr::getDesc(), getImplicitSPRUseForDPRUse(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineInstr::getParent(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), getRegisterInfo(), llvm::getUndefRegState(), llvm::RegState::Implicit, isPredicated(), llvm_unreachable, llvm::AArch64CC::MI, llvm::MachineInstr::readsRegister(), llvm::MachineInstr::RemoveOperand(), llvm::MachineInstr::setDesc(), and llvm::RegState::Undef.

| bool ARMBaseInstrInfo::shouldScheduleLoadsNear | ( | SDNode * | Load1, |

| SDNode * | Load2, | ||

| int64_t | Offset1, | ||

| int64_t | Offset2, | ||

| unsigned | NumLoads | ||

| ) | const [override] |

shouldScheduleLoadsNear - This is a used by the pre-regalloc scheduler to determine (in conjunction with areLoadsFromSameBasePtr) if two loads should be scheduled togther. On some targets if two loads are loading from addresses in the same cache line, it's better if they are scheduled together. This function takes two integers that represent the load offsets from the common base address. It returns true if it decides it's desirable to schedule the two loads together. "NumLoads" is the number of loads that have already been scheduled after Load1.

shouldScheduleLoadsNear - This is a used by the pre-regalloc scheduler to determine (in conjunction with areLoadsFromSameBasePtr) if two loads should be scheduled togther. On some targets if two loads are loading from addresses in the same cache line, it's better if they are scheduled together. This function takes two integers that represent the load offsets from the common base address. It returns true if it decides it's desirable to schedule the two loads together. "NumLoads" is the number of loads that have already been scheduled after Load1.

FIXME: remove this in favor of the MachineInstr interface once pre-RA-sched is permanently disabled.

Definition at line 1566 of file ARMBaseInstrInfo.cpp.

References llvm::SDNode::getMachineOpcode(), and llvm::ARMSubtarget::isThumb1Only().

| void ARMBaseInstrInfo::storeRegToStackSlot | ( | MachineBasicBlock & | MBB, |

| MachineBasicBlock::iterator | MBBI, | ||

| unsigned | SrcReg, | ||

| bool | isKill, | ||

| int | FrameIndex, | ||

| const TargetRegisterClass * | RC, | ||

| const TargetRegisterInfo * | TRI | ||

| ) | const [override] |

Reimplemented in llvm::Thumb2InstrInfo, and llvm::Thumb1InstrInfo.

Definition at line 839 of file ARMBaseInstrInfo.cpp.

References llvm::AddDefaultPred(), AddDReg(), llvm::MachineInstrBuilder::addFrameIndex(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMemOperand(), llvm::MachineInstrBuilder::addReg(), Align(), llvm::BuildMI(), llvm::MachineBasicBlock::end(), llvm::MachinePointerInfo::getFixedStack(), llvm::MachineFunction::getFrameInfo(), llvm::getKillRegState(), llvm::MachineFunction::getMachineMemOperand(), llvm::MachineFrameInfo::getObjectAlignment(), llvm::MachineFrameInfo::getObjectSize(), llvm::MachineBasicBlock::getParent(), getRegisterInfo(), llvm::TargetRegisterClass::getSize(), llvm::ARMSubtarget::hasV5TEOps(), llvm_unreachable, and llvm::MachineMemOperand::MOStore.

| bool ARMBaseInstrInfo::SubsumesPredicate | ( | const SmallVectorImpl< MachineOperand > & | Pred1, |

| const SmallVectorImpl< MachineOperand > & | Pred2 | ||

| ) | const [override] |

Definition at line 480 of file ARMBaseInstrInfo.cpp.

References llvm::ARMCC::AL, EQ, llvm::ARMCC::GE, llvm::AArch64CC::GT, llvm::AArch64CC::HI, llvm::ARMCC::HS, llvm::ARMCC::LE, llvm::ARMCC::LO, llvm::ARMCC::LS, llvm::AArch64CC::LT, and llvm::SmallVectorTemplateCommon< T >::size().

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1