#include <ARMISelLowering.h>

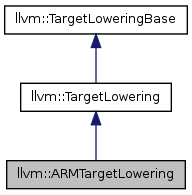

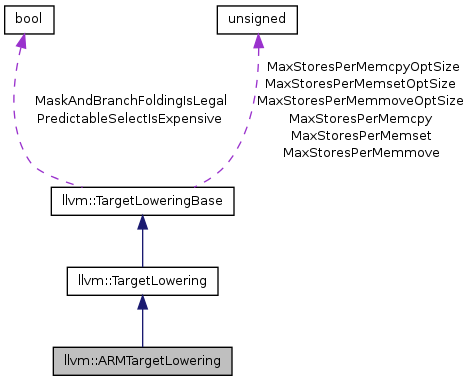

Detailed Description

Definition at line 233 of file ARMISelLowering.h.

Constructor & Destructor Documentation

| ARMTargetLowering::ARMTargetLowering | ( | TargetMachine & | TM | ) | [explicit] |

Definition at line 167 of file ARMISelLowering.cpp.

References llvm::ISD::ADD, llvm::RTLIB::ADD_F32, llvm::RTLIB::ADD_F64, llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::AND, llvm::ISD::ANY_EXTEND, llvm::CallingConv::ARM_AAPCS, llvm::CallingConv::ARM_AAPCS_VFP, llvm::CallingConv::ARM_APCS, llvm::ISD::ATOMIC_CMP_SWAP, llvm::ISD::ATOMIC_FENCE, llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_LOAD_ADD, llvm::ISD::ATOMIC_LOAD_AND, llvm::ISD::ATOMIC_LOAD_MAX, llvm::ISD::ATOMIC_LOAD_MIN, llvm::ISD::ATOMIC_LOAD_NAND, llvm::ISD::ATOMIC_LOAD_OR, llvm::ISD::ATOMIC_LOAD_SUB, llvm::ISD::ATOMIC_LOAD_UMAX, llvm::ISD::ATOMIC_LOAD_UMIN, llvm::ISD::ATOMIC_LOAD_XOR, llvm::ISD::ATOMIC_STORE, llvm::ISD::ATOMIC_SWAP, llvm::ISD::BITCAST, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BRCOND, llvm::ISD::BSWAP, llvm::ISD::BUILD_VECTOR, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::ISD::ConstantFP, llvm::ISD::ConstantPool, llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::TargetLoweringBase::Custom, llvm::RTLIB::DIV_F32, llvm::RTLIB::DIV_F64, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::EH_SJLJ_LONGJMP, llvm::ISD::EH_SJLJ_SETJMP, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::MVT::f16, llvm::MVT::f32, llvm::MVT::f64, llvm::ISD::FABS, llvm::ISD::FADD, llvm::ISD::FCEIL, llvm::ISD::FCOPYSIGN, llvm::ISD::FCOS, llvm::ISD::FDIV, llvm::ISD::FEXP, llvm::ISD::FEXP2, llvm::ISD::FFLOOR, llvm::ISD::FGETSIGN, llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::ISD::FLOG, llvm::ISD::FLOG10, llvm::ISD::FLOG2, llvm::ISD::FLT_ROUNDS_, llvm::ISD::FMA, llvm::ISD::FMUL, llvm::ISD::FNEARBYINT, llvm::ISD::FNEG, llvm::ISD::FP16_TO_FP, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_FP16, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::RTLIB::FPEXT_F16_F32, llvm::RTLIB::FPEXT_F32_F64, llvm::ISD::FPOW, llvm::ISD::FPOWI, llvm::RTLIB::FPROUND_F32_F16, llvm::RTLIB::FPROUND_F64_F16, llvm::RTLIB::FPROUND_F64_F32, llvm::RTLIB::FPTOSINT_F32_I32, llvm::RTLIB::FPTOSINT_F32_I64, llvm::RTLIB::FPTOSINT_F64_I32, llvm::RTLIB::FPTOSINT_F64_I64, llvm::RTLIB::FPTOUINT_F32_I32, llvm::RTLIB::FPTOUINT_F32_I64, llvm::RTLIB::FPTOUINT_F64_I32, llvm::RTLIB::FPTOUINT_F64_I64, llvm::ISD::FREM, llvm::ISD::FRINT, llvm::ISD::FROUND, llvm::ISD::FSIN, llvm::ISD::FSINCOS, llvm::ISD::FSQRT, llvm::ISD::FSUB, llvm::ISD::FTRUNC, llvm::TargetSubtargetInfo::getInstrItineraryData(), llvm::Triple::getOS(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::TargetMachine::getSubtarget(), llvm::TargetMachine::getSubtargetImpl(), llvm::ARMSubtarget::getTargetTriple(), llvm::ISD::GLOBAL_OFFSET_TABLE, llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::ARMSubtarget::hasAnyDataBarrier(), llvm::ARMSubtarget::hasARMOps(), llvm::ARMSubtarget::hasDivide(), llvm::ARMSubtarget::hasDivideInARMMode(), llvm::ARMSubtarget::hasFP16(), llvm::ARMSubtarget::hasNEON(), llvm::ARMSubtarget::hasSinCos(), llvm::ARMSubtarget::hasThumb2DSP(), llvm::ARMSubtarget::hasV5TOps(), llvm::ARMSubtarget::hasV6Ops(), llvm::ARMSubtarget::hasV8Ops(), llvm::ARMSubtarget::hasVFP2(), llvm::ARMSubtarget::hasVFP4(), llvm::Sched::Hybrid, llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::Triple::IOS, llvm::ARMSubtarget::isAAPCS_ABI(), llvm::ARMSubtarget::isFPOnlySP(), llvm::Triple::isiOS(), llvm::ARMSubtarget::isLikeA9(), llvm::Triple::isOSVersionLT(), llvm::ARMSubtarget::isTargetAEABI(), llvm::ARMSubtarget::isTargetDarwin(), llvm::ARMSubtarget::isTargetMachO(), llvm::ARMSubtarget::isTargetWindows(), llvm::ARMSubtarget::isThumb(), llvm::ARMSubtarget::isThumb1Only(), llvm::ARMSubtarget::isThumb2(), llvm::Triple::isWindowsItaniumEnvironment(), llvm::ISD::LAST_INDEXED_MODE, llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::TargetLoweringBase::Legal, llvm::TargetLoweringBase::MaxStoresPerMemcpy, llvm::TargetLoweringBase::MaxStoresPerMemcpyOptSize, llvm::TargetLoweringBase::MaxStoresPerMemmove, llvm::TargetLoweringBase::MaxStoresPerMemmoveOptSize, llvm::TargetLoweringBase::MaxStoresPerMemset, llvm::TargetLoweringBase::MaxStoresPerMemsetOptSize, llvm::RTLIB::MEMCPY, llvm::RTLIB::MEMMOVE, llvm::RTLIB::MEMSET, llvm::ISD::MUL, llvm::RTLIB::MUL_F32, llvm::RTLIB::MUL_F64, llvm::RTLIB::MUL_I64, llvm::ISD::MULHS, llvm::ISD::MULHU, Name, llvm::RTLIB::O_F32, llvm::RTLIB::O_F64, llvm::RTLIB::OEQ_F32, llvm::RTLIB::OEQ_F64, llvm::RTLIB::OGE_F32, llvm::RTLIB::OGE_F64, llvm::RTLIB::OGT_F32, llvm::RTLIB::OGT_F64, llvm::RTLIB::OLE_F32, llvm::RTLIB::OLE_F64, llvm::RTLIB::OLT_F32, llvm::RTLIB::OLT_F64, llvm::TargetMachine::Options, llvm::ISD::OR, llvm::MVT::Other, llvm::ISD::PRE_INC, llvm::TargetLoweringBase::PredictableSelectIsExpensive, llvm::ISD::PREFETCH, llvm::TargetLoweringBase::Promote, llvm::ISD::READCYCLECOUNTER, llvm::Sched::RegPressure, llvm::ISD::ROTL, llvm::ISD::SADDO, llvm::ISD::SDIV, llvm::RTLIB::SDIV_I16, llvm::RTLIB::SDIV_I32, llvm::RTLIB::SDIV_I64, llvm::RTLIB::SDIV_I8, llvm::ISD::SDIVREM, llvm::RTLIB::SDIVREM_I16, llvm::RTLIB::SDIVREM_I32, llvm::RTLIB::SDIVREM_I64, llvm::RTLIB::SDIVREM_I8, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::TargetLoweringBase::setBooleanVectorContents(), llvm::ISD::SETCC, llvm::ISD::SETCC_INVALID, llvm::TargetLoweringBase::setCmpLibcallCC(), llvm::ISD::SETEQ, llvm::TargetLoweringBase::setExceptionPointerRegister(), llvm::TargetLoweringBase::setExceptionSelectorRegister(), llvm::TargetLoweringBase::setIndexedLoadAction(), llvm::TargetLoweringBase::setIndexedStoreAction(), llvm::TargetLoweringBase::setInsertFencesForAtomic(), llvm::TargetLoweringBase::setLibcallCallingConv(), llvm::TargetLoweringBase::setLibcallName(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setMinFunctionAlignment(), llvm::TargetLoweringBase::setMinStackArgumentAlignment(), llvm::ISD::SETNE, llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setSchedulingPreference(), llvm::TargetLoweringBase::setStackPointerRegisterToSaveRestore(), llvm::TargetLoweringBase::setTargetDAGCombine(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SEXTLOAD, llvm::ISD::SHL, llvm::RTLIB::SHL_I128, llvm::RTLIB::SHL_I64, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND, llvm::ISD::SIGN_EXTEND_INREG, llvm::RTLIB::SINCOS_F32, llvm::RTLIB::SINCOS_F64, llvm::ThreadModel::Single, llvm::ISD::SINT_TO_FP, llvm::RTLIB::SINTTOFP_I32_F32, llvm::RTLIB::SINTTOFP_I32_F64, llvm::RTLIB::SINTTOFP_I64_F32, llvm::RTLIB::SINTTOFP_I64_F64, llvm::ISD::SMUL_LOHI, llvm::ISD::SRA, llvm::RTLIB::SRA_I128, llvm::RTLIB::SRA_I64, llvm::ISD::SRA_PARTS, llvm::ISD::SREM, llvm::ISD::SRL, llvm::RTLIB::SRL_I128, llvm::RTLIB::SRL_I64, llvm::ISD::SRL_PARTS, llvm::ISD::SSUBO, llvm::ISD::STACKRESTORE, llvm::ISD::STACKSAVE, llvm::ISD::STORE, llvm::ISD::SUB, llvm::RTLIB::SUB_F32, llvm::RTLIB::SUB_F64, llvm::ISD::SUBC, llvm::ISD::SUBE, llvm::TargetOptions::ThreadModel, llvm::ISD::TRAP, llvm::ISD::UADDO, llvm::ISD::UDIV, llvm::RTLIB::UDIV_I16, llvm::RTLIB::UDIV_I32, llvm::RTLIB::UDIV_I64, llvm::RTLIB::UDIV_I8, llvm::ISD::UDIVREM, llvm::RTLIB::UDIVREM_I16, llvm::RTLIB::UDIVREM_I32, llvm::RTLIB::UDIVREM_I64, llvm::RTLIB::UDIVREM_I8, llvm::ISD::UINT_TO_FP, llvm::RTLIB::UINTTOFP_I32_F32, llvm::RTLIB::UINTTOFP_I32_F64, llvm::RTLIB::UINTTOFP_I64_F32, llvm::RTLIB::UINTTOFP_I64_F64, llvm::ISD::UMUL_LOHI, llvm::RTLIB::UNE_F32, llvm::RTLIB::UNE_F64, llvm::RTLIB::UNWIND_RESUME, llvm::RTLIB::UO_F32, llvm::RTLIB::UO_F64, llvm::ISD::UREM, llvm::TargetOptions::UseSoftFloat, llvm::ISD::USUBO, llvm::MVT::v16i8, llvm::MVT::v1i64, llvm::MVT::v2f32, llvm::MVT::v2f64, llvm::MVT::v2i16, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v2i8, llvm::MVT::v4f32, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v4i8, llvm::MVT::v8i16, llvm::MVT::v8i8, llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VAEND, llvm::ISD::VASTART, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::XOR, llvm::ISD::ZERO_EXTEND, llvm::TargetLoweringBase::ZeroOrNegativeOneBooleanContent, and llvm::ISD::ZEXTLOAD.

Member Function Documentation

| void ARMTargetLowering::AdjustInstrPostInstrSelection | ( | MachineInstr * | MI, |

| SDNode * | Node | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'hasPostISelHook' flag. These instructions must be adjusted after instruction selection by target hooks. e.g. To fill in optional defs for ARM 's' setting instructions.

Reimplemented from llvm::TargetLowering.

Definition at line 7659 of file ARMISelLowering.cpp.

References llvm::MachineInstr::addOperand(), llvm::convertAddSubFlagsOpcode(), llvm::MachineOperand::CreateReg(), definesCPSR(), llvm::MachineInstr::getDesc(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MCInstrDesc::getNumOperands(), llvm::MachineInstr::getNumOperands(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineOperand::getReg(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SDNode::hasAnyUseOfValue(), llvm::MachineInstr::hasOptionalDef(), llvm::MachineInstr::hasPostISelHook(), llvm::MachineOperand::isDead(), llvm::MachineOperand::isDef(), llvm::MCOperandInfo::isOptionalDef(), llvm::MachineOperand::isReg(), llvm::MCInstrDesc::OpInfo, llvm::MachineInstr::RemoveOperand(), llvm::MachineInstr::setDesc(), llvm::MachineOperand::setIsDef(), and llvm::MachineOperand::setReg().

| bool ARMTargetLowering::allowsMisalignedMemoryAccesses | ( | EVT | VT, |

| unsigned | AddrSpace, | ||

| unsigned | Align, | ||

| bool * | Fast | ||

| ) | const [override, virtual] |

allowsMisalignedMemoryAccesses - Returns true if the target allows unaligned memory accesses of the specified type. Returns whether it is "fast" by reference in the second argument.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9868 of file ARMISelLowering.cpp.

References llvm::ARMSubtarget::allowsUnalignedMem(), llvm::MVT::f64, llvm::EVT::getSimpleVT(), llvm::ARMSubtarget::hasNEON(), llvm::ARMSubtarget::hasV7Ops(), llvm::MVT::i16, llvm::MVT::i8, llvm::TargetLoweringBase::isLittleEndian(), llvm::MVT::SimpleTy, and llvm::MVT::v2f64.

Referenced by getOptimalMemOpType().

| bool ARMTargetLowering::allowTruncateForTailCall | ( | Type * | , |

| Type * | |||

| ) | const [override, virtual] |

Return true if a truncation from Ty1 to Ty2 is permitted when deciding whether a call is in tail position. Typically this means that both results would be assigned to the same register or stack slot, but it could mean the target performs adequate checks of its own before proceeding with the tail call.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9966 of file ARMISelLowering.cpp.

References llvm::EVT::getEVT(), llvm::Type::getPrimitiveSizeInBits(), llvm::Type::isIntegerTy(), and llvm::TargetLoweringBase::isTypeLegal().

| void ARMTargetLowering::computeKnownBitsForTargetNode | ( | const SDValue | Op, |

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| const SelectionDAG & | DAG, | ||

| unsigned | Depth | ||

| ) | const [override, virtual] |

Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

computeKnownBitsForTargetNode - Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

Reimplemented from llvm::TargetLowering.

Definition at line 10375 of file ARMISelLowering.cpp.

References llvm::ARMISD::ADDC, llvm::ARMISD::ADDE, llvm::ARMISD::CMOV, llvm::SelectionDAG::computeKnownBits(), llvm::APInt::getBitWidth(), llvm::APInt::getHighBitsSet(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::SDValue::getResNo(), llvm::EVT::getScalarType(), llvm::EVT::getSizeInBits(), llvm::ConstantSDNode::getZExtValue(), llvm::ISD::INTRINSIC_W_CHAIN, llvm::ARMISD::SUBC, and llvm::ARMISD::SUBE.

| FastISel * ARMTargetLowering::createFastISel | ( | FunctionLoweringInfo & | funcInfo, |

| const TargetLibraryInfo * | libInfo | ||

| ) | const [override, virtual] |

createFastISel - This method returns a target specific FastISel object, or null if the target does not support "fast" ISel.

Reimplemented from llvm::TargetLowering.

Definition at line 1167 of file ARMISelLowering.cpp.

| MachineBasicBlock * ARMTargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::TargetLowering.

Definition at line 7405 of file ARMISelLowering.cpp.

References SISrcMods::ABS, llvm::AddDefaultPred(), llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addOperand(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), llvm::ARMCC::AL, llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::ARMCC::EQ, llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::ARM_AM::getAM2Offset(), llvm::ARM_AM::getAM2Op(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::SDNode::getOperand(), llvm::ARMCC::getOppositeCondition(), llvm::MachineFunction::getRegInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::MachineFunction::insert(), llvm::ARMSubtarget::isThumb2(), llvm::RegState::Kill, llvm_unreachable, llvm::ARMCC::MI, llvm::AArch64CC::NE, OtherSucc(), llvm::TargetOpcode::PHI, llvm::MachineBasicBlock::splice(), sub(), std::swap(), llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs(), and llvm::ARMISD::WIN__CHKSTK.

| void ARMTargetLowering::emitLeadingFence | ( | IRBuilder<> & | Builder, |

| AtomicOrdering | Ord, | ||

| bool | IsStore, | ||

| bool | IsLoad | ||

| ) | const [override, virtual] |

Inserts in the IR a target-specific intrinsic specifying a fence. It is called by AtomicExpandPass before expanding an AtomicRMW/AtomicCmpXchg/AtomicStore/AtomicLoad. RMW and CmpXchg set both IsStore and IsLoad to true. Backends with !getInsertFencesForAtomic() should keep a no-op here.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10995 of file ARMISelLowering.cpp.

References llvm::Acquire, llvm::AcquireRelease, llvm::TargetLoweringBase::getInsertFencesForAtomic(), llvm::ARM_MB::ISH, llvm::ARM_MB::ISHST, llvm::ARMSubtarget::isSwift(), llvm_unreachable, makeDMB(), llvm::Monotonic, llvm::NotAtomic, llvm::Release, llvm::SequentiallyConsistent, and llvm::Unordered.

| Value * ARMTargetLowering::emitLoadLinked | ( | IRBuilder<> & | Builder, |

| Value * | Addr, | ||

| AtomicOrdering | Ord | ||

| ) | const [override, virtual] |

Perform a load-linked operation on Addr, returning a "Value *" with the corresponding pointee type. This may entail some non-trivial operations to truncate or reconstruct types that will be illegal in the backend. See ARMISelLowering for an example implementation.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 11074 of file ARMISelLowering.cpp.

References llvm::IRBuilder< preserveNames, T, Inserter >::CreateBitCast(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateCall(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateExtractValue(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateOr(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateShl(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateTruncOrBitCast(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateZExt(), llvm::ConstantInt::get(), llvm::Module::getContext(), llvm::Intrinsic::getDeclaration(), llvm::IRBuilderBase::GetInsertBlock(), llvm::Type::getInt8PtrTy(), llvm::BasicBlock::getParent(), llvm::GlobalValue::getParent(), llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), llvm::tgtok::Int, llvm::isAtLeastAcquire(), llvm::ARMSubtarget::isLittle(), and std::swap().

| Value * ARMTargetLowering::emitStoreConditional | ( | IRBuilder<> & | Builder, |

| Value * | Val, | ||

| Value * | Addr, | ||

| AtomicOrdering | Ord | ||

| ) | const [override, virtual] |

Perform a store-conditional operation to Addr. Return the status of the store. This should be 0 if the store succeeded, non-zero otherwise.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 11110 of file ARMISelLowering.cpp.

References llvm::IRBuilder< preserveNames, T, Inserter >::CreateBitCast(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateCall2(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateCall3(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateLShr(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateTrunc(), llvm::IRBuilder< preserveNames, T, Inserter >::CreateZExtOrBitCast(), llvm::Module::getContext(), llvm::Intrinsic::getDeclaration(), llvm::Function::getFunctionType(), llvm::IRBuilderBase::GetInsertBlock(), llvm::Type::getInt32Ty(), llvm::Type::getInt8PtrTy(), llvm::FunctionType::getParamType(), llvm::BasicBlock::getParent(), llvm::GlobalValue::getParent(), llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), llvm::tgtok::Int, llvm::isAtLeastRelease(), llvm::ARMSubtarget::isLittle(), and std::swap().

| void ARMTargetLowering::emitTrailingFence | ( | IRBuilder<> & | Builder, |

| AtomicOrdering | Ord, | ||

| bool | IsStore, | ||

| bool | IsLoad | ||

| ) | const [override, virtual] |

Inserts in the IR a target-specific intrinsic specifying a fence. It is called by AtomicExpandPass after expanding an AtomicRMW/AtomicCmpXchg/AtomicStore/AtomicLoad. RMW and CmpXchg set both IsStore and IsLoad to true. Backends with !getInsertFencesForAtomic() should keep a no-op here.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 11023 of file ARMISelLowering.cpp.

References llvm::Acquire, llvm::AcquireRelease, llvm::TargetLoweringBase::getInsertFencesForAtomic(), llvm::ARM_MB::ISH, llvm_unreachable, makeDMB(), llvm::Monotonic, llvm::NotAtomic, llvm::Release, llvm::SequentiallyConsistent, and llvm::Unordered.

| bool ARMTargetLowering::ExpandInlineAsm | ( | CallInst * | ) | const [override, virtual] |

This hook allows the target to expand an inline asm call to be explicit llvm code if it wants to. This is useful for turning simple inline asms into LLVM intrinsics, which gives the compiler more information about the behavior of the code.

Reimplemented from llvm::TargetLowering.

Definition at line 10425 of file ARMISelLowering.cpp.

References llvm::SmallVectorImpl< T >::clear(), llvm::dyn_cast(), llvm::InlineAsm::getAsmString(), llvm::IntegerType::getBitWidth(), llvm::CallInst::getCalledValue(), llvm::InlineAsm::getConstraintString(), llvm::Value::getType(), llvm::ARMSubtarget::hasV6Ops(), llvm::IntrinsicLowering::LowerToByteSwap(), llvm::SmallVectorTemplateCommon< T >::size(), and llvm::SplitString().

| std::pair< const TargetRegisterClass *, uint8_t > ARMTargetLowering::findRepresentativeClass | ( | MVT | VT | ) | const [override, protected, virtual] |

Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

findRepresentativeClass - Return the largest legal super-reg register class of the register class for the specified type and its associated "cost".

Reimplemented from llvm::TargetLoweringBase.

Definition at line 970 of file ARMISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, llvm::MSP430ISD::RRC, llvm::MVT::SimpleTy, llvm::ARMSubtarget::useNEONForSinglePrecisionFP(), llvm::MVT::v16i8, llvm::MVT::v1i64, llvm::MVT::v2f32, llvm::MVT::v2f64, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v4f32, llvm::MVT::v4i16, llvm::MVT::v4i32, llvm::MVT::v4i64, llvm::MVT::v8i16, llvm::MVT::v8i64, and llvm::MVT::v8i8.

| bool ARMTargetLowering::functionArgumentNeedsConsecutiveRegisters | ( | Type * | Ty, |

| CallingConv::ID | CallConv, | ||

| bool | isVarArg | ||

| ) | const [override, virtual] |

Returns true if an argument of type Ty needs to be passed in a contiguous block of registers in calling convention CallConv.

Return true if a type is an AAPCS-VFP homogeneous aggregate.

Reimplemented from llvm::TargetLowering.

Definition at line 11203 of file ARMISelLowering.cpp.

References llvm::CallingConv::ARM_AAPCS_VFP, llvm::dbgs(), DEBUG, llvm::Type::dump(), HA_UNKNOWN, and isHomogeneousAggregate().

| ARMTargetLowering::ConstraintType ARMTargetLowering::getConstraintType | ( | const std::string & | Constraint | ) | const [override, virtual] |

getConstraintType - Given a constraint letter, return the type of constraint it is for this target.

Reimplemented from llvm::TargetLowering.

Definition at line 10459 of file ARMISelLowering.cpp.

References llvm::TargetLowering::C_Memory, llvm::TargetLowering::C_Other, and llvm::TargetLowering::C_RegisterClass.

| unsigned ARMTargetLowering::getJumpTableEncoding | ( | ) | const [override, virtual] |

Return the entry encoding for a jump table in the current function. The returned value is a member of the MachineJumpTableInfo::JTEntryKind enum.

getJumpTableEncoding - Return the entry encoding for a jump table in the current function. The returned value is a member of the MachineJumpTableInfo::JTEntryKind enum.

Reimplemented from llvm::TargetLowering.

Definition at line 2379 of file ARMISelLowering.cpp.

References llvm::MachineJumpTableInfo::EK_Inline.

| unsigned ARMTargetLowering::getMaximalGlobalOffset | ( | ) | const [override, virtual] |

getMaximalGlobalOffset - Returns the maximal possible offset which can be used for loads / stores from the global.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1174 of file ARMISelLowering.cpp.

References llvm::ARMSubtarget::isThumb1Only().

| EVT ARMTargetLowering::getOptimalMemOpType | ( | uint64_t | , |

| unsigned | , | ||

| unsigned | , | ||

| bool | , | ||

| bool | , | ||

| bool | , | ||

| MachineFunction & | |||

| ) | const [override, virtual] |

Returns the target specific optimal type for load and store operations as a result of memset, memcpy, and memmove lowering.

If DstAlign is zero that means it's safe to destination alignment can satisfy any constraint. Similarly if SrcAlign is zero it means there isn't a need to check it against alignment requirement, probably because the source does not need to be loaded. If 'IsMemset' is true, that means it's expanding a memset. If 'ZeroMemset' is true, that means it's a memset of zero. 'MemcpyStrSrc' indicates whether the memcpy source is constant so it does not need to be loaded. It returns EVT::Other if the type should be determined using generic target-independent logic.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9910 of file ARMISelLowering.cpp.

References allowsMisalignedMemoryAccesses(), llvm::MVT::f64, llvm::CallingConv::Fast, llvm::AttributeSet::FunctionIndex, llvm::Function::getAttributes(), llvm::MachineFunction::getFunction(), llvm::AttributeSet::hasAttribute(), llvm::ARMSubtarget::hasNEON(), llvm::MVT::i16, memOpAlign(), llvm::Attribute::NoImplicitFloat, llvm::MVT::Other, and llvm::MVT::v2f64.

| bool ARMTargetLowering::getPostIndexedAddressParts | ( | SDNode * | N, |

| SDNode * | Op, | ||

| SDValue & | Base, | ||

| SDValue & | Offset, | ||

| ISD::MemIndexedMode & | AM, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

getPostIndexedAddressParts - returns true by value, base pointer and offset pointer and addressing mode by reference if this node can be combined with a load / store to form a post-indexed load / store.

Reimplemented from llvm::TargetLowering.

Definition at line 10327 of file ARMISelLowering.cpp.

References llvm::ISD::ADD, getARMIndexedAddressParts(), llvm::SDNode::getOpcode(), getT2IndexedAddressParts(), llvm::ISD::isSEXTLoad(), llvm::ARMSubtarget::isThumb1Only(), llvm::ARMSubtarget::isThumb2(), llvm::AArch64DB::LD, llvm::ISD::POST_DEC, llvm::ISD::POST_INC, llvm::ISD::SEXTLOAD, and std::swap().

| bool ARMTargetLowering::getPreIndexedAddressParts | ( | SDNode * | N, |

| SDValue & | Base, | ||

| SDValue & | Offset, | ||

| ISD::MemIndexedMode & | AM, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

getPreIndexedAddressParts - returns true by value, base pointer and offset pointer and addressing mode by reference if the node's address can be legally represented as pre-indexed load / store address.

Reimplemented from llvm::TargetLowering.

Definition at line 10289 of file ARMISelLowering.cpp.

References getARMIndexedAddressParts(), llvm::SDValue::getNode(), getT2IndexedAddressParts(), llvm::ISD::isSEXTLoad(), llvm::ARMSubtarget::isThumb1Only(), llvm::ARMSubtarget::isThumb2(), llvm::AArch64DB::LD, llvm::ISD::PRE_DEC, llvm::ISD::PRE_INC, and llvm::ISD::SEXTLOAD.

| const TargetRegisterClass * ARMTargetLowering::getRegClassFor | ( | MVT | VT | ) | const [override, virtual] |

getRegClassFor - Return the register class that should be used for the specified value type.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1152 of file ARMISelLowering.cpp.

References llvm::ARMSubtarget::hasNEON(), llvm::MVT::v4i64, and llvm::MVT::v8i64.

| RCPair ARMTargetLowering::getRegForInlineAsmConstraint | ( | const std::string & | Constraint, |

| MVT | VT | ||

| ) | const [override, virtual] |

Given a physical register constraint (e.g. {edx}), return the register number and the register class for the register.

Given a register class constraint, like 'r', if this corresponds directly to an LLVM register class, return a register of 0 and the register class pointer.

This should only be used for C_Register constraints. On error, this returns a register number of 0 and a null register class pointer..

Reimplemented from llvm::TargetLowering.

Definition at line 10519 of file ARMISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::getSizeInBits(), llvm::ARMSubtarget::isThumb(), and llvm::MVT::Other.

| Sched::Preference ARMTargetLowering::getSchedulingPreference | ( | SDNode * | ) | const [override, virtual] |

Some scheduler, e.g. hybrid, can switch to different scheduling heuristics for different nodes. This function returns the preference (or none) for the given node.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1178 of file ARMISelLowering.cpp.

References llvm::MCInstrInfo::get(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::SDNode::getMachineOpcode(), llvm::MCInstrDesc::getNumDefs(), llvm::SDNode::getNumValues(), llvm::InstrItineraryData::getOperandCycle(), llvm::MCInstrDesc::getSchedClass(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SDNode::getValueType(), llvm::MVT::Glue, llvm::Sched::ILP, llvm::InstrItineraryData::isEmpty(), llvm::EVT::isFloatingPoint(), llvm::SDNode::isMachineOpcode(), llvm::EVT::isVector(), llvm::MVT::Other, llvm::Sched::RegPressure, and TII.

| EVT ARMTargetLowering::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [override, virtual] |

getSetCCResultType - Return the value type to use for ISD::SETCC.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 1145 of file ARMISelLowering.cpp.

References llvm::EVT::changeVectorElementTypeToInteger(), llvm::TargetLoweringBase::getPointerTy(), and llvm::EVT::isVector().

| TargetLowering::ConstraintWeight ARMTargetLowering::getSingleConstraintMatchWeight | ( | AsmOperandInfo & | info, |

| const char * | constraint | ||

| ) | const [override, virtual] |

Examine constraint string and operand type and determine a weight value. The operand object must already have been set up with the operand type.

Examine constraint type and operand type and determine a weight value. This object must already have been set up with the operand type and the current alternative constraint selected.

Reimplemented from llvm::TargetLowering.

Definition at line 10487 of file ARMISelLowering.cpp.

References llvm::TargetLowering::AsmOperandInfo::CallOperandVal, llvm::TargetLowering::CW_Default, llvm::TargetLowering::CW_Invalid, llvm::TargetLowering::CW_Register, llvm::TargetLowering::CW_SpecificReg, llvm::Value::getType(), llvm::Type::isFloatingPointTy(), llvm::Type::isIntegerTy(), and llvm::ARMSubtarget::isThumb().

| const ARMSubtarget* llvm::ARMTargetLowering::getSubtarget | ( | ) | const [inline] |

Definition at line 347 of file ARMISelLowering.h.

| const char * ARMTargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

Definition at line 1006 of file ARMISelLowering.cpp.

References llvm::ARMISD::ADDC, llvm::ARMISD::ADDE, llvm::ARMISD::BCC_i64, llvm::ARMISD::BFI, llvm::ARMISD::BR2_JT, llvm::ARMISD::BR_JT, llvm::ARMISD::BRCOND, llvm::ARMISD::BUILD_VECTOR, llvm::ARMISD::CALL, llvm::ARMISD::CALL_NOLINK, llvm::ARMISD::CALL_PRED, llvm::ARMISD::CMN, llvm::ARMISD::CMOV, llvm::ARMISD::CMP, llvm::ARMISD::CMPFP, llvm::ARMISD::CMPFPw0, llvm::ARMISD::CMPZ, llvm::ARMISD::DYN_ALLOC, llvm::ARMISD::EH_SJLJ_LONGJMP, llvm::ARMISD::EH_SJLJ_SETJMP, llvm::ARMISD::FMAX, llvm::ARMISD::FMIN, llvm::ARMISD::FMSTAT, llvm::ARMISD::FTOSI, llvm::ARMISD::FTOUI, llvm::ARMISD::INTRET_FLAG, llvm::ARMISD::MEMBARRIER_MCR, llvm::ARMISD::PIC_ADD, llvm::ARMISD::PRELOAD, llvm::ARMISD::RBIT, llvm::ARMISD::RET_FLAG, llvm::ARMISD::RRX, llvm::ARMISD::SITOF, llvm::ARMISD::SMLAL, llvm::ARMISD::SRA_FLAG, llvm::ARMISD::SRL_FLAG, llvm::ARMISD::SUBC, llvm::ARMISD::SUBE, llvm::ARMISD::TC_RETURN, llvm::ARMISD::tCALL, llvm::ARMISD::THREAD_POINTER, llvm::ARMISD::UITOF, llvm::ARMISD::UMLAL, llvm::ARMISD::VBICIMM, llvm::ARMISD::VBSL, llvm::ARMISD::VCEQ, llvm::ARMISD::VCEQZ, llvm::ARMISD::VCGE, llvm::ARMISD::VCGEU, llvm::ARMISD::VCGEZ, llvm::ARMISD::VCGT, llvm::ARMISD::VCGTU, llvm::ARMISD::VCGTZ, llvm::ARMISD::VCLEZ, llvm::ARMISD::VCLTZ, llvm::ARMISD::VDUP, llvm::ARMISD::VDUPLANE, llvm::ARMISD::VEXT, llvm::ARMISD::VGETLANEs, llvm::ARMISD::VGETLANEu, llvm::ARMISD::VLD1_UPD, llvm::ARMISD::VLD2_UPD, llvm::ARMISD::VLD2DUP, llvm::ARMISD::VLD2DUP_UPD, llvm::ARMISD::VLD2LN_UPD, llvm::ARMISD::VLD3_UPD, llvm::ARMISD::VLD3DUP, llvm::ARMISD::VLD3DUP_UPD, llvm::ARMISD::VLD3LN_UPD, llvm::ARMISD::VLD4_UPD, llvm::ARMISD::VLD4DUP, llvm::ARMISD::VLD4DUP_UPD, llvm::ARMISD::VLD4LN_UPD, llvm::ARMISD::VMAXNM, llvm::ARMISD::VMINNM, llvm::ARMISD::VMOVDRR, llvm::ARMISD::VMOVFPIMM, llvm::ARMISD::VMOVIMM, llvm::ARMISD::VMOVRRD, llvm::ARMISD::VMULLs, llvm::ARMISD::VMULLu, llvm::ARMISD::VMVNIMM, llvm::ARMISD::VORRIMM, llvm::ARMISD::VQRSHRNs, llvm::ARMISD::VQRSHRNsu, llvm::ARMISD::VQRSHRNu, llvm::ARMISD::VQSHLs, llvm::ARMISD::VQSHLsu, llvm::ARMISD::VQSHLu, llvm::ARMISD::VQSHRNs, llvm::ARMISD::VQSHRNsu, llvm::ARMISD::VQSHRNu, llvm::ARMISD::VREV16, llvm::ARMISD::VREV32, llvm::ARMISD::VREV64, llvm::ARMISD::VRSHRN, llvm::ARMISD::VRSHRs, llvm::ARMISD::VRSHRu, llvm::ARMISD::VSHL, llvm::ARMISD::VSHRs, llvm::ARMISD::VSHRu, llvm::ARMISD::VST1_UPD, llvm::ARMISD::VST2_UPD, llvm::ARMISD::VST2LN_UPD, llvm::ARMISD::VST3_UPD, llvm::ARMISD::VST3LN_UPD, llvm::ARMISD::VST4_UPD, llvm::ARMISD::VST4LN_UPD, llvm::ARMISD::VTBL1, llvm::ARMISD::VTBL2, llvm::ARMISD::VTRN, llvm::ARMISD::VTST, llvm::ARMISD::VUZP, llvm::ARMISD::VZIP, llvm::ARMISD::WIN__CHKSTK, llvm::ARMISD::Wrapper, llvm::ARMISD::WrapperJT, and llvm::ARMISD::WrapperPIC.

| bool ARMTargetLowering::getTgtMemIntrinsic | ( | IntrinsicInfo & | Info, |

| const CallInst & | I, | ||

| unsigned | Intrinsic | ||

| ) | const [override, virtual] |

getTgtMemIntrinsic - Represent NEON load and store intrinsics as MemIntrinsicNodes. The associated MachineMemOperands record the alignment specified in the intrinsic calls.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10866 of file ARMISelLowering.cpp.

References llvm::TargetLoweringBase::IntrinsicInfo::align, llvm::DataLayout::getABITypeAlignment(), llvm::CallInst::getArgOperand(), llvm::Type::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::SequentialType::getElementType(), llvm::CallInst::getNumArgOperands(), llvm::Value::getType(), llvm::DataLayout::getTypeAllocSize(), llvm::EVT::getVectorVT(), llvm::MVT::getVT(), llvm::MVT::i64, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::Type::isVectorTy(), llvm::TargetLoweringBase::IntrinsicInfo::memVT, llvm::TargetLoweringBase::IntrinsicInfo::offset, llvm::TargetLoweringBase::IntrinsicInfo::opc, llvm::TargetLoweringBase::IntrinsicInfo::ptrVal, llvm::TargetLoweringBase::IntrinsicInfo::readMem, llvm::TargetLoweringBase::IntrinsicInfo::vol, and llvm::TargetLoweringBase::IntrinsicInfo::writeMem.

| bool ARMTargetLowering::hasLoadLinkedStoreConditional | ( | ) | const [override, virtual] |

True if AtomicExpandPass should use emitLoadLinked/emitStoreConditional and expand AtomicCmpXchgInst.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10985 of file ARMISelLowering.cpp.

| bool ARMTargetLowering::isDesirableToTransformToIntegerOp | ( | unsigned | , |

| EVT | |||

| ) | const [override, virtual] |

Return true if it is profitable for dag combiner to transform a floating point op of specified opcode to a equivalent op of an integer type. e.g. f32 load -> i32 load can be profitable on ARM.

Reimplemented from llvm::TargetLowering.

Definition at line 9863 of file ARMISelLowering.cpp.

References llvm::MVT::f32, llvm::ISD::LOAD, and llvm::ISD::STORE.

| bool ARMTargetLowering::isFPImmLegal | ( | const APFloat & | Imm, |

| EVT | VT | ||

| ) | const [override, virtual] |

isFPImmLegal - Returns true if the target can instruction select the specified FP immediate natively. If false, the legalizer will materialize the FP immediate as a load from a constant pool.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10853 of file ARMISelLowering.cpp.

References llvm::MVT::f32, llvm::MVT::f64, llvm::AArch64_AM::getFP32Imm(), llvm::ARMSubtarget::hasVFP3(), and llvm::ARMSubtarget::isFPOnlySP().

| bool ARMTargetLowering::isLegalAddImmediate | ( | int64_t | Imm | ) | const [override, virtual] |

isLegalAddImmediate - Return true if the specified immediate is legal add immediate, that is the target has add instructions which can add a register and the immediate without having to materialize the immediate into a register.

isLegalAddImmediate - Return true if the specified immediate is a legal add or sub* immediate, that is the target has add or sub instructions which can add a register with the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10190 of file ARMISelLowering.cpp.

References llvm::abs64(), llvm::ARM_AM::getSOImmVal(), llvm::ARM_AM::getT2SOImmVal(), llvm::ARMSubtarget::isThumb(), and llvm::ARMSubtarget::isThumb2().

| bool ARMTargetLowering::isLegalAddressingMode | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10113 of file ARMISelLowering.cpp.

References llvm::TargetLoweringBase::AddrMode::BaseGV, llvm::TargetLoweringBase::AddrMode::BaseOffs, llvm::EVT::getSimpleVT(), llvm::TargetLoweringBase::getValueType(), llvm::TargetLoweringBase::AddrMode::HasBaseReg, llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i64, llvm::MVT::i8, isLegalAddressImmediate(), isLegalT2ScaledAddressingMode(), llvm::isPowerOf2_32(), llvm::EVT::isSimple(), llvm::ARMSubtarget::isThumb1Only(), llvm::ARMSubtarget::isThumb2(), llvm::MVT::isVoid, llvm::TargetLoweringBase::AddrMode::Scale, and llvm::MVT::SimpleTy.

| bool ARMTargetLowering::isLegalICmpImmediate | ( | int64_t | Imm | ) | const [override, virtual] |

isLegalICmpImmediate - Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10176 of file ARMISelLowering.cpp.

References llvm::abs64(), llvm::ARM_AM::getSOImmVal(), llvm::ARM_AM::getT2SOImmVal(), llvm::ARMSubtarget::isThumb(), and llvm::ARMSubtarget::isThumb2().

| bool ARMTargetLowering::isLegalT2ScaledAddressingMode | ( | const AddrMode & | AM, |

| EVT | VT | ||

| ) | const |

Definition at line 10078 of file ARMISelLowering.cpp.

References llvm::EVT::getSimpleVT(), llvm::TargetLoweringBase::AddrMode::HasBaseReg, llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i64, llvm::MVT::i8, llvm::isPowerOf2_32(), llvm::MVT::isVoid, llvm::TargetLoweringBase::AddrMode::Scale, and llvm::MVT::SimpleTy.

Referenced by isLegalAddressingMode().

| bool llvm::ARMTargetLowering::isNoopAddrSpaceCast | ( | unsigned | SrcAS, |

| unsigned | DestAS | ||

| ) | const [inline, override, virtual] |

Returns true if a cast between SrcAS and DestAS is a noop.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 360 of file ARMISelLowering.h.

| bool ARMTargetLowering::isOffsetFoldingLegal | ( | const GlobalAddressSDNode * | GA | ) | const [override, virtual] |

Return true if folding a constant offset with the given GlobalAddress is legal. It is frequently not legal in PIC relocation models.

Reimplemented from llvm::TargetLowering.

Definition at line 10832 of file ARMISelLowering.cpp.

| bool llvm::ARMTargetLowering::isSelectSupported | ( | SelectSupportKind | Kind | ) | const [inline, override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 249 of file ARMISelLowering.h.

References llvm::TargetLoweringBase::ScalarCondVectorVal.

| bool ARMTargetLowering::isShuffleMaskLegal | ( | const SmallVectorImpl< int > & | M, |

| EVT | VT | ||

| ) | const [override, virtual] |

isShuffleMaskLegal - Targets can use this to indicate that they only support *some* VECTOR_SHUFFLE operations, those with specific masks. By default, if a target supports the VECTOR_SHUFFLE node, all mask values are assumed to be legal.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 5429 of file ARMISelLowering.cpp.

References llvm::EVT::getSizeInBits(), llvm::EVT::getVectorElementType(), llvm::EVT::getVectorNumElements(), llvm::EVT::is128BitVector(), llvm::EVT::is64BitVector(), isReverseMask(), llvm::ShuffleVectorSDNode::isSplatMask(), isVEXTMask(), isVREVMask(), isVTBLMask(), isVTRN_v_undef_Mask(), isVTRNMask(), isVUZP_v_undef_Mask(), isVUZPMask(), isVZIP_v_undef_Mask(), isVZIPMask(), PerfectShuffleTable, llvm::MVT::v16i8, and llvm::MVT::v8i16.

| bool ARMTargetLowering::isZExtFree | ( | SDValue | Val, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Return true if zero-extending the specific node Val to type VT2 is free (either because it's implicitly zero-extended such as ARM ldrb / ldrh or because it's folded such as X86 zero-extending loads).

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9945 of file ARMISelLowering.cpp.

References llvm::SDValue::getOpcode(), llvm::EVT::getSimpleVT(), llvm::SDValue::getValueType(), llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i8, llvm::EVT::isInteger(), llvm::EVT::isSimple(), llvm::ISD::LOAD, and llvm::MVT::SimpleTy.

| void ARMTargetLowering::LowerAsmOperandForConstraint | ( | SDValue | Op, |

| std::string & | Constraint, | ||

| std::vector< SDValue > & | Ops, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerAsmOperandForConstraint - Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops. If hasMemory is true it means one of the asm constraint of the inline asm instruction being processed is 'm'.

LowerAsmOperandForConstraint - Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops.

Reimplemented from llvm::TargetLowering.

Definition at line 10568 of file ARMISelLowering.cpp.

References llvm::dyn_cast(), llvm::SDValue::getNode(), llvm::ConstantSDNode::getSExtValue(), llvm::ARM_AM::getSOImmVal(), llvm::ARM_AM::getT2SOImmVal(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValueType(), llvm::ARMSubtarget::hasV6T2Ops(), llvm::ARMSubtarget::isThumb(), llvm::ARMSubtarget::isThumb1Only(), llvm::ARMSubtarget::isThumb2(), and llvm::ARM_AM::isThumbImmShiftedVal().

| SDValue ARMTargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

This callback is invoked for operations that are unsupported by the target, which are registered to use 'custom' lowering, and whose defined values are all legal. If the target has no operations that require custom lowering, it need not implement this. The default implementation of this aborts.

Reimplemented from llvm::TargetLowering.

Definition at line 6364 of file ARMISelLowering.cpp.

References llvm::ISD::ADDC, llvm::ISD::ADDE, llvm::ISD::ATOMIC_FENCE, llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_STORE, llvm::ISD::BITCAST, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BUILD_VECTOR, llvm::Triple::COFF, llvm::ISD::CONCAT_VECTORS, llvm::ISD::ConstantFP, llvm::ISD::ConstantPool, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::EH_SJLJ_LONGJMP, llvm::ISD::EH_SJLJ_SETJMP, llvm::Triple::ELF, ExpandBITCAST(), llvm::ISD::EXTRACT_VECTOR_ELT, llvm::ISD::FCOPYSIGN, llvm::ISD::FLT_ROUNDS_, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FRAMEADDR, llvm::ISD::FSINCOS, llvm::SDValue::getNode(), llvm::Triple::getObjectFormat(), llvm::SDValue::getOpcode(), llvm::ARMSubtarget::getTargetTriple(), llvm::ISD::GLOBAL_OFFSET_TABLE, llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::Triple::isWindowsItaniumEnvironment(), llvm_unreachable, LowerADDC_ADDE_SUBC_SUBE(), LowerATOMIC_FENCE(), LowerAtomicLoadStore(), LowerCONCAT_VECTORS(), LowerConstantPool(), LowerCTPOP(), LowerCTTZ(), LowerEXTRACT_VECTOR_ELT(), LowerINSERT_VECTOR_ELT(), LowerMUL(), LowerPREFETCH(), LowerSDIV(), LowerShift(), LowerUDIV(), LowerVASTART(), LowerVECTOR_SHUFFLE(), LowerVSETCC(), llvm::Triple::MachO, llvm::ISD::MUL, llvm::ISD::PREFETCH, llvm::ISD::RETURNADDR, llvm::ISD::SADDO, llvm::ISD::SDIV, llvm::ISD::SDIVREM, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::ISD::SETCC, llvm::ISD::SHL, llvm::ISD::SHL_PARTS, llvm::ISD::SINT_TO_FP, llvm::ISD::SRA, llvm::ISD::SRA_PARTS, llvm::ISD::SRL, llvm::ISD::SRL_PARTS, llvm::ISD::SSUBO, llvm::ISD::SUBC, llvm::ISD::SUBE, llvm::ISD::UADDO, llvm::ISD::UDIV, llvm::ISD::UDIVREM, llvm::ISD::UINT_TO_FP, llvm::ISD::USUBO, llvm::ISD::VASTART, and llvm::ISD::VECTOR_SHUFFLE.

| SDValue ARMTargetLowering::PerformCMOVCombine | ( | SDNode * | N, |

| SelectionDAG & | DAG | ||

| ) | const |

PerformCMOVCombine - Target-specific DAG combining for ARMISD::CMOV.

FIXME: Turn this into a target neutral optimization?

Definition at line 9739 of file ARMISelLowering.cpp.

References llvm::ISD::AssertZext, llvm::ARMISD::CMOV, llvm::ARMISD::CMPZ, llvm::SelectionDAG::computeKnownBits(), llvm::ARMCC::EQ, llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::SelectionDAG::getValueType(), llvm::SDNode::getValueType(), llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i8, llvm::ARMCC::NE, and llvm::ISD::SETNE.

Referenced by PerformDAGCombine().

| SDValue ARMTargetLowering::PerformDAGCombine | ( | SDNode * | N, |

| DAGCombinerInfo & | DCI | ||

| ) | const [override, virtual] |

This method will be invoked for all target nodes and for any target-independent nodes that the target has registered with invoke it for.

The semantics are as follows: Return Value: SDValue.Val == 0 - No change was made SDValue.Val == N - N was replaced, is dead, and is already handled. otherwise - N should be replaced by the returned Operand.

In addition, methods provided by DAGCombinerInfo may be used to perform more complex transformations.

Reimplemented from llvm::TargetLowering.

Definition at line 9801 of file ARMISelLowering.cpp.

References llvm::ISD::ADD, llvm::ISD::ADDC, llvm::ISD::AND, llvm::ISD::ANY_EXTEND, llvm::ARMISD::BFI, llvm::ARMISD::BUILD_VECTOR, llvm::ISD::BUILD_VECTOR, llvm::ARMISD::CMOV, CombineBaseUpdate(), llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::ISD::FDIV, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::ISD::MUL, llvm::ISD::OR, PerformADDCCombine(), PerformADDCombine(), PerformANDCombine(), PerformARMBUILD_VECTORCombine(), PerformBFICombine(), PerformBUILD_VECTORCombine(), PerformCMOVCombine(), PerformExtendCombine(), PerformInsertEltCombine(), PerformIntrinsicCombine(), PerformMULCombine(), PerformORCombine(), PerformSELECT_CCCombine(), PerformShiftCombine(), PerformSTORECombine(), PerformSUBCombine(), PerformVCVTCombine(), PerformVDIVCombine(), PerformVDUPLANECombine(), PerformVECTOR_SHUFFLECombine(), PerformVMOVDRRCombine(), PerformVMOVRRDCombine(), PerformXORCombine(), llvm::ISD::SELECT_CC, llvm::ISD::SHL, llvm::ISD::SIGN_EXTEND, llvm::ISD::SRA, llvm::ISD::SRL, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ARMISD::VDUPLANE, llvm::ISD::VECTOR_SHUFFLE, llvm::ARMISD::VLD2DUP, llvm::ARMISD::VLD3DUP, llvm::ARMISD::VLD4DUP, llvm::ARMISD::VMOVDRR, llvm::ARMISD::VMOVRRD, llvm::ISD::XOR, and llvm::ISD::ZERO_EXTEND.

| void ARMTargetLowering::ReplaceNodeResults | ( | SDNode * | N, |

| SmallVectorImpl< SDValue > & | Results, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

ReplaceNodeResults - Replace the results of node with an illegal result type with new values built out of custom code.

Reimplemented from llvm::TargetLowering.

Definition at line 6444 of file ARMISelLowering.cpp.

References llvm::ISD::BITCAST, Expand64BitShift(), ExpandBITCAST(), llvm::SDValue::getNode(), llvm::SDNode::getOpcode(), llvm_unreachable, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), llvm::ISD::READCYCLECOUNTER, ReplaceREADCYCLECOUNTER(), llvm::ISD::SRA, and llvm::ISD::SRL.

| bool ARMTargetLowering::shouldConvertConstantLoadToIntImm | ( | const APInt & | Imm, |

| Type * | Ty | ||

| ) | const [override, virtual] |

Returns true if it is beneficial to convert a load of a constant to just the constant itself.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 10975 of file ARMISelLowering.cpp.

References llvm::tgtok::Bits, llvm::Type::getPrimitiveSizeInBits(), and llvm::Type::isIntegerTy().

| bool ARMTargetLowering::shouldExpandAtomicLoadInIR | ( | LoadInst * | LI | ) | const [override, virtual] |

Returns true if the given (atomic) load should be expanded by the IR-level AtomicExpand pass into a load-linked instruction (through emitLoadLinked()).

Reimplemented from llvm::TargetLoweringBase.

Definition at line 11057 of file ARMISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), and llvm::ARMSubtarget::isMClass().

| bool ARMTargetLowering::shouldExpandAtomicRMWInIR | ( | AtomicRMWInst * | RMWI | ) | const [override, virtual] |

Returns true if the given AtomicRMW should be expanded by the IR-level AtomicExpand pass into a loop using LoadLinked/StoreConditional.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 11064 of file ARMISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), and llvm::ARMSubtarget::isMClass().

| bool ARMTargetLowering::shouldExpandAtomicStoreInIR | ( | StoreInst * | SI | ) | const [override, virtual] |

Returns true if the given (atomic) store should be expanded by the IR-level AtomicExpand pass into an "atomic xchg" which ignores its input.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 11048 of file ARMISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), llvm::Value::getType(), llvm::StoreInst::getValueOperand(), and llvm::ARMSubtarget::isMClass().

| bool ARMTargetLowering::useLoadStackGuardNode | ( | ) | const [override, virtual] |

If this function returns true, SelectionDAGBuilder emits a LOAD_STACK_GUARD node when it is lowering Intrinsic::stackprotector.

Reimplemented from llvm::TargetLowering.

Definition at line 11070 of file ARMISelLowering.cpp.

References llvm::Triple::getObjectFormat(), llvm::ARMSubtarget::getTargetTriple(), and llvm::Triple::MachO.

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1