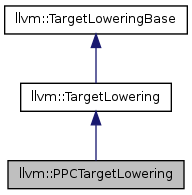

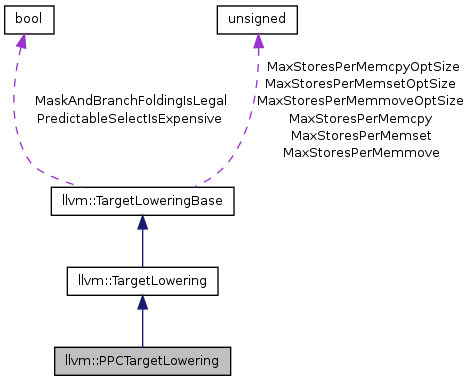

#include <PPCISelLowering.h>

Detailed Description

Definition at line 348 of file PPCISelLowering.h.

Constructor & Destructor Documentation

| PPCTargetLowering::PPCTargetLowering | ( | PPCTargetMachine & | TM | ) | [explicit] |

Definition at line 67 of file PPCISelLowering.cpp.

References llvm::ISD::ADD, llvm::TargetLoweringBase::AddPromotedToType(), llvm::TargetLoweringBase::addRegisterClass(), llvm::ISD::ADJUST_TRAMPOLINE, llvm::ISD::AND, ANDIGlueBug, llvm::ISD::ANY_EXTEND, llvm::ISD::ATOMIC_LOAD, llvm::ISD::ATOMIC_STORE, llvm::ISD::BITCAST, llvm::ISD::BlockAddress, llvm::ISD::BR_CC, llvm::ISD::BR_JT, llvm::ISD::BRCOND, llvm::ISD::BSWAP, llvm::ISD::BUILD_PAIR, llvm::ISD::BUILD_VECTOR, llvm::TargetLoweringBase::computeRegisterProperties(), llvm::ISD::ConstantPool, llvm::RTLIB::COS_PPCF128, llvm::ISD::CTLZ, llvm::ISD::CTLZ_ZERO_UNDEF, llvm::ISD::CTPOP, llvm::ISD::CTTZ, llvm::ISD::CTTZ_ZERO_UNDEF, llvm::TargetLoweringBase::Custom, llvm::PPC::DIR_E500mc, llvm::PPC::DIR_E5500, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::EH_SJLJ_LONGJMP, llvm::ISD::EH_SJLJ_SETJMP, llvm::PPCSubtarget::enableMachineScheduler(), llvm::RTLIB::EXP2_PPCF128, llvm::RTLIB::EXP_PPCF128, llvm::TargetLoweringBase::Expand, llvm::ISD::EXTLOAD, llvm::ISD::EXTRACT_VECTOR_ELT, llvm::MVT::f32, llvm::MVT::f64, llvm::ISD::FABS, llvm::ISD::FCEIL, llvm::ISD::FCOPYSIGN, llvm::ISD::FCOS, llvm::ISD::FDIV, llvm::ISD::FEXP, llvm::ISD::FEXP2, llvm::ISD::FFLOOR, llvm::MVT::FIRST_VECTOR_VALUETYPE, llvm::ISD::FLOG, llvm::ISD::FLOG10, llvm::ISD::FLOG2, llvm::ISD::FLT_ROUNDS_, llvm::ISD::FMA, llvm::ISD::FNEARBYINT, llvm::ISD::FNEG, llvm::ISD::FP_ROUND_INREG, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FPOW, llvm::ISD::FPOWI, llvm::ISD::FREM, llvm::ISD::FRINT, llvm::ISD::FROUND, llvm::ISD::FSIN, llvm::ISD::FSINCOS, llvm::ISD::FSQRT, llvm::ISD::FTRUNC, llvm::PPCSubtarget::getDarwinDirective(), llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::PPCSubtarget::has64BitSupport(), llvm::PPCSubtarget::hasAltivec(), llvm::PPCSubtarget::hasFCPSGN(), llvm::PPCSubtarget::hasFPCVT(), llvm::PPCSubtarget::hasFPRND(), llvm::PPCSubtarget::hasFRE(), llvm::PPCSubtarget::hasFRES(), llvm::PPCSubtarget::hasFRSQRTE(), llvm::PPCSubtarget::hasFRSQRTES(), llvm::PPCSubtarget::hasFSQRT(), llvm::PPCSubtarget::hasLFIWAX(), llvm::PPCSubtarget::hasPOPCNTD(), llvm::PPCSubtarget::hasVSX(), llvm::Sched::Hybrid, llvm::MVT::i1, llvm::MVT::i16, llvm::MVT::i32, llvm::MVT::i64, llvm::MVT::i8, llvm::ISD::INIT_TRAMPOLINE, llvm::ISD::INSERT_VECTOR_ELT, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::PPCSubtarget::isDarwin(), llvm::PPCSubtarget::isPPC64(), llvm::PPCSubtarget::isSVR4ABI(), llvm::ISD::JumpTable, llvm::MVT::LAST_VECTOR_VALUETYPE, llvm::TargetLoweringBase::Legal, llvm::ISD::LOAD, llvm::RTLIB::LOG10_PPCF128, llvm::RTLIB::LOG2_PPCF128, llvm::RTLIB::LOG_PPCF128, llvm::TargetLoweringBase::MaxStoresPerMemcpy, llvm::TargetLoweringBase::MaxStoresPerMemcpyOptSize, llvm::TargetLoweringBase::MaxStoresPerMemmove, llvm::TargetLoweringBase::MaxStoresPerMemmoveOptSize, llvm::TargetLoweringBase::MaxStoresPerMemset, llvm::TargetLoweringBase::MaxStoresPerMemsetOptSize, llvm::ISD::MUL, llvm::ISD::MULHS, llvm::ISD::MULHU, llvm::TargetMachine::Options, llvm::ISD::OR, llvm::MVT::Other, llvm::RTLIB::POW_PPCF128, llvm::MVT::ppcf128, llvm::ISD::PRE_INC, llvm::ISD::PREFETCH, llvm::TargetLoweringBase::Promote, llvm::ISD::READCYCLECOUNTER, llvm::RTLIB::REM_PPCF128, llvm::ISD::ROTR, llvm::ISD::SCALAR_TO_VECTOR, llvm::ISD::SDIV, llvm::ISD::SDIVREM, llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::TargetLoweringBase::setBooleanContents(), llvm::TargetLoweringBase::setBooleanVectorContents(), llvm::ISD::SETCC, llvm::TargetLoweringBase::setCondCodeAction(), llvm::TargetLoweringBase::setExceptionPointerRegister(), llvm::TargetLoweringBase::setExceptionSelectorRegister(), llvm::TargetLoweringBase::setHasMultipleConditionRegisters(), llvm::TargetLoweringBase::setIndexedLoadAction(), llvm::TargetLoweringBase::setIndexedStoreAction(), llvm::TargetLoweringBase::setInsertFencesForAtomic(), llvm::TargetLoweringBase::setLibcallName(), llvm::TargetLoweringBase::setLoadExtAction(), llvm::TargetLoweringBase::setMinFunctionAlignment(), llvm::TargetLoweringBase::setMinStackArgumentAlignment(), llvm::ISD::SETO, llvm::ISD::SETOGE, llvm::ISD::SETOLE, llvm::ISD::SETONE, llvm::TargetLoweringBase::setOperationAction(), llvm::TargetLoweringBase::setPow2SDivIsCheap(), llvm::TargetLoweringBase::setPrefFunctionAlignment(), llvm::TargetLoweringBase::setSchedulingPreference(), llvm::TargetLoweringBase::setStackPointerRegisterToSaveRestore(), llvm::TargetLoweringBase::setTargetDAGCombine(), llvm::TargetLoweringBase::setTruncStoreAction(), llvm::ISD::SETUEQ, llvm::ISD::SETUGT, llvm::ISD::SETULT, llvm::ISD::SETUO, llvm::TargetLoweringBase::setUseUnderscoreLongJmp(), llvm::TargetLoweringBase::setUseUnderscoreSetJmp(), llvm::ISD::SEXTLOAD, llvm::ISD::SHL, llvm::RTLIB::SHL_I128, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND, llvm::ISD::SIGN_EXTEND_INREG, llvm::RTLIB::SIN_PPCF128, llvm::ISD::SINT_TO_FP, llvm::ISD::SMUL_LOHI, llvm::Sched::Source, llvm::RTLIB::SQRT_PPCF128, llvm::ISD::SRA, llvm::RTLIB::SRA_I128, llvm::ISD::SRA_PARTS, llvm::ISD::SREM, llvm::ISD::SRL, llvm::RTLIB::SRL_I128, llvm::ISD::SRL_PARTS, llvm::ISD::STACKRESTORE, llvm::ISD::STACKSAVE, llvm::ISD::STORE, llvm::ISD::SUB, llvm::ISD::TRAP, llvm::ISD::TRUNCATE, llvm::ISD::UDIV, llvm::ISD::UDIVREM, llvm::ISD::UINT_TO_FP, llvm::ISD::UMUL_LOHI, llvm::TargetOptions::UnsafeFPMath, llvm::ISD::UREM, llvm::PPCSubtarget::use64BitRegs(), llvm::PPCSubtarget::useCRBits(), llvm::MVT::v16i8, llvm::MVT::v2f64, llvm::MVT::v2i16, llvm::MVT::v2i32, llvm::MVT::v2i64, llvm::MVT::v2i8, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v8i16, llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VAEND, llvm::ISD::VASTART, llvm::ISD::VECTOR_SHUFFLE, llvm::ISD::VSELECT, llvm::ISD::XOR, llvm::ISD::ZERO_EXTEND, llvm::TargetLoweringBase::ZeroOrNegativeOneBooleanContent, llvm::TargetLoweringBase::ZeroOrOneBooleanContent, and llvm::ISD::ZEXTLOAD.

Member Function Documentation

| bool PPCTargetLowering::allowsMisalignedMemoryAccesses | ( | EVT | VT, |

| unsigned | AddrSpace, | ||

| unsigned | Align = 1, |

||

| bool * | Fast = nullptr |

||

| ) | const [override, virtual] |

Is unaligned memory access allowed for the given type, and is it fast relative to software emulation.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9333 of file PPCISelLowering.cpp.

References DisablePPCUnaligned, llvm::EVT::getSimpleVT(), llvm::PPCSubtarget::hasVSX(), llvm::EVT::isSimple(), llvm::MVT::isVector(), llvm::MVT::ppcf128, llvm::MVT::v2f64, and llvm::MVT::v2i64.

| void PPCTargetLowering::computeKnownBitsForTargetNode | ( | const SDValue | Op, |

| APInt & | KnownZero, | ||

| APInt & | KnownOne, | ||

| const SelectionDAG & | DAG, | ||

| unsigned | Depth = 0 |

||

| ) | const [override, virtual] |

Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

computeKnownBitsForTargetNode - Determine which of the bits specified in Mask are known to be either zero or one and return them in the KnownZero/KnownOne bitsets.

Reimplemented from llvm::TargetLowering.

Definition at line 8815 of file PPCISelLowering.cpp.

References llvm::APInt::getBitWidth(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::MVT::i16, llvm::ISD::INTRINSIC_WO_CHAIN, and llvm::PPCISD::LBRX.

| FastISel * PPCTargetLowering::createFastISel | ( | FunctionLoweringInfo & | FuncInfo, |

| const TargetLibraryInfo * | LibInfo | ||

| ) | const [override, virtual] |

createFastISel - This method returns a target-specific FastISel object, or null if the target does not support "fast" instruction selection.

Reimplemented from llvm::TargetLowering.

Definition at line 9402 of file PPCISelLowering.cpp.

| MachineBasicBlock * PPCTargetLowering::EmitAtomicBinary | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB, | ||

| bool | is64Bit, | ||

| unsigned | BinOpcode | ||

| ) | const |

Definition at line 6537 of file PPCISelLowering.cpp.

References llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineBasicBlock::end(), F(), llvm::MCInstrInfo::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::MachineFunction::insert(), llvm::PPC::PRED_NE, llvm::MachineBasicBlock::splice(), TII, and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

Referenced by EmitInstrWithCustomInserter().

| MachineBasicBlock * PPCTargetLowering::emitEHSjLjLongJmp | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const |

Definition at line 6878 of file PPCISelLowering.cpp.

References llvm::MachineInstrBuilder::addReg(), llvm::BuildMI(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineInstr::eraseFromParent(), llvm::MCInstrInfo::get(), llvm::MachineInstr::getDebugLoc(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::TargetLoweringBase::getPointerTy(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::TargetMachine::getRelocationModel(), llvm::MVT::getStoreSize(), llvm::TargetMachine::getSubtargetImpl(), llvm::MachineFunction::getTarget(), llvm::TargetLoweringBase::getTargetMachine(), llvm::MVT::i64, llvm::PPCSubtarget::isSVR4ABI(), llvm::AArch64DB::LD, llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), llvm::PPCISD::MTCTR, llvm::Reloc::PIC_, llvm::MachineInstrBuilder::setMemRefs(), and TII.

Referenced by EmitInstrWithCustomInserter().

| llvm::MachineBasicBlock * PPCTargetLowering::emitEHSjLjSetJmp | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const |

Definition at line 6729 of file PPCISelLowering.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::MachineInstrBuilder::addRegMask(), llvm::MachineBasicBlock::addSuccessor(), llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), llvm::AttributeSet::FunctionIndex, llvm::MCInstrInfo::get(), llvm::Function::getAttributes(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::MachineFunction::getFunction(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::PPCRegisterInfo::getNoPreservedMask(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::TargetLoweringBase::getPointerTy(), llvm::MachineOperand::getReg(), llvm::MachineRegisterInfo::getRegClass(), llvm::TargetLoweringBase::getRegClassFor(), llvm::MachineFunction::getRegInfo(), llvm::MVT::getStoreSize(), llvm::TargetMachine::getSubtarget(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::AttributeSet::hasAttribute(), llvm::TargetRegisterClass::hasType(), I, llvm::MVT::i64, llvm::MachineFunction::insert(), llvm::PPCSubtarget::isPPC64(), llvm::PPCSubtarget::isSVR4ABI(), LI, llvm::MachineInstr::memoperands_begin(), llvm::MachineInstr::memoperands_end(), llvm::Attribute::Naked, llvm::TargetOpcode::PHI, llvm::MachineInstrBuilder::setMemRefs(), llvm::MachineBasicBlock::splice(), TII, and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

Referenced by EmitInstrWithCustomInserter().

| MachineBasicBlock * PPCTargetLowering::EmitInstrWithCustomInserter | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB | ||

| ) | const [override, virtual] |

This method should be implemented by targets that mark instructions with the 'usesCustomInserter' flag. These instructions are special in various ways, which require special support to insert. The specified MachineInstr is created but not inserted into any basic blocks, and this method is called to expand it into a sequence of instructions, potentially also creating new basic blocks and control flow.

Reimplemented from llvm::TargetLowering.

Definition at line 6984 of file PPCISelLowering.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), AND, llvm::PPCISD::ANDIo_1_EQ_BIT, llvm::PPCISD::ANDIo_1_GT_BIT, llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::TargetOpcode::COPY, llvm::MachineOperand::CreateImm(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineRegisterInfo::createVirtualRegister(), EmitAtomicBinary(), emitEHSjLjLongJmp(), emitEHSjLjSetJmp(), EmitPartwordAtomicBinary(), llvm::MachineBasicBlock::end(), llvm::MachineInstr::eraseFromParent(), F(), llvm::ISD::FADD, llvm::MCInstrInfo::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::MachineOperand::getImm(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOpcode(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::PPCSubtarget::hasISEL(), llvm::MachineFunction::insert(), llvm::TargetInstrInfo::insertSelect(), llvm::PPCSubtarget::isPPC64(), LI, llvm_unreachable, llvm::PPCISD::MFFS, OR, llvm::TargetOpcode::PHI, llvm::PPC::PRED_BIT_SET, llvm::PPC::PRED_NE, llvm::SmallVectorTemplateBase< T, isPodLike< T >::value >::push_back(), llvm::MachineBasicBlock::splice(), TII, llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs(), and XOR.

| MachineBasicBlock * PPCTargetLowering::EmitPartwordAtomicBinary | ( | MachineInstr * | MI, |

| MachineBasicBlock * | MBB, | ||

| bool | is8bit, | ||

| unsigned | Opcode | ||

| ) | const |

Definition at line 6598 of file PPCISelLowering.cpp.

References llvm::MachineInstrBuilder::addImm(), llvm::MachineInstrBuilder::addMBB(), llvm::MachineInstrBuilder::addReg(), llvm::MachineBasicBlock::addSuccessor(), AND, llvm::MachineBasicBlock::begin(), llvm::BuildMI(), llvm::MachineFunction::CreateMachineBasicBlock(), llvm::MachineRegisterInfo::createVirtualRegister(), llvm::MachineBasicBlock::end(), F(), llvm::MCInstrInfo::get(), llvm::MachineBasicBlock::getBasicBlock(), llvm::MachineInstr::getDebugLoc(), llvm::TargetSubtargetInfo::getInstrInfo(), llvm::MachineInstr::getOperand(), llvm::MachineBasicBlock::getParent(), llvm::MachineOperand::getReg(), llvm::MachineFunction::getRegInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::MachineFunction::insert(), llvm::PPCSubtarget::isPPC64(), LI, OR, llvm::PPC::PRED_NE, llvm::MachineBasicBlock::splice(), TII, and llvm::MachineBasicBlock::transferSuccessorsAndUpdatePHIs().

Referenced by EmitInstrWithCustomInserter().

| bool llvm::PPCTargetLowering::functionArgumentNeedsConsecutiveRegisters | ( | Type * | Ty, |

| CallingConv::ID | CallConv, | ||

| bool | isVarArg | ||

| ) | const [inline, override, virtual] |

Returns true if an argument of type Ty needs to be passed in a contiguous block of registers in calling convention CallConv.

Reimplemented from llvm::TargetLowering.

Definition at line 525 of file PPCISelLowering.h.

References llvm::Type::isArrayTy().

| unsigned PPCTargetLowering::getByValTypeAlignment | ( | Type * | Ty | ) | const [override, virtual] |

getByValTypeAlignment - Return the desired alignment for ByVal aggregate function arguments in the caller parameter area. This is the actual alignment, not its logarithm.

getByValTypeAlignment - Return the desired alignment for ByVal aggregate function arguments in the caller parameter area.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 745 of file PPCISelLowering.cpp.

References Align(), getMaxByValAlign(), llvm::PPCSubtarget::hasAltivec(), llvm::PPCSubtarget::hasQPX(), llvm::PPCSubtarget::isDarwin(), and llvm::PPCSubtarget::isPPC64().

| PPCTargetLowering::ConstraintType PPCTargetLowering::getConstraintType | ( | const std::string & | Constraint | ) | const [override, virtual] |

getConstraintType - Given a constraint, return the type of constraint it is for this target.

Reimplemented from llvm::TargetLowering.

Definition at line 8856 of file PPCISelLowering.cpp.

References llvm::TargetLowering::C_Memory, and llvm::TargetLowering::C_RegisterClass.

| EVT PPCTargetLowering::getOptimalMemOpType | ( | uint64_t | Size, |

| unsigned | DstAlign, | ||

| unsigned | SrcAlign, | ||

| bool | IsMemset, | ||

| bool | ZeroMemset, | ||

| bool | MemcpyStrSrc, | ||

| MachineFunction & | MF | ||

| ) | const [override, virtual] |

getOptimalMemOpType - Returns the target specific optimal type for load and store operations as a result of memset, memcpy, and memmove lowering. If DstAlign is zero that means it's safe to destination alignment can satisfy any constraint. Similarly if SrcAlign is zero it means there isn't a need to check it against alignment requirement, probably because the source does not need to be loaded. If 'IsMemset' is true, that means it's expanding a memset. If 'ZeroMemset' is true, that means it's a memset of zero. 'MemcpyStrSrc' indicates whether the memcpy source is constant so it does not need to be loaded. It returns EVT::Other if the type should be determined using generic target-independent logic.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9285 of file PPCISelLowering.cpp.

References llvm::MVT::i64, and llvm::PPCSubtarget::isPPC64().

| bool PPCTargetLowering::getPreIndexedAddressParts | ( | SDNode * | N, |

| SDValue & | Base, | ||

| SDValue & | Offset, | ||

| ISD::MemIndexedMode & | AM, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

getPreIndexedAddressParts - returns true by value, base pointer and offset pointer and addressing mode by reference if the node's address can be legally represented as pre-indexed load / store address.

Reimplemented from llvm::TargetLowering.

Definition at line 1444 of file PPCISelLowering.cpp.

References DisablePPCPreinc, llvm::SDValue::getNode(), llvm::MVT::i32, llvm::MVT::i64, llvm::SDNode::isPredecessorOf(), llvm::EVT::isVector(), llvm::AArch64DB::LD, llvm::ISD::PRE_INC, SelectAddressRegImm(), SelectAddressRegReg(), llvm::ISD::SEXTLOAD, llvm::AArch64DB::ST, and std::swap().

| std::pair< unsigned, const TargetRegisterClass * > PPCTargetLowering::getRegForInlineAsmConstraint | ( | const std::string & | Constraint, |

| MVT | VT | ||

| ) | const [override, virtual] |

Given a physical register constraint (e.g. {edx}), return the register number and the register class for the register.

Given a register class constraint, like 'r', if this corresponds directly to an LLVM register class, return a register of 0 and the register class pointer.

This should only be used for C_Register constraints. On error, this returns a register number of 0 and a null register class pointer..

Reimplemented from llvm::TargetLowering.

Definition at line 8940 of file PPCISelLowering.cpp.

References llvm::MVT::f32, llvm::TargetRegisterInfo::getMatchingSuperReg(), llvm::TargetSubtargetInfo::getRegisterInfo(), llvm::TargetMachine::getSubtargetImpl(), llvm::TargetLoweringBase::getTargetMachine(), llvm::MVT::i64, and llvm::PPCSubtarget::isPPC64().

| unsigned PPCTargetLowering::getRegisterByName | ( | const char * | RegName, |

| EVT | VT | ||

| ) | const [override, virtual] |

Return the register ID of the name passed in. Used by named register global variables extension. There is no target-independent behaviour so the default action is to bail.

Reimplemented from llvm::TargetLowering.

Definition at line 9170 of file PPCISelLowering.cpp.

References llvm::StringSwitch< T, R >::Case(), llvm::StringSwitch< T, R >::Default(), llvm::MVT::i64, llvm::PPCSubtarget::isDarwinABI(), llvm::PPCSubtarget::isPPC64(), and llvm::report_fatal_error().

| MVT llvm::PPCTargetLowering::getScalarShiftAmountTy | ( | EVT | LHSTy | ) | const [inline, override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 358 of file PPCISelLowering.h.

References llvm::MVT::i32.

| Sched::Preference PPCTargetLowering::getSchedulingPreference | ( | SDNode * | ) | const [override, virtual] |

Some scheduler, e.g. hybrid, can switch to different scheduling heuristics for different nodes. This function returns the preference (or none) for the given node.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9393 of file PPCISelLowering.cpp.

References DisableILPPref, llvm::PPCSubtarget::enableMachineScheduler(), llvm::TargetLoweringBase::getSchedulingPreference(), and llvm::Sched::ILP.

| EVT PPCTargetLowering::getSetCCResultType | ( | LLVMContext & | Context, |

| EVT | VT | ||

| ) | const [override, virtual] |

getSetCCResultType - Return the ISD::SETCC ValueType

Reimplemented from llvm::TargetLoweringBase.

Definition at line 823 of file PPCISelLowering.cpp.

References llvm::EVT::changeVectorElementTypeToInteger(), llvm::MVT::i1, llvm::MVT::i32, llvm::EVT::isVector(), and llvm::PPCSubtarget::useCRBits().

Referenced by PerformDAGCombine(), and ReplaceNodeResults().

| TargetLowering::ConstraintWeight PPCTargetLowering::getSingleConstraintMatchWeight | ( | AsmOperandInfo & | info, |

| const char * | constraint | ||

| ) | const [override, virtual] |

Examine constraint string and operand type and determine a weight value. The operand object must already have been set up with the operand type.

Examine constraint type and operand type and determine a weight value. This object must already have been set up with the operand type and the current alternative constraint selected.

Reimplemented from llvm::TargetLowering.

Definition at line 8888 of file PPCISelLowering.cpp.

References llvm::TargetLowering::AsmOperandInfo::CallOperandVal, llvm::TargetLowering::CW_Default, llvm::TargetLowering::CW_Invalid, llvm::TargetLowering::CW_Memory, llvm::TargetLowering::CW_Register, llvm::Value::getType(), llvm::Type::isDoubleTy(), llvm::Type::isFloatTy(), llvm::Type::isIntegerTy(), and llvm::Type::isVectorTy().

| const char * PPCTargetLowering::getTargetNodeName | ( | unsigned | Opcode | ) | const [override, virtual] |

getTargetNodeName() - This method returns the name of a target specific DAG node.

Reimplemented from llvm::TargetLowering.

Definition at line 758 of file PPCISelLowering.cpp.

References llvm::PPCISD::ADD_TLS, llvm::PPCISD::ADDI_DTPREL_L, llvm::PPCISD::ADDI_TLSGD_L, llvm::PPCISD::ADDI_TLSLD_L, llvm::PPCISD::ADDI_TOC_L, llvm::PPCISD::ADDIS_DTPREL_HA, llvm::PPCISD::ADDIS_GOT_TPREL_HA, llvm::PPCISD::ADDIS_TLSGD_HA, llvm::PPCISD::ADDIS_TLSLD_HA, llvm::PPCISD::ADDIS_TOC_HA, llvm::PPCISD::BCTRL, llvm::PPCISD::BDNZ, llvm::PPCISD::BDZ, llvm::PPCISD::CALL, llvm::PPCISD::CALL_NOP, llvm::PPCISD::COND_BRANCH, llvm::PPCISD::CR6SET, llvm::PPCISD::CR6UNSET, llvm::PPCISD::DYNALLOC, llvm::PPCISD::EH_SJLJ_LONGJMP, llvm::PPCISD::EH_SJLJ_SETJMP, llvm::PPCISD::FADDRTZ, llvm::PPCISD::FCFID, llvm::PPCISD::FCTIDZ, llvm::PPCISD::FCTIWZ, llvm::PPCISD::FRE, llvm::PPCISD::FRSQRTE, llvm::PPCISD::FSEL, llvm::PPCISD::GET_TLS_ADDR, llvm::PPCISD::GET_TLSLD_ADDR, llvm::PPCISD::GlobalBaseReg, llvm::PPCISD::Hi, llvm::PPCISD::LARX, llvm::PPCISD::LBRX, llvm::PPCISD::LD_GOT_TPREL_L, llvm::PPCISD::LD_TOC_L, llvm::PPCISD::Lo, llvm::PPCISD::LOAD, llvm::PPCISD::LOAD_TOC, llvm::PPCISD::MFFS, llvm::PPCISD::MFOCRF, llvm::PPCISD::MTCTR, llvm::PPCISD::PPC32_GOT, llvm::PPCISD::RET_FLAG, llvm::PPCISD::SC, llvm::PPCISD::SHL, llvm::PPCISD::SRA, llvm::PPCISD::SRL, llvm::PPCISD::STBRX, llvm::PPCISD::STCX, llvm::PPCISD::STFIWX, llvm::PPCISD::TC_RETURN, llvm::PPCISD::TOC_ENTRY, llvm::PPCISD::VADD_SPLAT, llvm::PPCISD::VCMP, llvm::PPCISD::VCMPo, llvm::PPCISD::VMADDFP, llvm::PPCISD::VNMSUBFP, and llvm::PPCISD::VPERM.

| bool PPCTargetLowering::getTgtMemIntrinsic | ( | IntrinsicInfo & | , |

| const CallInst & | , | ||

| unsigned | |||

| ) | const [override, virtual] |

Given an intrinsic, checks if on the target the intrinsic will need to map to a MemIntrinsicNode (touches memory). If this is the case, it returns true and store the intrinsic information into the IntrinsicInfo that was passed to the function.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9198 of file PPCISelLowering.cpp.

References llvm::TargetLoweringBase::IntrinsicInfo::align, llvm::CallInst::getArgOperand(), llvm::EVT::getStoreSize(), llvm::MVT::i16, llvm::ISD::INTRINSIC_VOID, llvm::ISD::INTRINSIC_W_CHAIN, llvm::TargetLoweringBase::IntrinsicInfo::memVT, llvm::TargetLoweringBase::IntrinsicInfo::offset, llvm::TargetLoweringBase::IntrinsicInfo::opc, llvm::TargetLoweringBase::IntrinsicInfo::ptrVal, llvm::TargetLoweringBase::IntrinsicInfo::readMem, llvm::TargetLoweringBase::IntrinsicInfo::size, llvm::MVT::v4i32, llvm::TargetLoweringBase::IntrinsicInfo::vol, and llvm::TargetLoweringBase::IntrinsicInfo::writeMem.

| bool PPCTargetLowering::isFMAFasterThanFMulAndFAdd | ( | EVT | VT | ) | const [override, virtual] |

isFMAFasterThanFMulAndFAdd - Return true if an FMA operation is faster than a pair of fmul and fadd instructions. fmuladd intrinsics will be expanded to FMAs when this method returns true, otherwise fmuladd is expanded to fmul + fadd.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9367 of file PPCISelLowering.cpp.

References llvm::MVT::f32, llvm::EVT::getScalarType(), llvm::EVT::getSimpleVT(), llvm::EVT::isSimple(), and llvm::MVT::SimpleTy.

| bool PPCTargetLowering::isLegalAddImmediate | ( | int64_t | Imm | ) | const [override, virtual] |

isLegalAddImmediate - Return true if the specified immediate is legal add immediate, that is the target has add instructions which can add a register and the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9329 of file PPCISelLowering.cpp.

References llvm::isInt< 16 >(), and llvm::isUInt< 16 >().

| bool PPCTargetLowering::isLegalAddressingMode | ( | const AddrMode & | AM, |

| Type * | Ty | ||

| ) | const [override, virtual] |

isLegalAddressingMode - Return true if the addressing mode represented by AM is legal for this target, for a load/store of the specified type.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9067 of file PPCISelLowering.cpp.

References llvm::TargetLoweringBase::AddrMode::BaseGV, llvm::TargetLoweringBase::AddrMode::BaseOffs, llvm::TargetLoweringBase::AddrMode::HasBaseReg, and llvm::TargetLoweringBase::AddrMode::Scale.

| bool PPCTargetLowering::isLegalICmpImmediate | ( | int64_t | Imm | ) | const [override, virtual] |

isLegalICmpImmediate - Return true if the specified immediate is legal icmp immediate, that is the target has icmp instructions which can compare a register against the immediate without having to materialize the immediate into a register.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9325 of file PPCISelLowering.cpp.

References llvm::isInt< 16 >(), and llvm::isUInt< 16 >().

| bool PPCTargetLowering::isOffsetFoldingLegal | ( | const GlobalAddressSDNode * | GA | ) | const [override, virtual] |

Return true if folding a constant offset with the given GlobalAddress is legal. It is frequently not legal in PIC relocation models.

Reimplemented from llvm::TargetLowering.

Definition at line 9193 of file PPCISelLowering.cpp.

| bool PPCTargetLowering::isTruncateFree | ( | Type * | Ty1, |

| Type * | Ty2 | ||

| ) | const [override, virtual] |

isTruncateFree - Return true if it's free to truncate a value of type Ty1 to type Ty2. e.g. On PPC it's free to truncate a i64 value in register X1 to i32 by referencing its sub-register R1.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9309 of file PPCISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), and llvm::Type::isIntegerTy().

| bool PPCTargetLowering::isTruncateFree | ( | EVT | VT1, |

| EVT | VT2 | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9317 of file PPCISelLowering.cpp.

References llvm::EVT::getSizeInBits(), and llvm::EVT::isInteger().

| void PPCTargetLowering::LowerAsmOperandForConstraint | ( | SDValue | Op, |

| std::string & | Constraint, | ||

| std::vector< SDValue > & | Ops, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerAsmOperandForConstraint - Lower the specified operand into the Ops vector. If it is invalid, don't add anything to Ops.

Reimplemented from llvm::TargetLowering.

Definition at line 8997 of file PPCISelLowering.cpp.

References llvm::dyn_cast(), llvm::SDValue::getNode(), llvm::SelectionDAG::getTargetConstant(), llvm::SDValue::getValueType(), llvm::ConstantSDNode::getZExtValue(), llvm::isPowerOf2_32(), and llvm_unreachable.

| SDValue PPCTargetLowering::LowerOperation | ( | SDValue | Op, |

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

LowerOperation - Provide custom lowering hooks for some operations.

Reimplemented from llvm::TargetLowering.

Definition at line 6404 of file PPCISelLowering.cpp.

References llvm::ISD::ADJUST_TRAMPOLINE, llvm::ISD::BlockAddress, llvm::ISD::BUILD_VECTOR, llvm::ISD::ConstantPool, llvm::ISD::DYNAMIC_STACKALLOC, llvm::ISD::EH_SJLJ_LONGJMP, llvm::ISD::EH_SJLJ_SETJMP, llvm::ISD::FLT_ROUNDS_, llvm::ISD::FP_TO_SINT, llvm::ISD::FP_TO_UINT, llvm::ISD::FRAMEADDR, llvm::SDValue::getOpcode(), llvm::ISD::GlobalAddress, llvm::ISD::GlobalTLSAddress, llvm::ISD::INIT_TRAMPOLINE, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::ISD::JumpTable, llvm_unreachable, llvm::ISD::LOAD, llvm::ISD::MUL, llvm::ISD::RETURNADDR, llvm::ISD::SCALAR_TO_VECTOR, llvm::ISD::SELECT_CC, llvm::ISD::SETCC, llvm::ISD::SHL_PARTS, llvm::ISD::SIGN_EXTEND_INREG, llvm::ISD::SINT_TO_FP, llvm::ISD::SRA_PARTS, llvm::ISD::SRL_PARTS, llvm::ISD::STACKRESTORE, llvm::ISD::STORE, llvm::ISD::TRUNCATE, llvm::ISD::UINT_TO_FP, llvm::ISD::VAARG, llvm::ISD::VACOPY, llvm::ISD::VASTART, and llvm::ISD::VECTOR_SHUFFLE.

| SDValue PPCTargetLowering::PerformDAGCombine | ( | SDNode * | N, |

| DAGCombinerInfo & | DCI | ||

| ) | const [override, virtual] |

This method will be invoked for all target nodes and for any target-independent nodes that the target has registered with invoke it for.

The semantics are as follows: Return Value: SDValue.Val == 0 - No change was made SDValue.Val == N - N was replaced, is dead, and is already handled. otherwise - N should be replaced by the returned Operand.

In addition, methods provided by DAGCombinerInfo may be used to perform more complex transformations.

Reimplemented from llvm::TargetLowering.

Definition at line 8249 of file PPCISelLowering.cpp.

References llvm::ISD::ADD, ADD, llvm::TargetLowering::DAGCombinerInfo::AddToWorklist(), llvm::ISD::AND, llvm::ISD::ANY_EXTEND, llvm::PPCISD::BDNZ, llvm::PPCISD::BDZ, llvm::ISD::BITCAST, llvm::ISD::BR, llvm::ISD::BR_CC, llvm::ISD::BRCOND, llvm::ISD::BSWAP, llvm::ISD::BUILD_VECTOR, BuildIntrinsicOp(), llvm::TargetLowering::DAGCombinerInfo::CombineTo(), llvm::PPCISD::COND_BRANCH, llvm::TargetLowering::DAGCombinerInfo::DAG, llvm::MVT::f32, llvm::PPCISD::FCFID, llvm::PPCISD::FCTIDZ, llvm::PPCISD::FCTIWZ, llvm::ISD::FDIV, findConsecutiveLoad(), llvm::ISD::FMUL, llvm::ISD::FP_EXTEND, llvm::ISD::FP_ROUND, llvm::ISD::FP_TO_SINT, llvm::ISD::FSQRT, llvm::DataLayout::getABITypeAlignment(), llvm::MemSDNode::getAlignment(), llvm::APInt::getAllOnesValue(), getAltivecCompareInfo(), llvm::LoadSDNode::getBasePtr(), llvm::MemSDNode::getChain(), llvm::SelectionDAG::getConstant(), llvm::SelectionDAG::getConstantFP(), llvm::SelectionDAG::getContext(), llvm::TargetLoweringBase::getDataLayout(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getMachineFunction(), llvm::MachineFunction::getMachineMemOperand(), llvm::SelectionDAG::getMemIntrinsicNode(), llvm::MemSDNode::getMemOperand(), llvm::MemSDNode::getMemoryVT(), llvm::SDValue::getNode(), llvm::SelectionDAG::getNode(), llvm::SDValue::getOpcode(), llvm::SDNode::getOpcode(), llvm::SDValue::getOperand(), llvm::SDNode::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::EVT::getScalarType(), llvm::SelectionDAG::getSetCC(), getSetCCResultType(), llvm::EVT::getSizeInBits(), llvm::EVT::getStoreSize(), llvm::TargetMachine::getSubtarget(), llvm::SelectionDAG::getTargetConstant(), llvm::TargetLoweringBase::getTargetMachine(), llvm::EVT::getTypeForEVT(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SelectionDAG::getValueType(), llvm::SDNode::getValueType(), llvm::EVT::getVectorNumElements(), llvm::SelectionDAG::getVTList(), llvm::MVT::Glue, llvm::PPCSubtarget::has64BitSupport(), llvm::SDNode::hasNUsesOfValue(), llvm::SDValue::hasOneUse(), llvm::SDNode::hasOneUse(), llvm::PPCSubtarget::hasSTFIWX(), llvm::MVT::i16, llvm::MVT::i64, llvm::ISD::INTRINSIC_W_CHAIN, llvm::ISD::INTRINSIC_WO_CHAIN, llvm::PPCSubtarget::isLittleEndian(), llvm::ISD::isNON_EXTLoad(), llvm::EVT::isVector(), isZero(), llvm::PPCISD::LBRX, llvm::SPII::Load, llvm::ISD::LOAD, llvm::SelectionDAG::MaskedValueIsZero(), llvm::PPCISD::MFOCRF, llvm::TargetMachine::Options, llvm::MVT::Other, llvm::MVT::ppcf128, llvm::PPC::PRED_EQ, llvm::PPC::PRED_GE, llvm::PPC::PRED_LT, llvm::PPC::PRED_NE, llvm::SelectionDAG::ReplaceAllUsesOfValueWith(), llvm::ISD::SELECT, llvm::ISD::SELECT_CC, llvm::ISD::SETCC, llvm::ISD::SETEQ, llvm::ISD::SETNE, llvm::PPCISD::SHL, llvm::ISD::SIGN_EXTEND, llvm::ISD::SINT_TO_FP, llvm::PPCISD::SRA, llvm::PPCISD::SRL, llvm::PPCISD::STBRX, llvm::PPCISD::STFIWX, llvm::ISD::STORE, llvm::ISD::TokenFactor, llvm::ISD::TRUNCATE, llvm::TargetOptions::UnsafeFPMath, llvm::SDNode::use_begin(), llvm::SDNode::use_end(), llvm::MVT::v16i8, llvm::MVT::v4f32, llvm::MVT::v4i32, llvm::MVT::v8i16, llvm::PPCISD::VCMP, llvm::PPCISD::VCMPo, llvm::ISD::VSELECT, llvm::ISD::ZERO_EXTEND, and llvm::APInt::zext().

| void PPCTargetLowering::ReplaceNodeResults | ( | SDNode * | N, |

| SmallVectorImpl< SDValue > & | Results, | ||

| SelectionDAG & | DAG | ||

| ) | const [override, virtual] |

ReplaceNodeResults - Replace the results of node with an illegal result type with new values built out of custom code.

Reimplemented from llvm::TargetLowering.

Definition at line 6464 of file PPCISelLowering.cpp.

References llvm::ISD::BUILD_PAIR, llvm::ISD::EXTRACT_ELEMENT, llvm::PPCISD::FADDRTZ, llvm::ISD::FP_ROUND_INREG, llvm::ISD::FP_TO_SINT, llvm::SelectionDAG::getContext(), llvm::SelectionDAG::getIntPtrConstant(), llvm::SelectionDAG::getNode(), llvm::SDNode::getOpcode(), llvm::SDNode::getOperand(), getSetCCResultType(), llvm::TargetMachine::getSubtarget(), llvm::TargetLoweringBase::getTargetMachine(), llvm::SDValue::getValue(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::SelectionDAG::getVTList(), llvm::MVT::i1, llvm::MVT::i64, llvm::ISD::INTRINSIC_W_CHAIN, llvm::PPCSubtarget::isSVR4ABI(), llvm_unreachable, llvm::MVT::Other, llvm::MVT::ppcf128, llvm::SmallVectorTemplateBase< T, isPodLike >::push_back(), and llvm::ISD::VAARG.

| bool PPCTargetLowering::SelectAddressRegImm | ( | SDValue | N, |

| SDValue & | Disp, | ||

| SDValue & | Base, | ||

| SelectionDAG & | DAG, | ||

| bool | Aligned | ||

| ) | const |

SelectAddressRegImm - Returns true if the address N can be represented by a base register plus a signed 16-bit displacement [r+imm], and if it is not better represented as reg+reg. If Aligned is true, only accept displacements suitable for STD and friends, i.e. multiples of 4.

Returns true if the address N can be represented by a base register plus a signed 16-bit displacement [r+imm], and if it is not better represented as reg+reg. If Aligned is true, only accept displacements suitable for STD and friends, i.e. multiples of 4.

Definition at line 1318 of file PPCISelLowering.cpp.

References ADD, llvm::SelectionDAG::computeKnownBits(), fixupFuncForFI(), llvm::SelectionDAG::getMachineNode(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::TargetLoweringBase::getPointerTy(), llvm::SelectionDAG::getRegister(), llvm::SelectionDAG::getTargetConstant(), llvm::SelectionDAG::getTargetFrameIndex(), llvm::SDValue::getValueType(), llvm::SDNode::getValueType(), llvm::APInt::getZExtValue(), llvm::MVT::i32, isIntS16Immediate(), llvm::PPCSubtarget::isPPC64(), llvm::HexagonISD::Lo, OR, SelectAddressRegReg(), llvm::ISD::TargetConstantPool, llvm::ISD::TargetGlobalAddress, llvm::ISD::TargetGlobalTLSAddress, and llvm::ISD::TargetJumpTable.

Referenced by getPreIndexedAddressParts().

| bool PPCTargetLowering::SelectAddressRegReg | ( | SDValue | N, |

| SDValue & | Base, | ||

| SDValue & | Index, | ||

| SelectionDAG & | DAG | ||

| ) | const |

SelectAddressRegReg - Given the specified addressed, check to see if it can be represented as an indexed [r+r] operation. Returns false if it can be more efficiently represented with [r+imm].

Definition at line 1233 of file PPCISelLowering.cpp.

References ADD, llvm::SelectionDAG::computeKnownBits(), llvm::APInt::getBoolValue(), llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), isIntS16Immediate(), llvm::HexagonISD::Lo, and OR.

Referenced by getPreIndexedAddressParts(), SelectAddressRegImm(), and SelectAddressRegRegOnly().

| bool PPCTargetLowering::SelectAddressRegRegOnly | ( | SDValue | N, |

| SDValue & | Base, | ||

| SDValue & | Index, | ||

| SelectionDAG & | DAG | ||

| ) | const |

SelectAddressRegRegOnly - Given the specified addressed, force it to be represented as an indexed [r+r] operation.

Definition at line 1416 of file PPCISelLowering.cpp.

References ADD, llvm::SDValue::getOpcode(), llvm::SDValue::getOperand(), llvm::SelectionDAG::getRegister(), llvm::SDValue::getValueType(), llvm::PPCSubtarget::isPPC64(), and SelectAddressRegReg().

| bool PPCTargetLowering::shouldConvertConstantLoadToIntImm | ( | const APInt & | Imm, |

| Type * | Ty | ||

| ) | const [override, virtual] |

Returns true if it is beneficial to convert a load of a constant to just the constant itself.

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9299 of file PPCISelLowering.cpp.

References llvm::Type::getPrimitiveSizeInBits(), and llvm::Type::isIntegerTy().

| bool PPCTargetLowering::shouldExpandBuildVectorWithShuffles | ( | EVT | VT, |

| unsigned | DefinedValues | ||

| ) | const [override, virtual] |

Reimplemented from llvm::TargetLoweringBase.

Definition at line 9385 of file PPCISelLowering.cpp.

References llvm::MVT::v2i64.

The documentation for this class was generated from the following files:

1.7.6.1

1.7.6.1